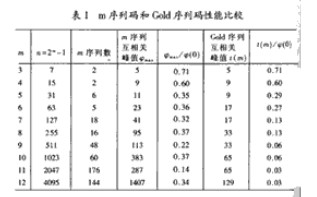

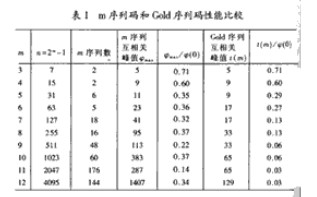

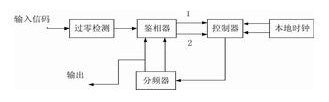

本文介绍一种基于现场可编程门阵列(FPGA)的通信系统同步提取方案的实现。本文只介绍了M序列码作为同步头的实现方案,对于m序列码作为同步头的实现,只要稍微做一下修改,即加一些相应的延时单元就可以实现。

2013-04-11 10:53:23 5696

5696

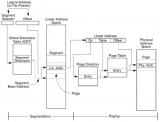

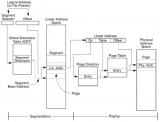

的数据可能不在内存中。 Linux内核地址映射模型 x86 CPU采用了段页式地址映射模型。进程代码中的地址为逻辑地址,经过段页式地址映射后,才真正访问物理内存。 段页式机制如下图。 linux内核地址空间划分 通常32位Linux内核地址空间划分0~3G为用户空

2018-05-08 10:33:19 3776

3776

大家好,51单片机 位地址 单元地址 字节地址?我对着三个概念比较模糊,有懂的朋友请讲,越详细越好。

2013-08-09 11:15:41

如何获知写数据所在的地址和数据长度?有没有寄存器可供查询?是否必须自定义一个寄存器,用来存储地址和长度,当发送完毕后,dsp读该寄存器,然后进行操作?问题3:以下流程是否正确?为提高带宽?是否需要完善?1

2019-01-09 10:58:04

FPGA已经在I/O路径中加入了可编程的硬件模块。这些模块很容易使设计人员在FPGA中实现逻辑功能。为支持更高的数据率, LatticeECP2M器件中的SERDES模块进一步在硬件中实现一些高速协议功能。而FPGA内的结构则用来实现更高层的数据处理功能。

2018-11-26 11:17:24

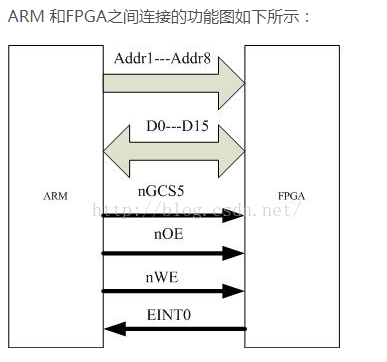

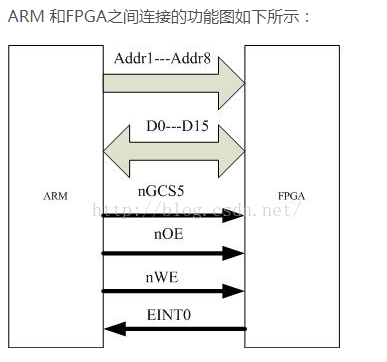

1 前言现场可编程逻辑器件(FPGA)在高速采集系统中的应用越来越广,由于FPGA对采集到的数据的处理能力比较差,故需要将其采集到的数据送到其他CPU系统来实现数据的处理功能,这就使FPGA系统与其

2011-11-24 16:10:01

功能框图。它内部分为两条,每条 1M 字节,数据宽度为 8 位,故存储总容量为 2M 字节。所有输入和输出操作都是在时钟 CLK 上升沿的作用下进行的,刷新时钟交替刷新内部的两条 RAM

2020-04-23 08:00:00

文章目录一、地址映射和寄存器映射原理1.地址映射2.寄存器映射二、GPIO端口的初始化三、实现LED灯参考文献一、地址映射和寄存器映射原理首先要清楚的一点,所有操作,最终目的都是操作寄存器1.地址

2022-03-02 06:36:34

ARM跟FPGA通信,要采用8位地址总线、8位数据总线、读写控制线,怎么实现,地址总线是要映射到FPGA的内部还是直接ARM的内存空间?最好有ARM端简单的C程序描述下,谢谢。

2022-11-22 14:58:26

51单片机串口不同寻常的特征是包括第9位方式(在串口模式2和模式3下)。它允许把在串行口通信增加的第9位用于标志特殊字节的接收。一般约定第9位为高时表示该字节为地址字节,第9位为低时为数据字节。

2020-03-16 07:15:29

为了能直接操作 ODR 的某个 Bit 位,在内核中开辟了一块地址区域(位带别名):可将 ODR这类 Bit 位(位带区)映射到位带别名区域对应的地址,只需操作映射后的地址,就可实现操作 ODR1 位

2025-11-18 07:03:05

mode读取数据(按照datasheet33页的介绍做的),发现数据字节数不对,后用示波器测量此时DRDYB管脚变成200Hz方波了;

3、使用的配置DRDYB_SRC_REG(地址0x27)的值是0x08, CH_CNFG_REG(地址0x2F)值是0x70。

不知道是哪里出了问题,还请各位帮忙解答下,谢谢。

2025-01-13 08:32:48

;amp;quot;memset/memcpy"函数。FPGA连接到ARM的GPMC总线CS1的起始地址为0x1000000,GPMC数据线位宽为16bit,数据线地址线复用

2018-05-16 14:28:40

本文档描述了ARM用于A级系统的地址映射,来自模型和模拟器到开发板和复杂的SoC。

它解释了存储器、外围设备和扩展的地址分区选择空间。

它描述了当32位平台操作系统使用36位或40位地址空间,以及32位总线主控器和外围设备。

它将存储器映射扩展到未来64位ARM系统的48位地址空间,

2023-08-02 08:19:29

有哪位大神知道AT24CXX的器件地址和数据地址是怎么确定的

2016-10-24 20:21:34

你好!设置 RB_ROM_CODE_OFS 位时的闪存地址映射是什么?CodeFlash 向下移动了 0x8000 字节,但 DataFlash 寻址是否以相同的方式移动(即变为

2022-08-30 07:31:04

期望的是,NDEF 消息是外部类型,ID = 0x06,长度为 1 和 3 个数据字节(0x12、0x34、0x56)我得到的是一个类型为外部 (OK) 和 3 个数据字节 0x12、0x00

2023-01-31 08:46:57

。7、32为源IP,目的IP,十六进制表示。8、选项和数据表示IP层之上的数据包。UDP报文1、16位UDP长度,表示整个UDP包字节数。2、16为校验和,伪头部( 4byte源IP地址

2014-03-25 12:46:56

目录1:前言2:地址(门牌号)3:STM32地址映射4:位带操作原理5:位操作代码实现1:前言 以前学51的时候,没有注重地址的这个概念,因为51寄存器少,一个reg52.h里面涵盖了你要用到的所有

2021-08-13 06:05:28

这里写目录标题STM32(CM3内核) 内存映射一.CM3内核简介二.CM3内核地址映射三.搭建代码,实现映射STM32(CM3内核) 内存映射一.CM3内核简介《CM3权威指南》摘抄一段简介

2022-02-11 07:48:56

:地址和数据的各个字节首先通过LSB传输。命令字节、地址字节和数据字节的8位CRC由bq2024计算并由主机读回,以确认接收到正确的命令字、起始地址和数据字节。 如果主机读取的CRC不正确,则必须

2020-07-06 09:18:02

hyperLink_cfg.address_map.rx_priv_id_sel = RX_PRIVID_SEL_ADDR_31_28; //接收端接收到数据后高四位为特权ID

2018-12-28 11:09:22

段长度随功能码变化,典型结构包含:

寄存器地址:2字节,指定操作目标(如读取从40001开始的寄存器)

数据长度:2字节,定义读取/写入的寄存器数量

写入值:根据功能码不同,可为1位线圈值或16位寄存器值

2025-11-17 08:15:29

和常量数据,全局变量数据以及运行时动态申请内存所分配的实际物理内存存放位置。MMU采用页表(page table)来实现虚实地址转换,页表项除了描述虚拟页到物理页直接的转换外,还提供了页的访问权限(读

2020-11-03 16:20:06

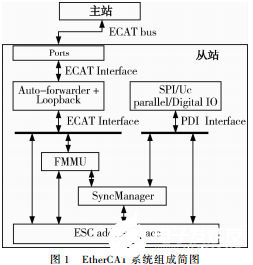

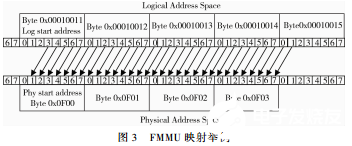

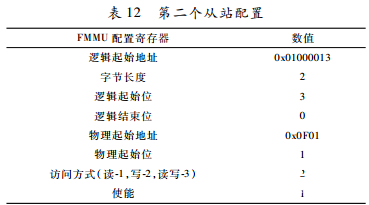

三、EtherCAT 主站 SOEM 源码解析----IOmapSOEM 通过函数 ec_config_map(&IOmap)完成逻辑地址和物理地址的映射,应用程序需要定义一个数

2023-04-20 14:35:51

在STM32中,RAM、CODE、寄存器等都共用一个32位的地址总线32位线性地址空间总容量为4GB,数据字节以小端形式存放在存储器中。一个字里的最低字节被认为是该字的最低有效字节。以0x4000

2021-08-19 06:38:58

的半导体电路具现的,具体的实现的方式我们现在不管。存储单位一般是字节。这样,每个字节的存储单元对应一个地址,当一个合法地址从存储器的地址总线输入后,该地址对应的存储单元上存储的数据就会出现在数据总线上面。图

2022-05-23 15:03:37

我知道可以与Thingspeak 通信,但是是否可以将数据字符串发送到另一个网站(在我的项目中是端口 4600)正在等待 38 字节的数据字符串?收到此字符串后,服务器将向同一 IP 地址发回一条短消息。目前这可能吗?我应该使用 wget 命令吗?

2023-04-26 08:41:37

),它与SPI IP core define的寄存器映射不匹配(见图3)。另外,当主端口(Avalon MM)的数据宽度为8位时,无论SPI如何设置数据位宽,QSYS自动分配的字节数为8个字节。当主端口

2018-06-19 14:26:57

通过编程来改变内部结构的芯片。FPGA 功能实现:需要通过编程即设计硬件描述语言,经过 EDA 工具编译、

2022-01-25 06:45:52

192.168.1.254。FPGA将接收的数据在发回PC端,实现回环。其中TCP server和TCP client模块需要先建立连接,之后才能发送数据。测试结果如下图所示,可见以太网功能正确实现。

四、总结

2025-10-30 07:45:31

中的从 FIFO 2 位异步示例,我们在发送二进制文件时遇到了一个问题。

文件详细信息:

二进制文件包含从地址 0x1400 到 0x27FF 的数据。

文件大小为 10240 字节。

问题: 在

2025-05-21 07:31:00

1MB大小的空间,所以全映射时,条目总数(全映射时页表所占内存空间)=4GB / 1MB =4096条(每条32位,即4字节,共 4 KB)。其中,所谓的每个条目大小为1MB,意思是,CPU发出的一段

2016-12-08 09:37:55

描述SBC-85 8085总线监视器,单步,二进制和十六进制显示,断点缺少在线仿真器,总线监视器是最强大的诊断工具之一。总线监视器提供以下功能:地址和数据字节的二进制和十六进制显示所有 8085

2022-08-22 06:27:43

由RS232接口接收十六进制数据字符串如下:FF80 8080 0080 FF80 8080 20A0.................每组数据如上两组数据格式相同,请问如何提取最后一组数据,即将最后一组FFxx xxxx xxxx分别提取出来,并变为十进制数值输出。。。。。。。。。。。。。。。。

2014-07-23 11:32:06

的研究中大多进行仿真实验,无法保证硬件实际输出PN序列的产生及其性能的测试。为此,基于FPGA技术,利用Logistic混沌映射作为随机信号源对实现PN序列的硬件进行了深入研究,提取Logistic数值

2019-07-05 07:33:06

的数据传输。该设计主要采用硬件描述语言VerilogHDL在可编程逻辑器件FPGA上实现,由于数据采集功能模块繁多,而Wishbone总线可以与任何类型的ROM或RAM相连,因此需在SDX总线与数据采集模块

2019-05-31 05:00:07

、QDR_SA、QDR_BW_n 和 QDR_D)的布线长度必须完全匹配,以将控制、地址及数据线接至具备充足建立与保持余量的存储器器件。物理接口的实现可确保这些信号在离开 FPGA 器件输出时与QDR_K

2019-04-22 07:00:07

在串口的应用中,9位数据格式保含着8位的数据字节及1位的奇偶校验位。另外在RS485应用中利用奇偶校验位指出这是数据字节还是地址字节。在初始化串口之后,如下表所示,依照奇偶校验位的电平,设定

2023-06-15 10:17:54

与FPGA上实现的总线接口基础设施保持一致。双QSPI配置接口为减少FPGA配置时间,许多现代FPGA允许将配置位流分区至两个QSPI器件(图3)。这两个QSPI器件以并行方式连接,其中位流的低半字节

2021-05-26 07:00:00

CPU的按字节寻址和按字寻址的范围分别是多少?如何去计算CPU的地址线和数据线?

2021-10-09 08:08:39

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。那么该如何在低端FPGA中实现DPA的功能呢?

2021-04-08 06:47:08

我创建了具有正常优先级的单个任务。该任务具有三个功能。在一个函数中,我将 2 字节数据写入内部 SRAM(例如 0x20010204 的起始地址)。2 字节数据分别写入内存地址 0x20010204

2022-12-27 08:18:13

,已知一次数据传输为一个字节,既八位二进制的数据,传输一个字节数据即可实现功能。故定义其高四位作为从机地址,低四位作为数据位。RS485通信#include "reg52.h" typedef unsigned int u16; //对数据类型进行声

2021-12-02 07:21:31

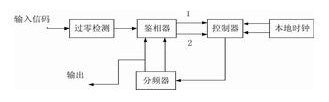

本文主要研究了一种基于FPGA、自顶向下、模块化、用于提取位同步时钟的全数字锁相环设计方法。

2021-05-06 08:00:46

一个4GB的线性地址空间。数据字节以小端模式存放在存储器中。地址空间分8块,每块512MB。注: 小端模式:与大端模式相对应,将数据的低字节保存在内存的低地址中,高字节保存在高地址中。其中: ...

2021-12-09 07:51:09

9中的流程图说明主机发出Write Status命令55h,然后是地址低字节,然后是地址高字节,最后是要编程的数据字节。注意地址和数据的各个字节首先通过LSB传输。命令字节、地址字节和数据字节的16位

2020-09-14 17:36:04

映射以及SRAM存取,DMA模式控制;OBCI3接口控制;线路端编解码功能。图1 网关接口板功能结构图设计描述FPGA的主要功能模块如图2所示。处于框图上端的部分主要是数据流处理部分,主要完成数据

2019-04-23 07:00:08

高电平,发送完成把TXENABLE

管脚置为低电平,这样就ok?

(3)AD9779A的SPI接口: 当使用单字节传输的时候,指令字节和数据字节之间是否可以把CSB管脚拉高?

谢谢!

2023-12-20 07:12:27

STM8 UART发送器根据M位的状态发送8位或9位的数据字

2020-11-11 06:35:06

图一是“接收内容”创建字符串类的属性-显示样式(因为十六进制显示才能正常接收,否则乱码),图二是modbus rtu 协议的数据传输,图三是我接收的传感器传输的其中一组数据,请问如何实现数据位的提取?谢谢

2019-03-30 15:07:31

在串口的应用中,9位数据格式保含着8位的数据字节及1位的奇偶校验位。另外在RS485应用中利用奇偶校验位指出这是数据字节还是地址字节。在初始化串口之后,如下表所示,依照奇偶校验位的电平,设定

2023-06-20 08:07:09

通过51单片机写数据到SD卡后如何统计写入的数据字节的大小

2020-04-18 01:03:56

控制FPGA实现的逻辑控制功能包括与上位机软件iMPACT和串口工具通信、烧写Flash以及配置FPGA器件。基于模块化的设计思想将具体功能分解成多个模块,如图3所示,数据与地址通道上的下标为其通道宽度

2019-05-30 05:00:05

对齐、多通道对齐)是必须的 。字节对齐:设计确定在数据流的哪里是10位数据字节的开始和结束。在FPGA结构中使用有限状态机(FSM)来完成这一任务。把数据流的第一个和第二个 10位组合在一起,形成一个

2019-06-06 05:00:34

和常量数据,全局变量数据以及运行时动态申请内存所分配的实际物理内存存放位置。MMU采用页表(page table)来实现虚实地址转换,页表项除了描述虚拟页到物理页直接的转换外,还提供了页的访问权限(读

2020-11-19 10:52:17

针对报文解析过程中存在的数据存储无序、查询和调用不便等问题,提出应用XML 数据字典进行数据存储的方案。根据给定的数据表,设计XML 形式的数据字典。实现XML 字典数据的解

2009-03-28 09:38:52 36

36 ARM启动代码及地址映射

2010-02-11 11:00:27 104

104 基于FPGA的提取位同步时钟DPLL设计

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发

2010-01-25 09:36:18 3699

3699

基于fpga的锁相环位同步提取电路

该电路如图所示,它由双相高频时钟

2010-10-08 12:00:23 1743

1743

介绍 AES 中的字节替换算法原理并阐述基于FPGA的设计和实现。为了提高系统工作速度,在设计中应用了流水线技术。最后利用MAXPLUS-II开发工具给出仿真结果,并分析了系统工作速度。

2011-09-27 15:54:04 6641

6641

位同步提取实验的实验报告,位同步提取实验的实验报告,位同步提取实验的实验报告

2016-05-26 10:58:41 0

0 现场可编程逻辑门阵列(FPGA)应用于图像处理时,需要对数据中的图像信息进行准确的提取。设计中,FPGA中解压缩功能需要对压缩数据中的图像信息进行提取。根据压缩格式,设计了一种基于状态机的图像

2017-11-17 06:04:02 2595

2595

原文链接:freescale 16位单片机的地址映射--(1)前言 freescale 16位单片机的地址映射--(2)飞思卡尔16位单片机的资源配置 freescale16位单片机的地址映射

2017-11-24 07:43:33 1402

1402 本文将详细地讨论简化UART功能在FPGA中的实现方法。简单回顾一下异步串行通信的数据格式。图2表明在异步传送中串行发送一个数据字节的位定时关系(图中没有包括奇偶校验位)。发送一个完整的字节信息

2018-04-04 12:45:00 28418

28418

众多领域。在图像检测系统中,应具备一个高速的子图像提取和输出模块,本文采用FPGA 器件EP3C25F256C8 和CCD 线阵图像传感器RL1024P,实现线阵CCD 图像检测系统中的子图像提取和输出功能。

2019-04-29 08:22:00 3526

3526

一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。本文给出了一种基于fpga的数字锁相环位同步提取电路。

2019-04-19 08:24:00 4278

4278

视频中展示了各种连接至FPGA开发系统并受其控制的MEMS传感器和数据转换器件。Avnet Xilinx Spartan®-6 FPGA LX9 MicroBoard、Digilent Pmods™和Arrow Altera Cyclone IV BeMicro SDK。

2019-07-05 06:00:00 2652

2652 我们可以把存储器看成一个具有输出和输入口的黑盒子。如下图所示,输入量是地址,输出的是对应地址上存储的数据。当然这个黑盒子是由很复杂的半导体电路具现的,具体的实现的方式我们现在不管。存储单位一般是字节

2019-08-16 17:31:00 0

0 MCS-51单片机的内部数据存储器(RAM)共有128个字节,地址为00H~7FH 。其中的20H~2FH单元是可作为可位寻址的一个区域,共128位,用位地址00H~7FH与之对应。例如:位7FH

2019-07-25 17:36:00 0

0 2、 主机先发送一帧地址信息,其中8位地址,第9为为地址/数据信息的标志位,该位置1表示该帧为地址信息。

2020-04-05 11:42:00 6607

6607

从CPU的总体结构到局部功能的实现采用了自顶向下的设计方法和模块化的设计思想,利用Xilinx 公司的Spartan II 系列FPGA,设计实现了八位CPU软核。在FPGA内部不仅实现了CPU必需

2020-08-03 17:58:56 13

13 从CPU的总体结构到局部功能的实现采用了自顶向下的设计方法和模块化的设计思想, 利用Xilinx 公司的Spartan II 系列FPGA, 设计实现了八位CPU软核。在FPGA 内部不仅实现了

2020-08-19 17:43:19 7

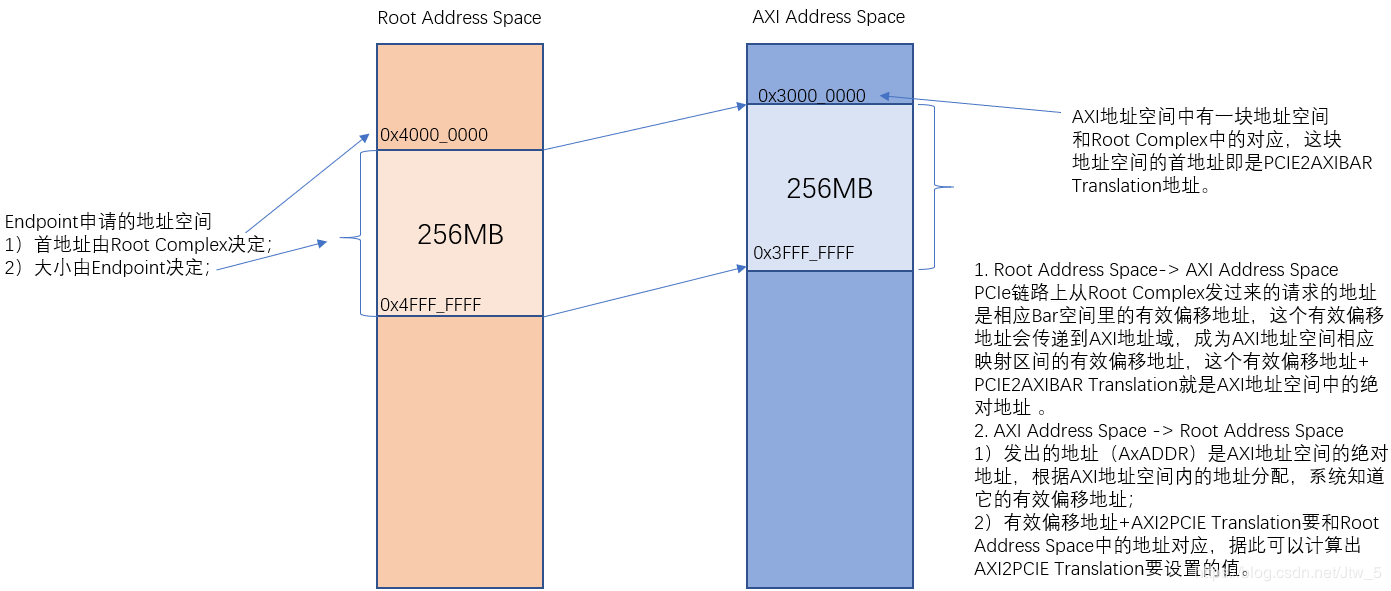

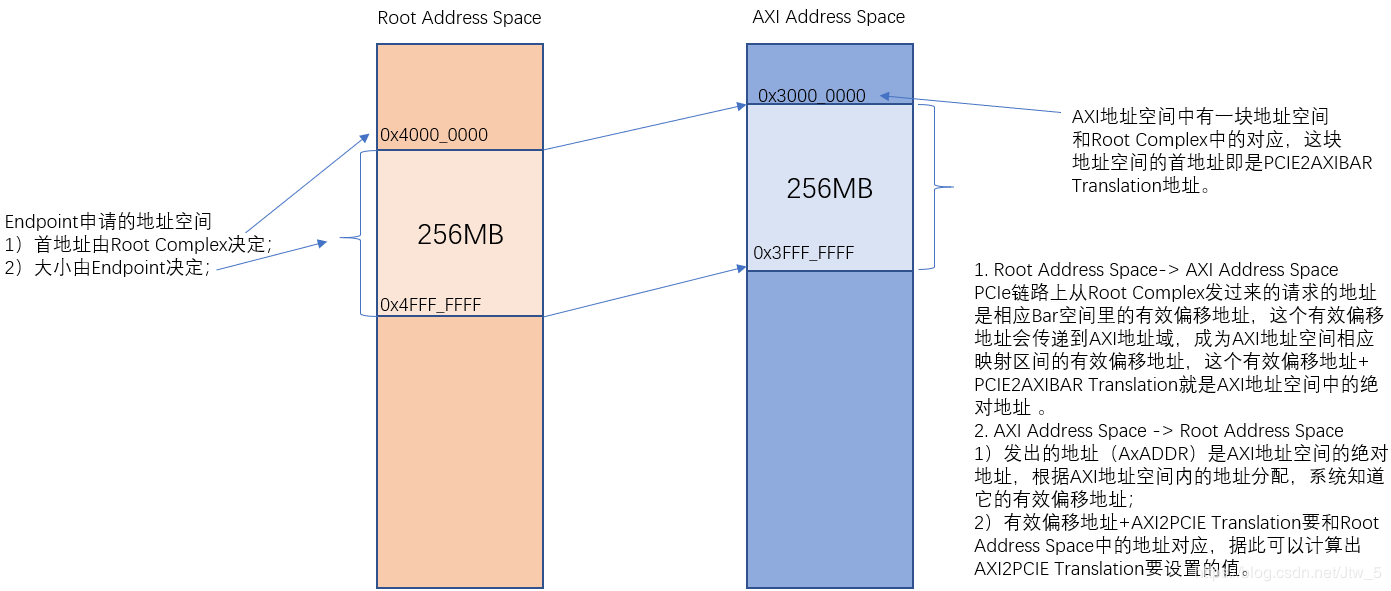

7 (Root Complex中的系统地址空间)到AXI域(FPGA逻辑中的AXI地址空间)。PCIe发起的对Endpoint的访问应在Endpoint申请的BAR空间内,Endpoint申请BAR空间

2020-11-20 15:28:52 8159

8159

到局域网络上的所有主机,并接收返回消息,以此确定目标的物理地址;收到返回消息后将该IP地址和物理地址存入本机ARP缓存中并保留一定时间,下次请求时直接查询ARP缓存以节约资源。地址 ARP映射方式 静态映射 静态映射的意思是要手动创建一张ARP表,把逻辑(IP)地址和物理地址关联起来。 动态

2021-08-22 10:47:54 3958

3958 CAN总线上日益增长的带宽需求。相比于CAN2.0主要有2点增强:将数据位段增加到最多64数据字节(CAN 2.0最大为8个数据字节)。标称位和数据位使用不同的比特率,标称位的比特率和CAN...

2021-10-29 11:21:11 19

19 ArmCortex-M4处理器采用哈佛结构,可以使用相互独立的总线来读取指令和加载/存储 数据。指令代码和数据都位于相同的存储器地址空间,但在不同的地址范围。程序存储器, 数据存储器,寄存器和I/O

2021-12-04 13:51:04 13

13 STM32F103系列芯片的地址和寄存器映射原理、LED轮流闪烁实现文章目录STM32F103系列芯片的地址和寄存器映射原理、LED轮流闪烁实现1 寄存器介绍1 寄存器介绍寄存器是中央处理器内

2021-12-05 15:21:04 3

3 这里写目录标题STM32(CM3内核) 内存映射一.CM3内核简介二.CM3内核地址映射三.搭建代码,实现映射STM32(CM3内核) 内存映射一.CM3内核简介《CM3权威指南》摘抄一段简介

2021-12-07 19:21:12 9

9 位待操作是如何实现的代码代码解读基地址映射偏移地址映射例程STM32地址基地址、总线地址、寄存器地址是什么基地址以及偏移地址这是stm32的系统结构图,只需要看一下红线框出来的地方即可从下图可以看到

2022-01-12 18:21:32 1

1 本文介绍如何试用MediaPipe实现人脸3D点云数据提取,提取的数据为人脸468点位。

2023-02-23 17:47:23 2490

2490 。这些关系通常不明确,并且可以跨越数据库。Dataedo将数据库中的外键读取到数据字典中,允许您使用手动定义的关系扩展此信息,并使用ER图将它们可视化。 提取外键 定义额外的表关系 可视化ERD中的表关系 定义跨数据库和数据集的关系 用学科领域

2023-06-19 09:52:32 1244

1244

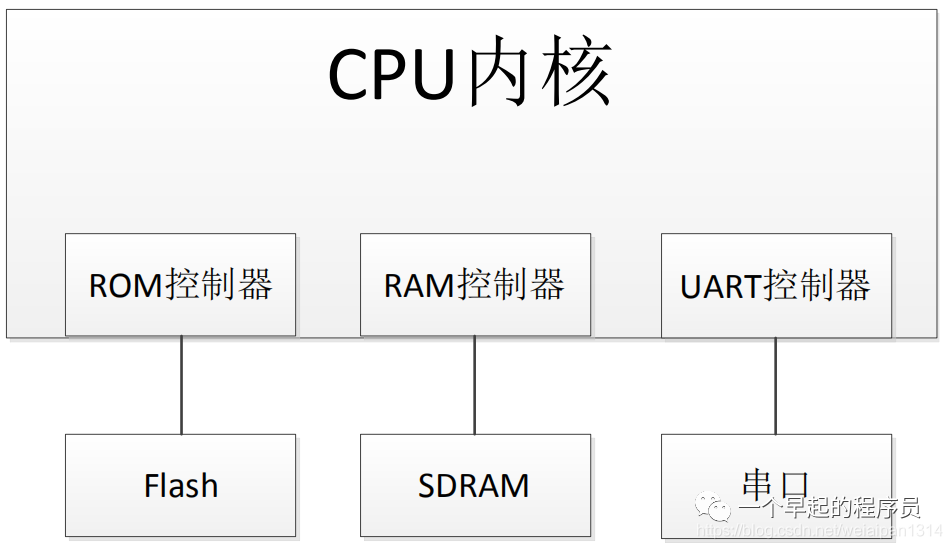

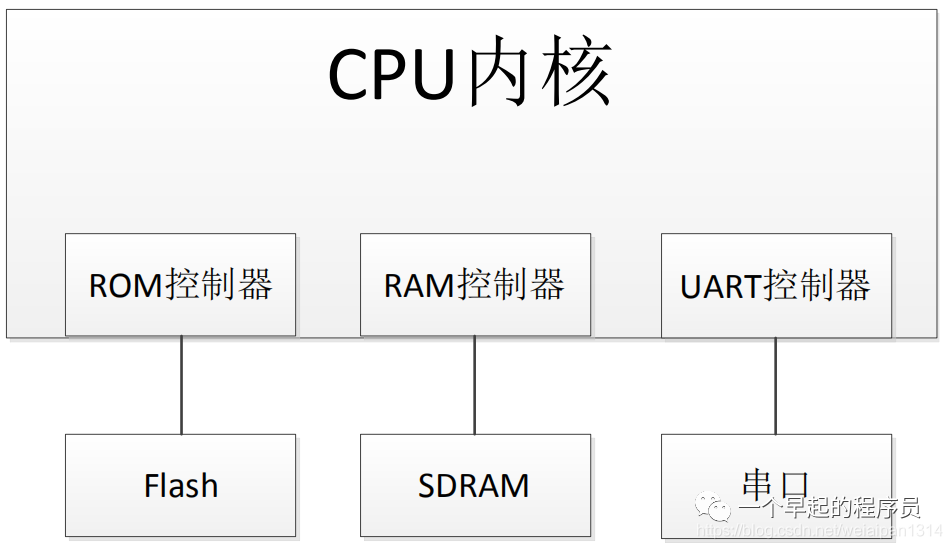

很多人对总线和地址映射的概念都是一头雾水,但是我们如果知道为何需要总线和地址映射,他们是在什么背景下被衍化出来的,自然而然对此概念就清清楚楚了。

2023-07-24 11:14:59 1880

1880

can总线的数据帧中数据长度码和数据字节数的关系? CAN总线是一种常用于数据通信的协议,它使用数据帧来传输信息。在CAN数据帧中,数据长度码(DLC)和数据字节数是紧密相关的。 首先,我们来了

2024-01-31 11:31:52 4199

4199 fpga和数字ic区别 FPGA(现场可编程逻辑门阵列)和数字IC(集成电路)在设计、功能、应用等方面存在显著的区别。 FPGA和数字IC在设计上有不同的特点。FPGA是一种可以重构电路的芯片,其

2024-03-14 18:08:23 4332

4332

电子发烧友App

电子发烧友App

评论