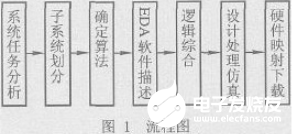

本文介绍了一种以FPGA 为基础的数字密码锁。采用自顶向下的数字系统设计方法, 将数字密码锁系统分解为若干子系统, 并且进一步细划为若干模块, 然后用硬件描述语言VHDL 来设计这些模块, 同时进行硬件测试。

2015-08-04 16:47:51 10182

10182

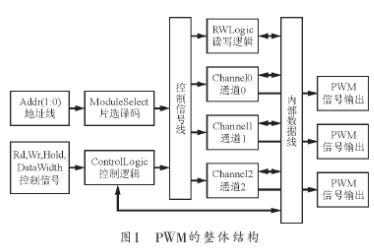

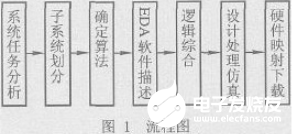

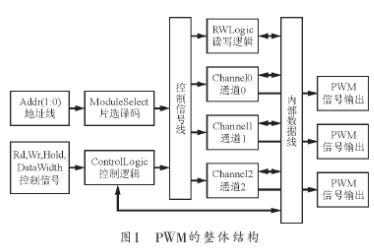

在采用自顶向下(Top_Down)正向设计PWM器件的过程中,芯片的结构划分和规格定制是整个设计的重要环节,因此合理的结构设计将决定整个设计的成败。

2020-10-28 10:35:14 3530

3530

本次的设计为多路UART/SPI通信系统,可以实现一对多的通信。系统可以运行在UART模式,也可以运行在SPI模式。我选择这一课题的原因主要是目前我所在的实验室需要写基于UART的快速通信。这一

2022-10-24 10:55:09 1746

1746 `UART 主要由 UART 内核、信号监测器、移位寄存器、波特率发生器、计数器、总线选择器和奇偶校验器总共 7 个模块组成,如图 5-5 所示。图 5-5 UART 实现原理图UART 各个模块

2018-10-18 09:51:47

,力求深入浅出,简单易懂涵盖从基本逻辑电路设计到DSP模块设计,再到基于软核处理器的设计列举大量实例讲解难于理解的内容,并给出详细说明和实现步骤着力贯彻自顶向下的设计思路,培养层次化和模块化的设计思想

2012-05-08 15:21:24

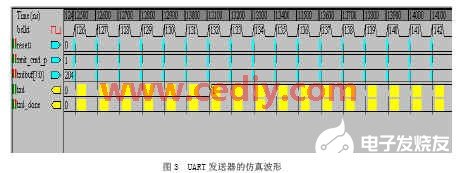

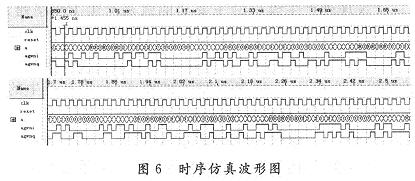

的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA片上UART的设计,给出了仿真结果。关键词:通用异步收发器;串口通信;现场可编程逻辑器件;有限状态机

2019-06-21 07:17:24

就不是最合适的。本设计使用Xilinx 的FPGA 器件,只将UART 的核心功能嵌入到FPGA 内部,不但实现了电路的异步通讯的主要功能,而且使电路更加紧凑、稳定、可靠。 1 引 言

2015-02-05 15:33:30

外设连接如图2.17所示。FPGA器件通过UART转USB芯片PL2303将标准的UART协议转换为USB协议,在PC端安装驱动后,便是一个虚拟串口实现UART的传输。图2.17 FPGA与UART

2017-10-28 20:05:14

1、在FPGA中实现串口协议的设计在FPGA中实现串口协议,通过Anlogic_FPGA开发板上的“UART2USB”口接收从计算机发来的数据。实验设计思路UART串口是一种类似于USB、VGA

2022-07-19 11:09:48

基于FPGA的高速实时图像采集和自适应阈值算法提出了基于FPGA的图像处理自适应阈值算法,实现了激光光斑中心的高速实时检测。采用3×3窗口模块和自适应阈值模块,先对CCD输入数据进行处理,判断光斑

2012-08-11 15:38:18

【作者】:刘雪冬【来源】:《华南理工大学》2009年【摘要】:自顶向下的设计方法及装配建模技术是在消费品行业应用比较成熟的一种设计方法和理论;但是有鉴于通用机械设计的复杂性、多样性和关联性等特点

2010-04-24 09:20:57

如何实现扩频通信调制器自顶向下的设计?如何实现扩频通信调制器的仿真测试?

2021-04-29 06:46:04

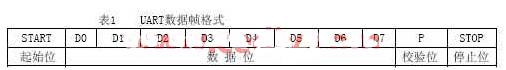

如何利用FPGA实现UART的设计?UART的结构和帧格式

2021-04-08 06:32:05

本文详细讨论了基于cadenceVirtuoso设计平台的单片射频收发集成电路的设计过程。讨论了利用VirtUOSO工具完成的自顶向下、从系统到模块、从前端都后端的整个设计步骤,直到实现一个完整的射频芯片。

2021-04-22 06:57:22

自适应算术编码的基本原理是什么?自适应算术编码的FPGA实现如何对自适应算术编码进行仿真?

2021-04-30 06:50:44

本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2021-05-07 06:33:09

本文利用先进的EDA软件,用VHDL硬件描述语言采用自顶向下的模块化设计方法,完成了具有相序自适应功能的双脉冲数字移相触发器的IP软核设计。

2021-04-28 06:39:00

针对高速无线数据通讯的实时性要求,提出采用FPGA来实现可配置均衡器的设计,在设计过程中采用自顶而下划分的设计方式,即方便了设计的需要,同时又满足了性能的要求,在实际项目中收到很好的效果。

2021-04-29 06:48:32

现代通信信号处理发展到3G、4G时代后,每秒上百兆比特处理速度的要求对于自适应处理技术是一个极大的挑战。使用具有高度并行结构的FPGA实现自适应算法以及完成相应的调整和优化,相比于在DSP芯片上的算法实现可以达到更高的运行速度。

2019-08-23 08:03:10

刚接触FPGA 想用FPGA实现422通讯 求大牛给一个实现UART的VHDL的程序

2013-12-05 20:40:39

本文主要研究了一种基于FPGA、自顶向下、模块化、用于提取位同步时钟的全数字锁相环设计方法。

2021-05-06 08:00:46

。最后一步是进行 ASIC 的版图设计,即将电路转换成版图,或者用可编程ASIC 实现(CPLD/FPGA)。图 1.3.1 是“自底向上”和“自顶向下”两种设计方法的设计步骤。

2019-02-27 14:00:22

),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2012-05-23 19:37:24

求推荐一款赛灵思的FPGA, 要求实现LMS自适应滤波,较高的处理速度,我数据进来的速率 62.5M/s

2013-08-20 17:28:13

介绍可编程逻辑器件的结构和开发软件MAX+PLUSII 主要特点,以交通控制系统电路芯片设计为例, 叙述自顶向下的设计方法。

2009-04-16 14:14:42 26

26 介绍了Altera公司生产的可编程逻辑器件EPM7032的内部结构和性能特点,给出了采用自顶向下的层次化设计方法进行自动交通控制系统的设计方案,同时给出了选用EPM7032可编程逻辑器件和M

2009-04-23 16:22:12 60

60 介绍可编程逻辑器件的结构和开发软件MAX+PLUSII 主要特点,以交通控制系统电路芯片设计为例, 叙述自顶向下的设计方法。

2009-05-14 14:46:48 23

23 本文提出了一种采用FPGA 技术开发的自诊断传感器接口方案,能够单板实现多达128路自诊断传感器的信号解码并通过Profibus 总线进行传输关键词:FPGA;传感器;自诊断;Profibus;Veri

2009-06-12 15:43:15 17

17 介绍了一种基于FPGA 的LED 大屏设计方案,采用自顶向下的设计思想,设计了基于FPGA 的双口RAM 和扫描控制电路,解决了传统LED 大屏设计中,控制系统复杂﹑可靠性差的问题。关键

2009-06-15 09:34:14 26

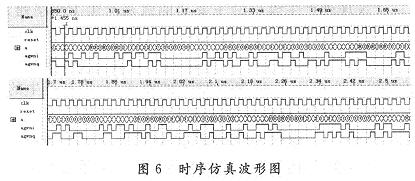

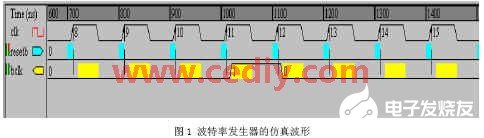

26 文章介绍了一种采基于FPGA 实现UART电路的方法,并对系统结构进行了模块化分解以适应自顶向下的设计方法。采用有限状态机对接收器模块和发送器模块进行了设计,所有功能的

2009-08-15 09:27:55 46

46 文章介绍了一种在现场可编程门阵列(FPGA)上实现UART 的方法。UART 的波特率可设置调整,工作状态可读取。系统结构进行了模块化分解,使之适应自顶向下(Top-Down)的设计

2009-08-21 11:35:03 52

52 本文介绍了自适应滤波器的实现方法,给出了基于LMS 算法自适应滤波器在FPGA 中的实现,简单介绍了这种实现方法的各个功能模块,主要包括输入信号的延时输出模块、控制模块

2009-09-14 15:51:00 34

34 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。关键词 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 24

24 本文设计了一种基于 FPGA 的UART 核,该核符合串行通信协议,具有模块化、兼容性和可配置性,适合于SoC 应用。设计中使用Verilog HDL 硬件描述语言在Xilinx ISE 环境下进行设计、仿真,

2009-11-27 15:48:51 20

20 本文介绍了一种基于FPGA 的用自定义串口命令的方式实现MDIO 接口逻辑设计的方法,并对系统结构进行了模块化分解以适应自顶向下的设计方法。所有功能的实现全部采用VHDL 进行描

2009-12-26 16:48:44 103

103 利用 FPGA 实现UART 的设计引 言随着计算机技术的发展和广泛应用,尤其是在工业控制领域的应用越来越广泛,计算机通信显的尤为重要。串行通信虽然使设备之间的连线大为减

2010-03-24 09:23:40 49

49 IO模拟UART实现

本应用用于扩展UART端口,在单片机自带的UART口不够用的情况下,使用GPIO和定时器实现模拟UART通信。可增加两个模拟的UART模块。

2010-03-26 09:20:40 69

69 1.产品概述WK2124是SPITM接口的4通道UART器件,WK2124实现SPI桥接/扩展4个增强功能串口(UART)的功能。扩展的子通道的UART具备如下功能特点:每个子通道UART的波特率

2023-11-24 00:17:37

利用Verilog HDL 硬件描述语言自顶向下的设计方法和QuartusⅡ 软件,在复杂的可编程逻辑器件(FPGA, Field Programmable Gate Array)中实现了发电机组频率测量计的设计。该设计采用了光电隔离

2010-08-06 15:52:40 18

18 文章介绍了一种在现场可编程门阵列(FPGA)上实现UART 的方法。首先阐述了UART 异步串行通信原理,然后介绍了实现UART异步串行通信的硬件接口电路及各部分硬件模块,以及用硬件

2010-08-06 16:24:13 55

55 介绍了一种基于FPGA的汽车油改气电控系统的研究与设计,采用自顶向下模块化设计, 依据功能将FPGA划分成几个模块,详细论述了各模块的设计方法和控制流程,给出核心模块的状

2010-09-08 10:39:14 28

28 串行外设都会用到RS232-C异步串行接口,传统上采用专用的集成电路即UART实现,如TI、EXAR、EPIC的550、452等系列,但是我们一般不需要使用完整的UART的功能

2006-05-26 21:52:09 895

895

摘 要 :UART是广泛使用的串行数据通讯电路。本设计包含UART发送器、接收器和波特率发生器。设计应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2009-06-20 13:14:52 1267

1267

摘要: 在简单介绍算术编码和自适应算术编码的基础上,介绍了利用FPGA器件并通过VHDL语言描述实现自适应算术编码的过程。整个编码系统在LTERA公司的MAX+plus Ⅱ软

2009-06-20 13:40:24 1356

1356

基于FPGA的AGWN信号生成器

在通信系统中分析计算系统抗噪声性能时,经常假定信道噪声为加性高斯型白噪声(AGWN)。本文就是通过分析AGWN的性质,采用自顶向下的设计思

2009-12-25 10:10:29 1092

1092

VLIW处理器的设计与实现 摘要! 介绍了基于FPGA 实现VLIW微处理器的基本方法# 对VLIW微处理器具体划分为C 个 主要功能模块$ 依据FPGA的设计思想#采用自顶向下和文本与原理图相结合的流水线方式的设计方 法# 进行VLIW微处理器的5 个模块功能设计# 从而最终实现

2011-01-25 19:05:11 21

21 基于现场可编程(FPGA)技术和硬件描述语言VHDL的设计和综合,通过自顶向下的设计方法和模块化设计思想,在Quartus II环境下能定制、仿真、下载验证和实现CPU功能。通过VHDL语言定制了运算器ALU模块和调用宏模块定制了RAM模块,介绍了基于FPGA的CPU设计方法,

2011-03-15 17:39:19 178

178 介绍了QDPSK信号的优点,并分析了其实现原理,提出一种QDPSK 高性能数字调制器的FPGA实现方案。采用自顶向下的设计思想,将系统分成串/并变换器、差分编码器、逻辑选相电路、四相载

2011-05-05 16:17:53 78

78 提出一种 OFDM 高性能数字调制器的FPGA实现方案;采用自顶向下的设计思想,将系统分成FIR滤波器、数控振荡器、移相器、乘法电路和加法电路等5大模块,重点论述了FIR滤波器、数控振

2011-08-15 11:15:53 62

62 FPGA的常用设计方法包括自顶向下和自下而上,目前大规模FPGA设计一般选择自顶向下的设计方法。 所谓自顶向下设计方法, 简单地说,就是采用可完全独立于芯片厂商及其产品结构的描述语

2011-09-06 15:08:50 363

363 随着FPGA的广泛应用,经常需要FPGA与其他数字系统进行串行通信,专用的UART集成电路如8250,8251等是比较复杂的,因为专用的UART集成电路既要考虑异步的收发功能,又要兼容RS232接口设计

2011-09-16 11:57:43 5053

5053

目前利用FPGA设计高性能的嵌入式处理器已经成为SOC设计的重要部分,对一种基于FPGA芯片的嵌入式PLC处理器进行了研究和设计,并采用了基于VHDL语言的自顶向下的模块化设计方法,顶层

2011-09-28 18:19:50 2186

2186

该设计采用了自顶向下的模块化划分和有限状态机相结合的方法,由于其应用了标准的Wishbone总线接口,从而使微机系统与串行设备之间的通信更加灵活方便。验证结果表明,这种新的架构

2011-10-19 15:01:54 27

27 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。

2011-12-17 00:15:00 59

59 LMS自适应滤波器是一种广泛使用的数字信号处理算法,对其实现有多种方法.通过研究其特性的基础上,提出了在FPGA 中使用软处理的嵌入式实现方案,文中对实现方式的优缺点进行了

2012-02-14 16:37:02 75

75 介绍了一种基于FPGA 的LED 大屏设计方案,采用自顶向下的设计思想,设计了基于FPGA 的双口RAM 和扫描控制电路,解决了传统LED 大屏设计中,控制系统复杂﹑可靠性差的问题。

2012-03-02 16:48:46 34

34 介绍了MSK信号的优点,并分析了其实现原理,提出一种MSK高性能数字调制器的FPGA实现方案;采用自顶向下的设计思想,将系统分成串/并变换器、差分编码器、数控振荡器、移相器、乘

2012-04-12 14:40:40 65

65 UART 即通用异步收发器,传统上采用多功能的专用集成电路实现。但是在一般的使用中往往不需要完整的UART 的功能,比如对于多串口的设备或需要加密通讯的场合使用专用集成电路

2012-05-23 10:13:33 3760

3760

串行外设都会用到RS232-C异步串行接口,传统上采用专用的集成电路即UART实现,如TI、EXAR、EPIC的550、452等系列,但是我们一般不需要使用完整的UART的功能,而且对于多串口的设备或需要

2012-06-04 11:42:50 1405

1405

针对传统高炉TRT顶压控制系统的不足,提出一种基于FPGA实现的系统设计方法,以EP2C35 FPGA作为主控芯片,采用模块化的设计思想,实现了高炉顶压的模糊自适应PID控制。实验结果表明,

2012-10-16 15:58:42 25

25 基于FPGA的光电系统同步自适应电路设计与实现

2016-01-04 17:03:55 11

11 华清远见FPGA代码-RS-232C(UART)接口的设计与实现

2016-10-27 18:07:54 10

10 一种改进的NLMS自适应滤波器的FPGA实现_赵茂林

2017-01-08 10:30:29 2

2 基于FPGA/CPLD的UART功能设计

2017-01-23 20:45:37 31

31 通过模块之间的调用实现自顶向下的设计目的:学习状态机的嵌套使用实现层次化、结构化设计。

2017-02-11 05:53:38 2657

2657

LMS自适应算法的FPGA设计与实现_陈亮

2017-03-19 11:27:34 5

5 FPGA和UART的MCU总线数据采集系统设计

2017-10-31 15:20:51 8

8 设计和实现了基于FPGA的可编程数字下变频器(DDC),用于宽带数字中频软件无线电接收机中,主要完成了数字下变频、数据抽取等功能。采用自顶向下的模块化设计方法,将整个下变频器划分为基本单元,实现这些

2017-11-22 09:09:56 6993

6993

本文介绍如何利用VHDL硬件描述语言设计一个具有年、月、日、星期、时、分、秒计时显示功能,时间调整功能和整点报时功能的数字日历。在QuartusⅡ开发环境下,采用自顶向下的设计方法,建立各个基本模块

2019-04-23 08:25:00 5221

5221 FPGA芯片却没有这个特点,所以使用FPGA作为处理器可以有两个选择,第一个选择是使用UART芯片进行串并转换,第二个选择是在FPGA内部实现UART功能。

2019-10-18 07:54:00 3397

3397

在Altera Cyclone II 平台上采用“自顶向下”的模块化设计思想及VHDL 硬件描述语言,设计了串行通信控制系统。在Quartus II 软件上编译、仿真后下载到FPGA 芯片

2018-11-07 11:18:23 6

6 利用Verilog HDL 硬件描述语言自顶向下的设计方法和QuartusⅡ 软件,在复杂的可编程逻辑器件(FPGA, Field Programmable Gate Array)中实现了发电机组

2018-11-16 16:48:06 2

2 FPGA的设计是一个系统工程,是一种道,会编程会仿真会调试可能更多是一种术。很多这方面的书籍,写什么自顶向下之类的很多,还是停留在方法学上,而对于一个公司的项目来说,FPGA的设计是从立项开始的。

2019-02-27 14:25:11 665

665 三方面的电子设计工作,即集成电路设计、电子电路设计以及PCB设计。总之,EDA技术的基本特征是采用具有系统仿真和综合能力的高级语言描述。它一般采用自顶向下的模块化设计方法。但是由于所设计的数字系统的规模大小不一,且系统内部逻辑关系复杂,如何划分逻辑功能模块便成为设计数字系统的最重要的任务。

2020-01-21 16:50:00 9552

9552

的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 15:51:05 12

12 的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 17:28:03 10

10 从CPU的总体结构到局部功能的实现采用了自顶向下的设计方法和模块化的设计思想,利用Xilinx 公司的Spartan II 系列FPGA,设计实现了八位CPU软核。在FPGA内部不仅实现了CPU必需

2020-08-03 17:58:56 13

13 从CPU的总体结构到局部功能的实现采用了自顶向下的设计方法和模块化的设计思想, 利用Xilinx 公司的Spartan II 系列FPGA, 设计实现了八位CPU软核。在FPGA 内部不仅实现了

2020-08-19 17:43:19 7

7 本设计采用EDA技术,以硬件描述语言VHDL为系统逻辑描述手段设计文件,在QUARTUSII工具软件环境下, 采用自顶向下的设计方法, 由各个基本模块共同构建了一个基于FPGA的数字钟。

2020-08-28 09:36:00 30

30 Verilog HDL作为一种规范的硬件描述语言,被广泛应用于电路的设计中。它的设计描述可被不同的工具所支持,可用不同器件来实现。利用Verilog HDL语言自顶向下的设计方法设计交通灯控制系统

2020-10-10 17:08:00 34

34 在分析传统自适应滤波算法的基础上,针对自适应滤波器的硬件实现,采用一种适合FPGA实现的DLMS算法。使用VHDL语言完成设计,仿真实验验证了设计的正确性,经过编译和布局布线后对改进算法和传统算法进行了比较,结果表明改进算法在增加硬件消耗较少的情况下有效提高了系统工作频率。

2021-01-22 16:12:24 12

12 了当前普追采用的多UART的方法和Actel公司提供的标准8051和UAI玎(通用异步收发器)。在IP核的基础上,通过两块FPGA内部RAM,设计出一种“桥”的办法,用Vcalog硬件描述语言实现多个UART的扩展,并在M0ddS.蛆中进行仿真验证,最后在Acid公司的H礅(现

2021-02-02 15:15:00 11

11 主要介绍基于FPGA实现多路模拟信号自适应采集系统的设计。该系统主要包括软件和硬件两部分:硬件主要采用FPGA芯片,AD7982—1,ADG406和运放AD824来搭建硬件平台;软件包括FPGA程序

2021-02-02 15:52:34 5

5 的。本设计使用Xilinx的FPGA器件,只将UART的核心功能嵌入到FPGA内部,不但实现了电路的异步通讯的主要功能,而且使电路更加紧凑、稳定、可靠。

2021-04-27 14:07:25 9

9 基于FPGA的自适应LMS算法的实现资料免费下载。

2021-05-28 10:52:09 19

19 基于FPGA的UART模块设计与实现介绍说明。

2021-06-01 09:43:30 20

20 本次的设计为多路UART/SPI通信系统,可以实现一对多的通信。系统可以运行在UART模式,也可以运行在SPI模式。我选择这一课题的原因主要是目前我所在的实验室需要写基于UART的快速通信。这一

2023-02-20 11:10:31 2392

2392 本文档包含Jim Kurose和Keith Ross编写的《计算机网络:自顶向下方法(第7版)》复习题和问题的参考答案。这些答案只对指导老师有效。请不要复制或者分发给其他人(即使是其他指导老师)。请

2023-03-13 14:23:08 0

0 EDA(Electronic Design Automation,电子设计自动化)自顶向下的设计方法是一种常见的电子电路设计方法。该方法将电路设计分为多个模块,从系统级别出发,逐步分解成较低层次的模块,直到达到设计细节的层次,最终将每个模块进行详细的设计。

2023-04-10 16:49:22 4855

4855 目的:实现上位机与FPGAuart交互

开发环境:quatus prime 18.1,芯片 altera :EP4CE15F23C8。

实验现象: 1.使用uart:bps=9600(参数可调整

2023-05-08 10:28:33 2

2 电子发烧友网站提供《基于FPGA的高炉TRT顶压控制系统的研究与设计.pdf》资料免费下载

2023-10-23 09:43:56 0

0

电子发烧友App

电子发烧友App

评论