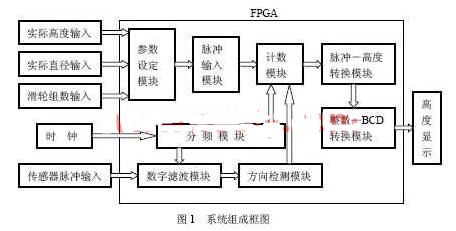

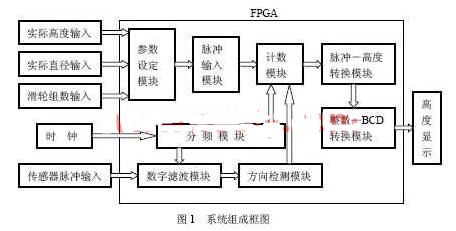

本文采用的是ALTERA公司的EP1C6Q240C8型号的FPGA,整个体统采用模块化设计的思想,将各个模块用VHDL语言描述出来再进行连接。

2020-08-04 09:39:44 2332

2332

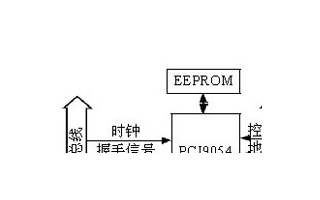

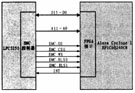

为了方便对1553B设备进行测试,介绍了一种基于ARM9平台和FPGA的1553B总线测试系统的设计与实现方法。该系统以LPC3250作为微处理器,以CYCLONE I系列的EP1C6Q240C8芯片实现ARM与1553B协议芯片的接口逻辑。

2015-04-21 14:49:08 4605

4605

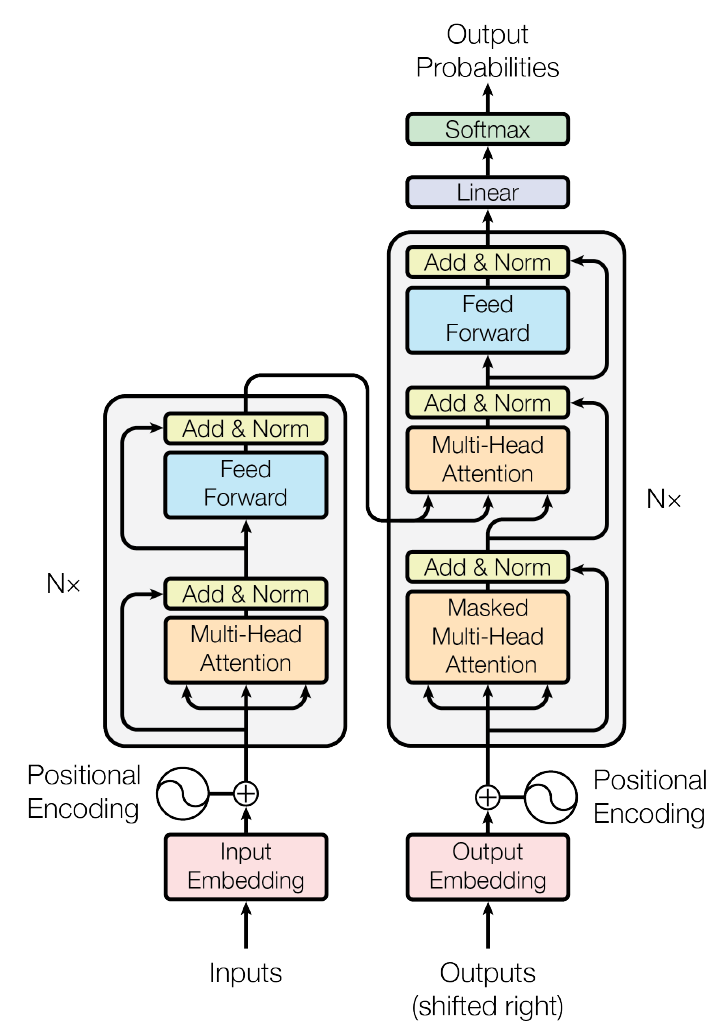

前言 AI芯片(这里只谈FPGA芯片用于神经网络加速)的优化主要有三个方面:算法优化,编译器优化以及硬件优化。算法优化减少的是神经网络的算力,它确定了神经网络部署实现效率的上限。编译器优化和硬件优化

2020-09-29 11:36:09 5773

5773

现在Altera的网页已经下载不到支持EP1C6Q240元件的开发软件,求各位网友大力支持!

2025-06-11 06:15:28

本帖最后由 mr.pengyongche 于 2013-4-30 02:58 编辑

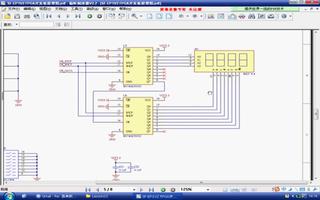

EP1C6Q240C6开发板原理

2012-08-11 10:10:06

EP1C6Q240C6开发板原理图

2012-08-20 15:21:25

本资料为EP1C6Q240C6开发板原理图

2012-04-19 11:19:41

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8这三种芯片的区别,用哪种芯片较好?买哪种芯片的学习开发板较好? 谢谢大家的求解!!!

2013-07-21 19:46:34

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8这是三种芯片的区别,用哪种芯片较好?买哪种芯片的开发板较好?谢谢大家的求解啊!!!

2013-07-21 19:58:40

一、FPGA核心板:多种核心板供选择,所采用的FPGA分别有:(1)Cyclone核心:EP1C12Q240C8、EP1C6Q240C8;(2)CycloneII核心

2009-11-02 18:55:54

有:(1)Cyclone核心:EP1C12Q240C8、EP1C6Q240C8;(2)CycloneII核心:EP2C8Q208C8、EP2C5Q208C8、EP2C20Q208C8;(3)SDRAM

2009-10-23 15:15:24

毕业设计得做与FPGA有关的论文 ,现在正在用***画 FPGA EP1C6Q240C8 外围电路图,请教各位高手,本人不会,谢谢~!

2009-04-07 09:15:55

board manual.pdfEP1C6Q240C6开发板原理图.pdfEPM1270F256C5 MAX_II_board_schematics.pdf

2012-04-19 11:12:40

第1章 概述 1.1 人工神经网络研究与发展 1.2 生物神经元 1.3 人工神经网络的构成 第2章人工神经网络基本模型 2.1 MP模型 2.2 感知器模型 2.3 自适应线性

2012-03-20 11:32:43

如题,Altera的FPGA芯片EP2C8Q208开发板没驱动,u***驱动不了,怎么办呀,求助

2013-10-28 12:18:14

;nbsp;核心是DSP 处理器TMS320VC5416,最高工作频率160M2、 扩展一片Altera 15万门Cyclone FPGA EP1C6Q240C8,给

2009-11-27 15:49:35

是一台包含GPU的服务器或高性能PC,Device从机是一个ZYNQ/FPGA开发板。另一方面,通常情况下,当落地到具体场景解决某个具体问题时,神经网络算法通常仅是整体解决方案的一小部分,其他的算法和流程

2020-05-18 17:13:24

FPGA加速的关键因素是什么?EdgeBoard中神经网络算子在FPGA中的实现方法是什么?

2021-09-28 06:37:44

NMSIS NN 软件库是一组高效的神经网络内核,旨在最大限度地提高 Nuclei N 处理器内核上的神经网络的性能并最大限度地减少其内存占用。

该库分为多个功能,每个功能涵盖特定类别

2025-10-29 06:08:21

CY7C68013A-128AXC、FPGA芯片EP1C6Q240C8和SDRAM芯片IS61LV25616AL-10T共同组合完成,实现USB2.0的高速传输。本USB+FPGA开发板的实际传输速度

2010-03-25 16:01:56

请问:我在用labview做BP神经网络实现故障诊断,在NI官网找到了机器学习工具包(MLT),但是里面没有关于这部分VI的帮助文档,对于”BP神经网络分类“这个范例有很多不懂的地方,比如

2017-02-22 16:08:08

习神经神经网络,对于神经网络的实现是如何一直没有具体实现一下:现看到一个简单的神经网络模型用于训练的输入数据:对应的输出数据:我们这里设置:1:节点个数设置:输入层、隐层、输出层的节点

2021-08-18 07:25:21

《 AI加速器架构设计与实现》+第一章卷积神经网络观感

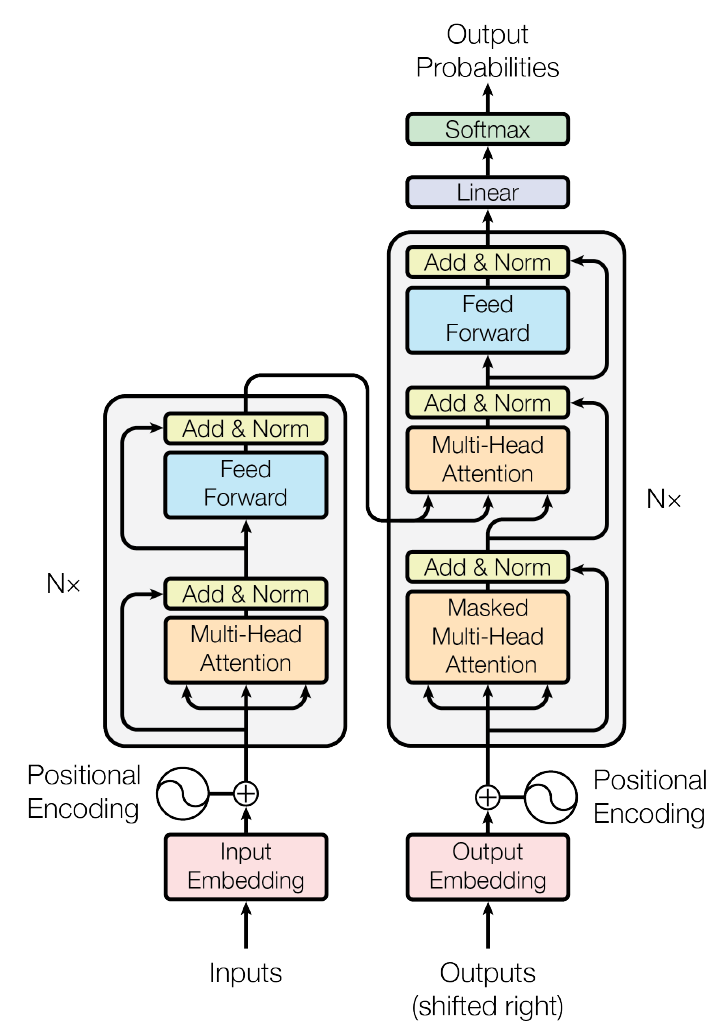

在本书的引言中也提到“一图胜千言”,读完第一章节后,对其进行了一些归纳(如图1),第一章对常见的神经网络结构进行了介绍,举例了一些结构

2023-09-11 20:34:01

的神经网络编程,想基于此开发板,进行神经网络的学习,训练和测试神经网络。项目计划:1.基于官方的文档及资料,熟悉此开发板。2.测试官方demo,学习ARM内核和FPGA如何协调工作。3.基于自己最近

2019-01-09 14:48:59

项目名称:基于PYNQ的神经网络自动驾驶小车试用计划:一、本人技术背景本人有四年以上的嵌入式开发和三年以上的机器视觉领域项目实践经验,在计算机视觉与FPGA数字图像处理方面有较多的理论研究与项目实践

2018-12-19 11:36:24

,得到训练参数2、利用开发板arm与FPGA联合的特性,在arm端实现图像预处理已经卷积核神经网络的池化、激活函数和全连接,在FPGA端实现卷积运算3、对整个系统进行调试。4、在基本实现系统的基础上

2018-12-19 11:37:22

,神经网络技术的第三次发展浪潮仍在继续,在其背后,高性能CPU、GPU和FPGA、ASIC以强大的算力为技术的应用落地提供了有力的支持。然而目前基于FPGA平台搭建神经网络作为控制器,适合我们自己动手实现

2019-03-02 23:10:52

人工神经网络(Artificial Neural Network,ANN)是一种类似生物神经网络的信息处理结构,它的提出是为了解决一些非线性,非平稳,复杂的实际问题。那有哪些办法能实现人工神经网络呢?

2019-08-01 08:06:21

简单理解LSTM神经网络

2021-01-28 07:16:57

我们可以对神经网络架构进行优化,使之适配微控制器的内存和计算限制范围,并且不会影响精度。我们将在本文中解释和探讨深度可分离卷积神经网络在 Cortex-M 处理器上实现关键词识别的潜力。关键词识别

2021-07-26 09:46:37

FPGA实现神经网络关键问题分析基于FPGA的ANN实现方法基于FPGA的神经网络的性能评估及局限性

2021-04-30 06:58:13

FPGA 上实现卷积神经网络 (CNN)。CNN 是一类深度神经网络,在处理大规模图像识别任务以及与机器学习类似的其他问题方面已大获成功。在当前案例中,针对在 FPGA 上实现 CNN 做一个可行性研究

2019-06-19 07:24:41

不确定因素影响,并且随着可编程片上系统SoPC和大规模现场可编程门阵列FPGA的出现,为神经网络控制器的硬件实现提供了新的载体。

2019-08-12 06:25:35

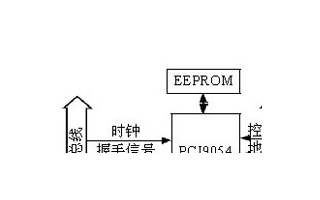

某人工神经网络的FPGA处理器能够对数据进行运算处理,为了实现集数据通信、操作控制和数据处理于一体的便携式神经网络处理器,需要设计一种基于嵌入式ARM内核及现场可编程门阵列FPGA的主从结构处理系统满足要求。

2021-05-21 06:35:27

训练一个神经网络并移植到Lattice FPGA上,通常需要开发人员既要懂软件又要懂数字电路设计,是个不容易的事。好在FPGA厂商为我们提供了许多工具和IP,我们可以在这些工具和IP的基础上做

2020-11-26 07:46:03

(Digital Signal Processor)相比,现场可编程门阵列(Field Programma-ble Gate Array,FPGA)在神经网络的实现上更具优势。DSP处理器在处理时采用指令顺序执行

2019-08-08 06:11:30

FPGA的嵌入式应用。某人工神经网络的FPGA处理器能够对数据进行运算处理,为了实现集数据通信、操作控制和数据处理于一体的便携式神经网络处理器,需要设计一种基于嵌入式ARM内核及现场可编程门阵列FPGA的主从结构处理系统满足要求。

2019-09-20 06:15:20

学生做创新实验 学校提供的EP1C6Q240C8N芯片 但是没有给芯片的资料。自己去找的又全是英文版的 看不懂还不知道哪些有用。哪位用过的前辈麻烦指导一下,特别是AD转换那 如果有引脚介绍什么的就最好了 可以联系我QQ1428685070 万分感谢了

2013-09-17 23:15:57

小弟最近在设计一款双核采集系统使用ep1c6q240c8和tms320vc5509a双核,两块芯片使用外部双口RAM进行数据传输,请教各位大神ep1c6q240c8怎么和双口RAM连接啊???????????????????????

2012-11-05 10:42:41

FPGA型号为:EP1C6Q240C8

2016-09-17 15:46:18

1、加速神经网络的必备开源项目 到底纯FPGA适不适合这种大型神经网络的设计?这个问题其实我们不适合回答,但是FPGA厂商是的实际操作是很有权威性的,现在不论是Intel还是Xilinx都没有在

2022-10-24 16:10:50

脉冲耦合神经网络(PCNN)在FPGA上的实现,实现数据分类功能,有报酬。QQ470345140.

2013-08-25 09:57:14

采用EP1C6Q240C8和VHDL的定时器的设计

2012-08-17 09:53:38

基FPGA Cyclone II_EP2C5 EP2C8的频率计

基FPGA_Cyclone_II_EP2C5/EP2C8的频率计

功能描述:按4*4键盘上的1,2,3...号按键可依次测出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 斑梨电子FPGA CycloneII EP2C5T144 学习板 开发板产品参数1. 采用ALTERA公司的CyclonellEP2C5T144芯片作为核心最小系统,将FPGA

2023-02-03 15:14:29

此套开发板采用altera公司的CYCLONE II系列芯片EP2C5Q208C8 和 EP2C8 Q208C8作为核心处理器设计,CYCLONE II系列芯片可以说是目前市场上性价比最高的芯片,比第一代的EP1C6 或者 EP1C12等

2010-08-11 16:42:56 47

47 设计和实现了一个以Altera FPGA的Cyclone器件EP1C6Q240C8为核心的多功能实验板.它分为核心板和扩展板, 用户可以结合QuartusII集成开发环境, 使用VHDL语言、Verilog HDL语言或原理图, 进行编

2010-09-14 16:38:06 12

12 以89S52单片机和EP1C6Q240C8型FPGA为控制核心的多功能计数器,是由峰值检波、A/D转换、程控放大、比较整形、移相网络部分组成,可实现测量正弦信号的频率、周期和相位差的功能。多

2010-12-27 15:21:44 78

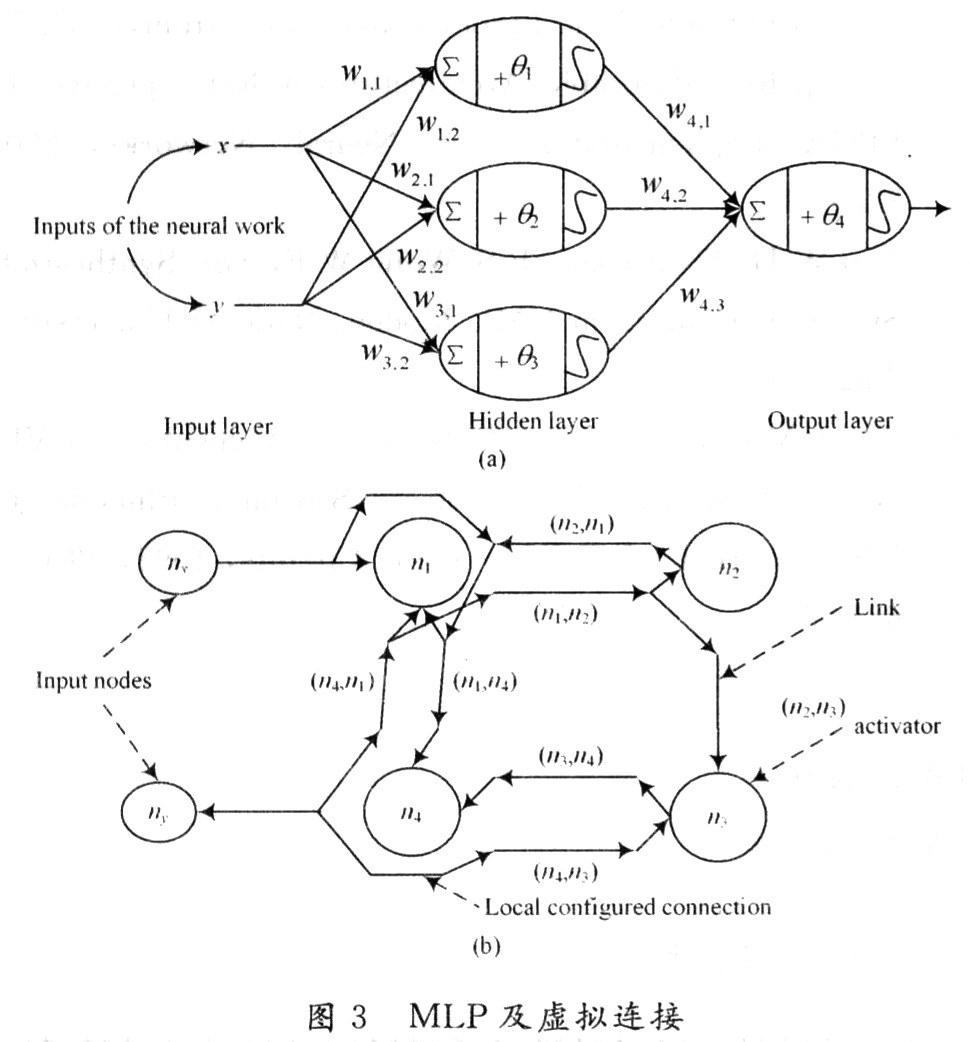

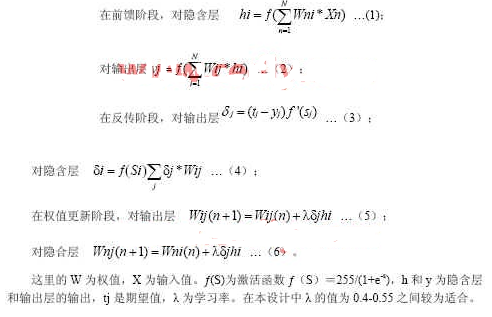

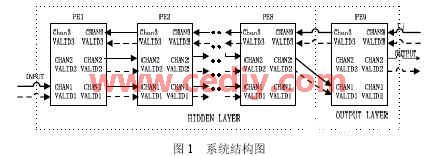

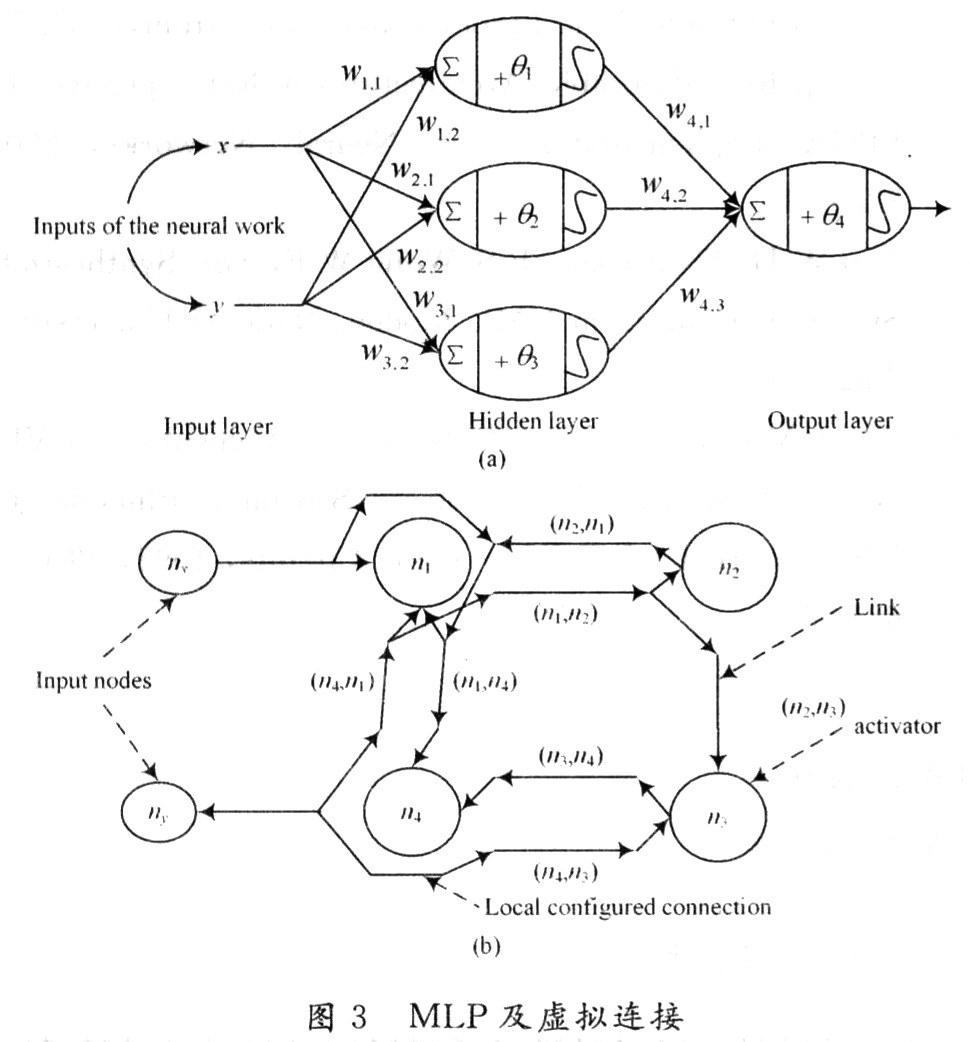

78 基于FPGA的人工神经网络实现方法的研究

引 言 人工神经网络(Artificial Neural Network,ANN)是一种类似生物神经网络的信息处理结构,它的提出是为了

2009-11-17 17:17:20 1428

1428

基于FPGA的人工神经网络实现方法的研究

引言

人工神经网络(ArtificialNeuralNetwork,ANN)是一种类似生物神经网络的信息处理结构,它的提出是为了解决一些非线

2009-11-21 16:25:24 5007

5007

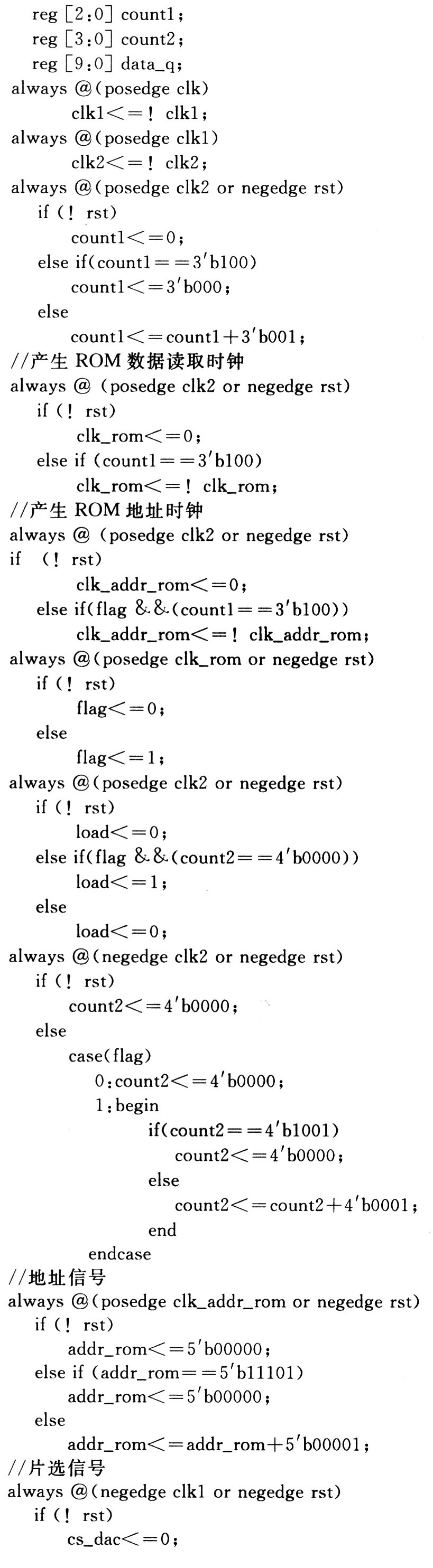

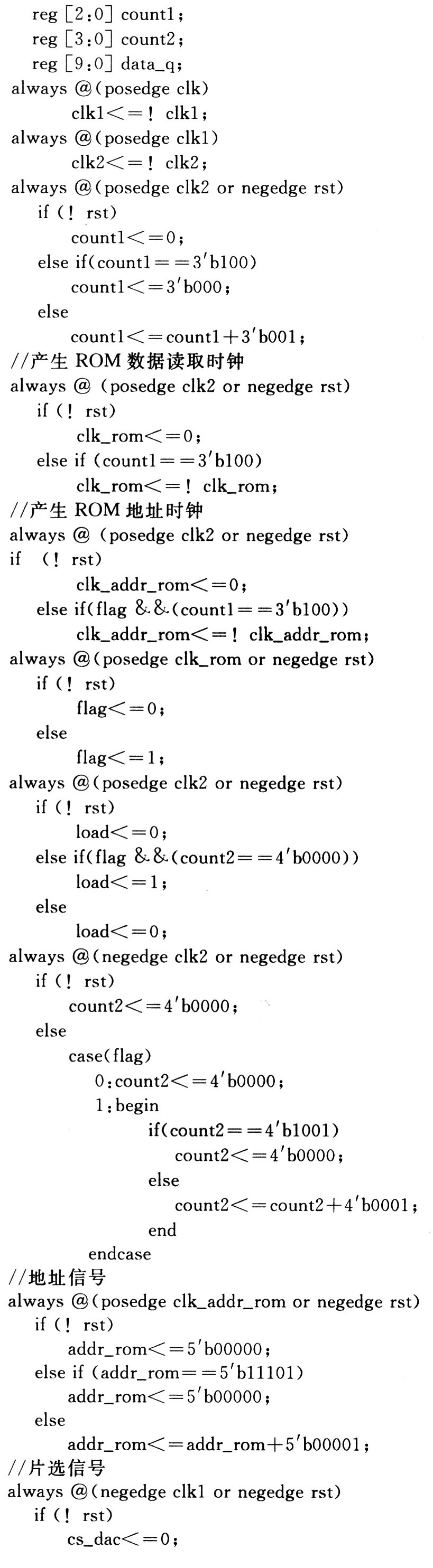

1 系统设计

采用Altera公司Cyclone系列EP1C6Q240C8为控制芯片。通过Altera的IP工具MegaWizard管理器定制LPM_ROM宏功能模块,用.mif格式文件存放产生电压的数据;利用硬件描述

2010-08-20 11:14:55 1502

1502

本内容展示了EP1C6Q240C6开发板的原理图,详细列出了开发板的原理图

2011-02-23 15:43:10 156

156 列举了EP2C8开发板原理图,详细说明了各版块的原理图

2011-02-23 15:45:23 279

279 设计和实现了一个以Altera FPGA的Cyclone器件EP1C6Q240C8为核心的多功能实验板.它分为核心板和扩展板, 用户可以结合QuartusII集成开发环境, 使用VHDL语言、Verilog HDL语言或原理图, 进行编辑、综

2011-06-27 15:58:37 95

95 介绍一种基于SOPC的基本信号产生器的设计技术,以Altera公司EP1C6Q240C8为硬件核心,把软核CPU嵌入到FPGA之中构成片上系统,以此实现基本信号产生器

2011-07-23 11:07:21 1292

1292

EP2C5T144C8-FPGA开发板采用Altera公司推出的CYCLONEⅡ系列芯片EP2C5T144C8芯片作为核心处理器进行设计,CYCLONEⅡ系列芯片可以说是目前市场上性价比较高的芯片,比第一代的EP1C6或者EP1C12等芯片

2011-12-06 10:24:54 671

671 本开发板采用 Altera 公司CycloneII 系列EP2C8Q208 芯片而设计的。帮助用户降低学习成本和加快用户快速进入可编程逻辑器件的设计开发领域。提供一个帮助用户快速学习可编程逻辑器件的硬

2011-12-06 10:29:14 799

799 文章以T6963C控制的240×128LCD液晶显示屏模块阐述了一种基于EP1C6Q240C8处理器的液晶显示屏的滚屏显示的软硬件控制方法。

2012-02-28 10:33:51 2570

2570 介绍一种基于SOPC的基本信号产生器的设计技术,以Altera公司EP1C6Q240C8为硬件核心,把软核CPU嵌入到FPGA之中构成片上系统(SOPC),并结合存储电路、高速DAC电路、LCD电路、键盘电路、JTAG配置电路

2012-03-09 14:55:15 14

14 开发板EP1C6Q240C6开发板原理图

2017-03-20 08:00:00 26

26 开发板EP1C3T144_FPGA_develop_board_manual

2017-03-20 11:38:00 32

32 EP4CE6E22C8N开发板原理图

2017-04-22 09:11:44 890

890 本文档的主要内容详细介绍的是FPGA EP1C3开发板原理图的详细资料免费下载。

2018-09-26 16:35:00 63

63 设计和实现了一个以Altera FPGA的Cyclone器件EP1C6Q240C8为核心的多功能实验板。它分为核心板和扩展板, 用户可以结合QuartusII集成开发环境, 使用VHDL语言

2018-11-16 16:48:05 8

8 3T144 FPGA开发板手册,EP1C6Q240C6开发板原理图,EP2C5原理图,EP2C8开发板原理图,EPM1270F256C5 MAX II板示意图,EPM7128最小系统,MAX7000等等。

2019-03-04 08:00:00 91

91 本文档的主要内容详细介绍的是FPGA视频教程之使用SF-EP1C开发板实现DIY数码相框的实验资料说明。

2019-03-06 14:02:07 4

4 本视频的主要内容详细介绍的是FPGA视频教程之SF-EP1C开发板256色VGA显示实验的详细资料说明。

2019-03-07 14:53:55 3658

3658 SF-EP1C开发板有着比较丰富的外设,也给用户预留了一些可扩展的接口。FPGA使用EP1C3T144C8,硬件电路充分考虑了可升级性,该板子同样适用于EP1C6T144。

2019-12-16 07:04:00 2662

2662

1、FPGA使用EP1C3T144C8,硬件电路充分考虑了可升级性,该板子同样适用于EP1C6T144

2019-12-12 07:10:00 3502

3502

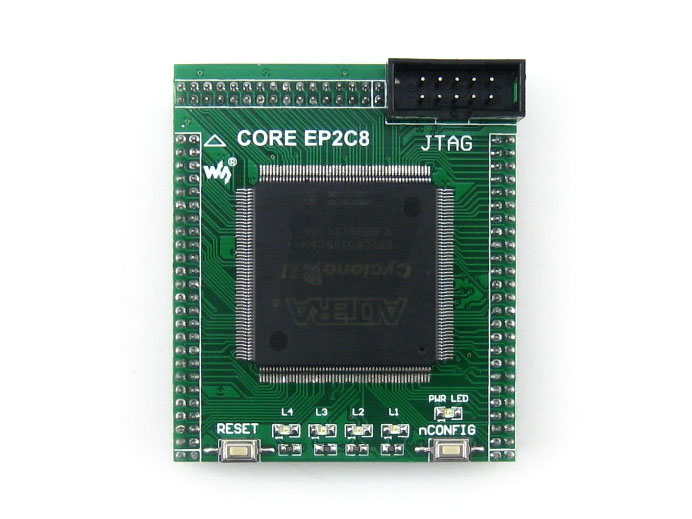

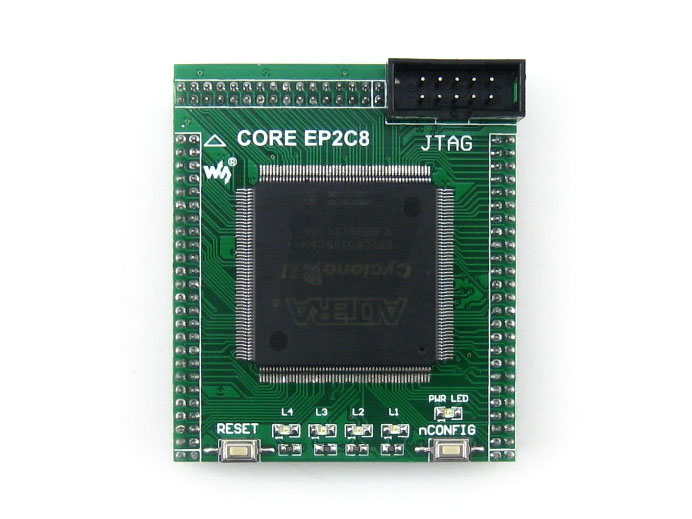

CoreEP2C8是一款基于EP2C8Q208C8N为主控芯片的核心板

2019-12-19 14:26:33 3126

3126

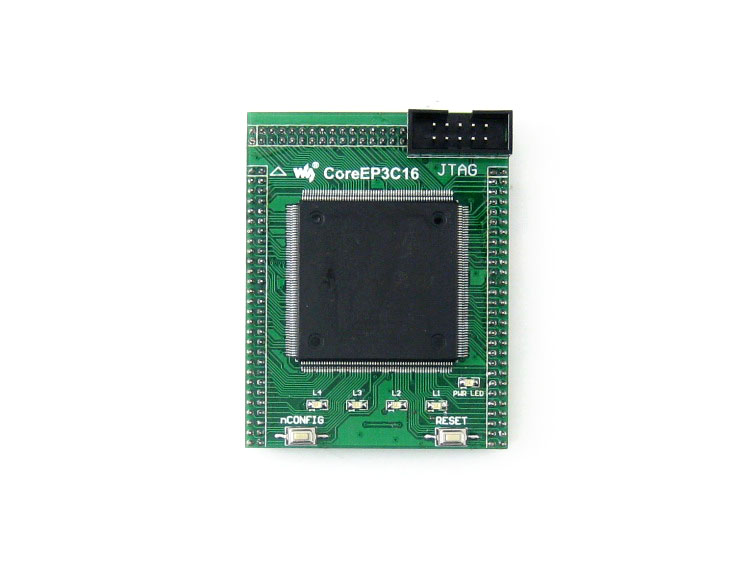

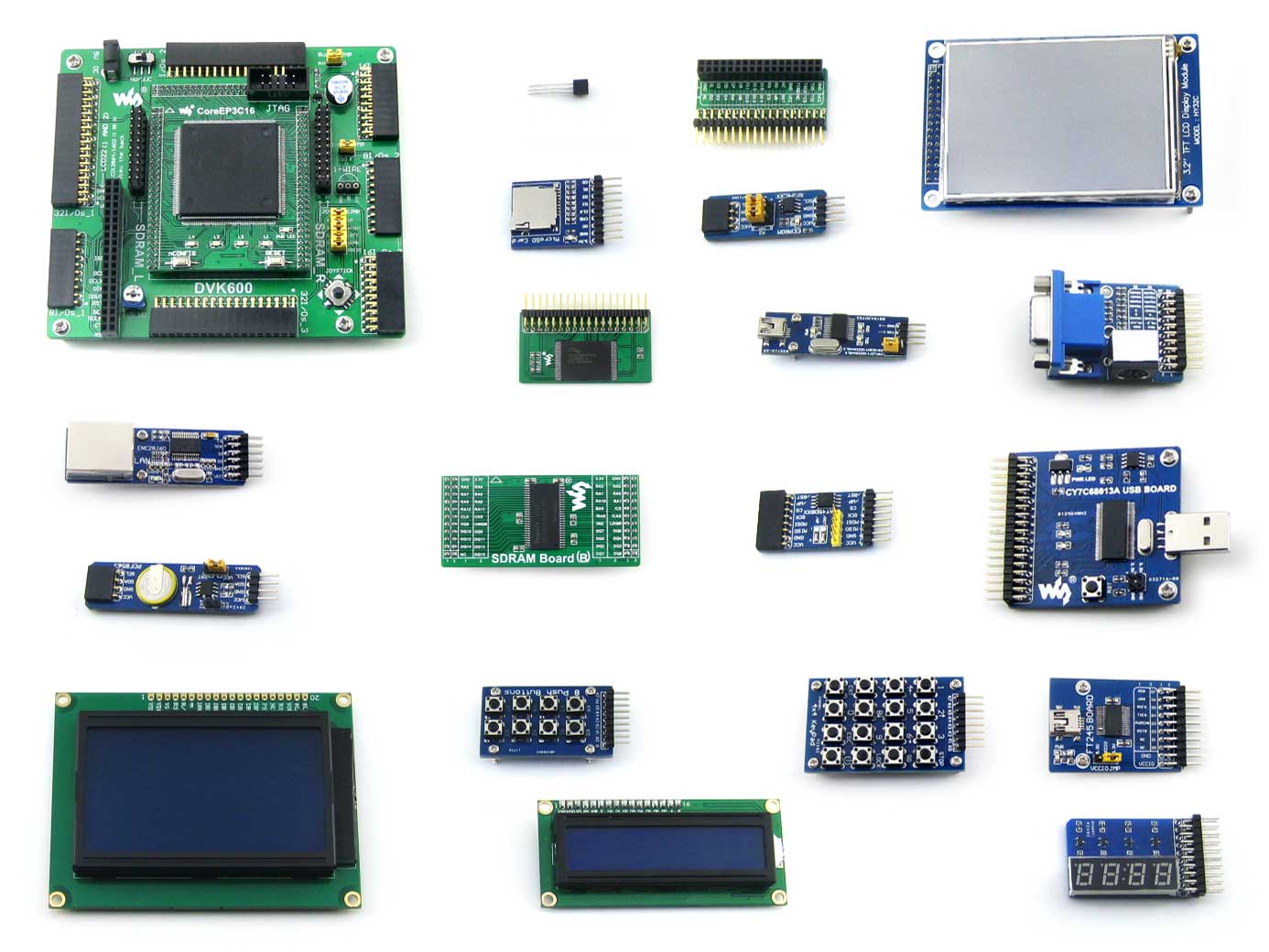

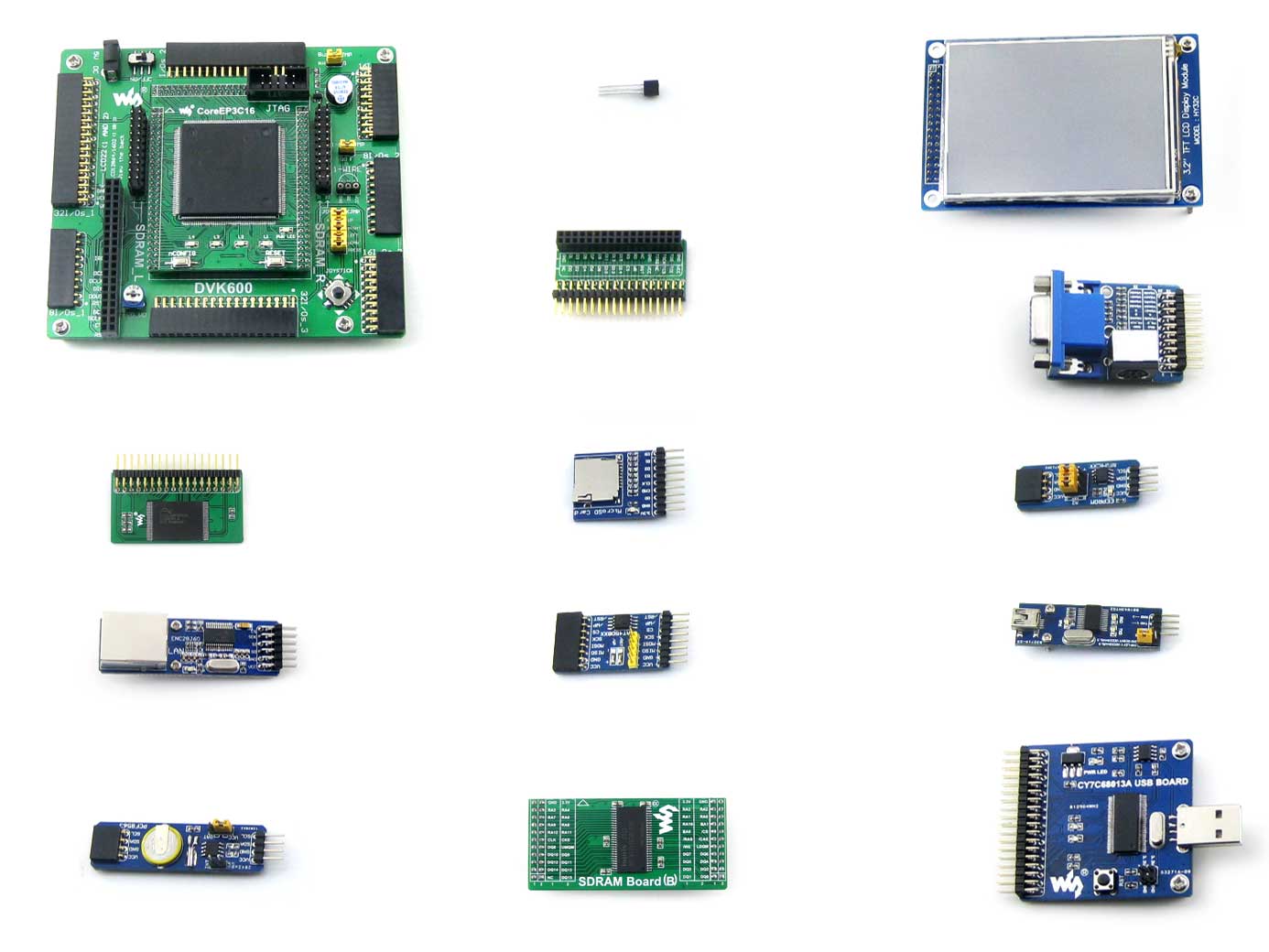

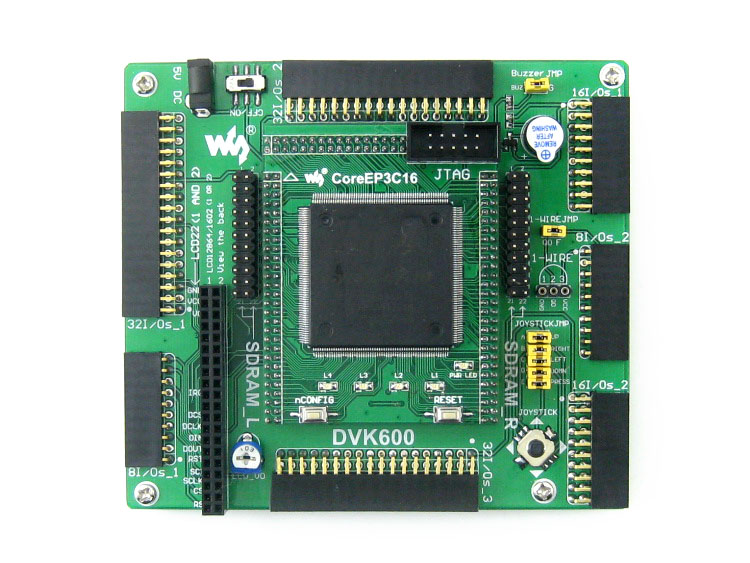

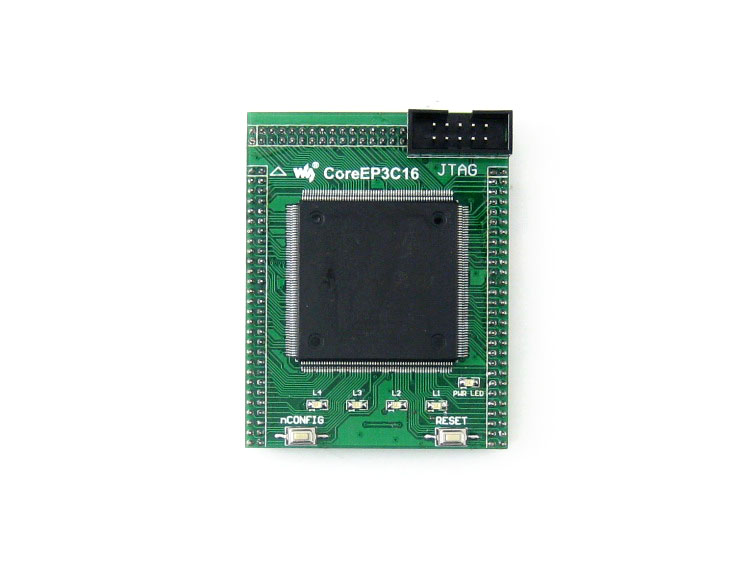

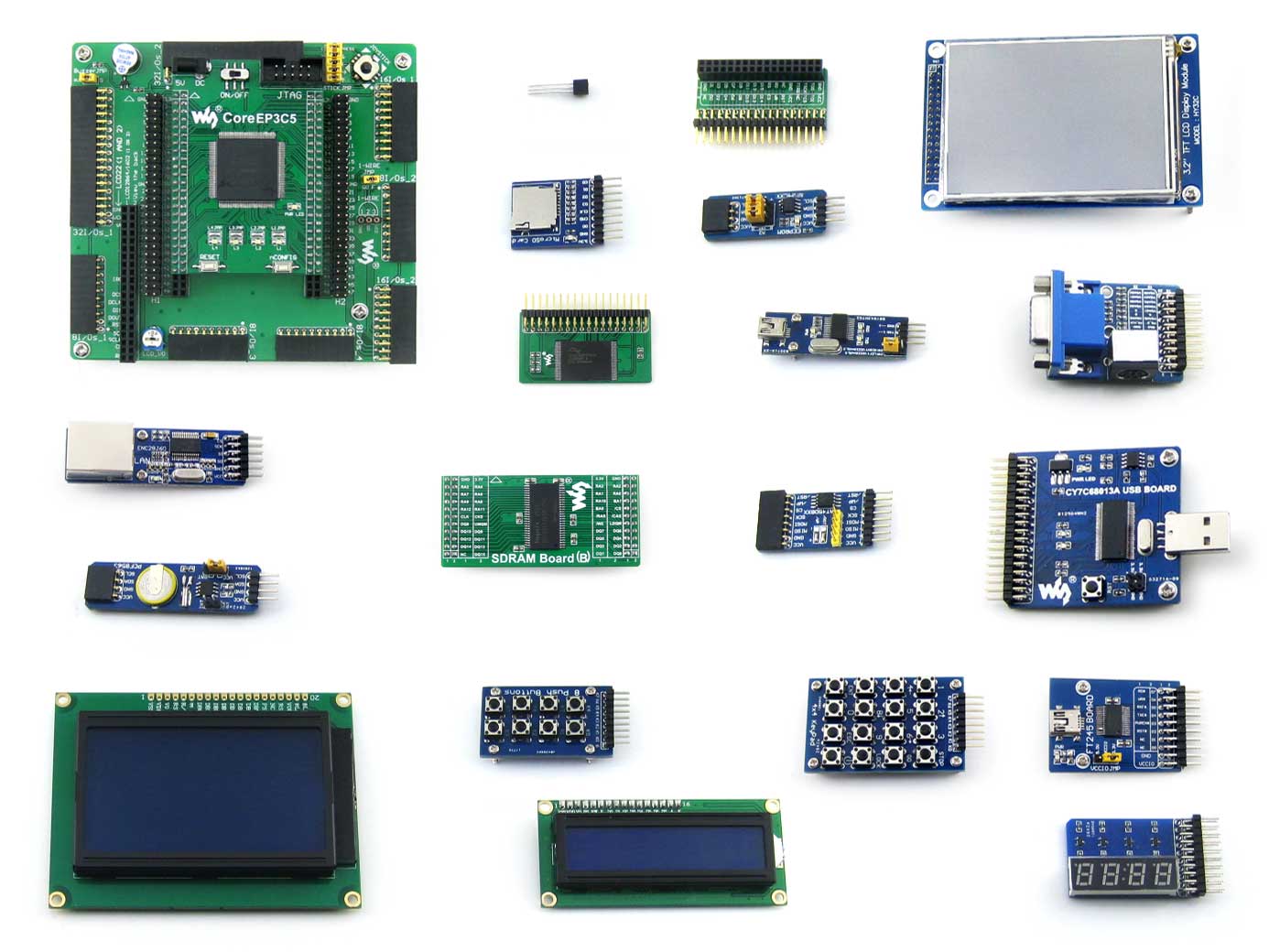

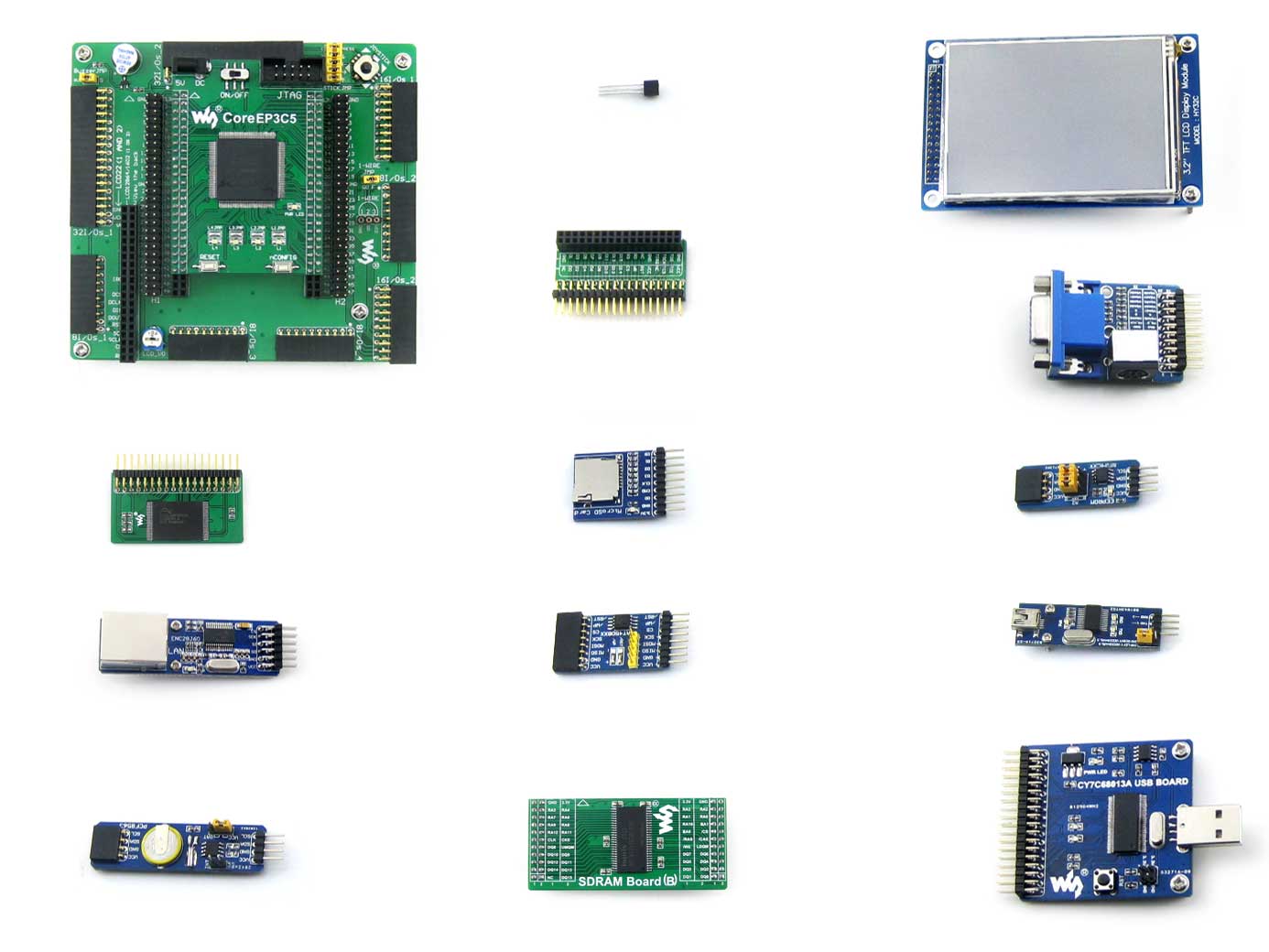

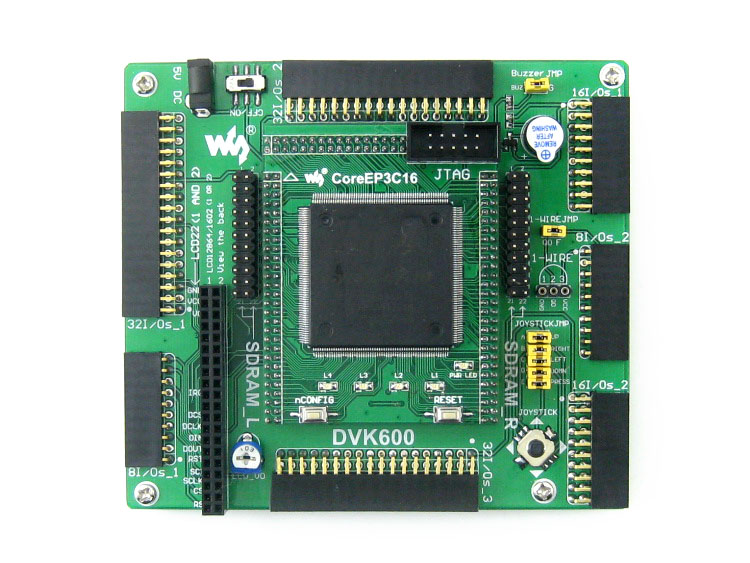

EP3C16Q240C8N 核心板 最小系统板

引出了所有I/O资源 带JTAG调试下载接口

型号 CoreEP3C16

2019-12-19 14:29:36 2496

2496

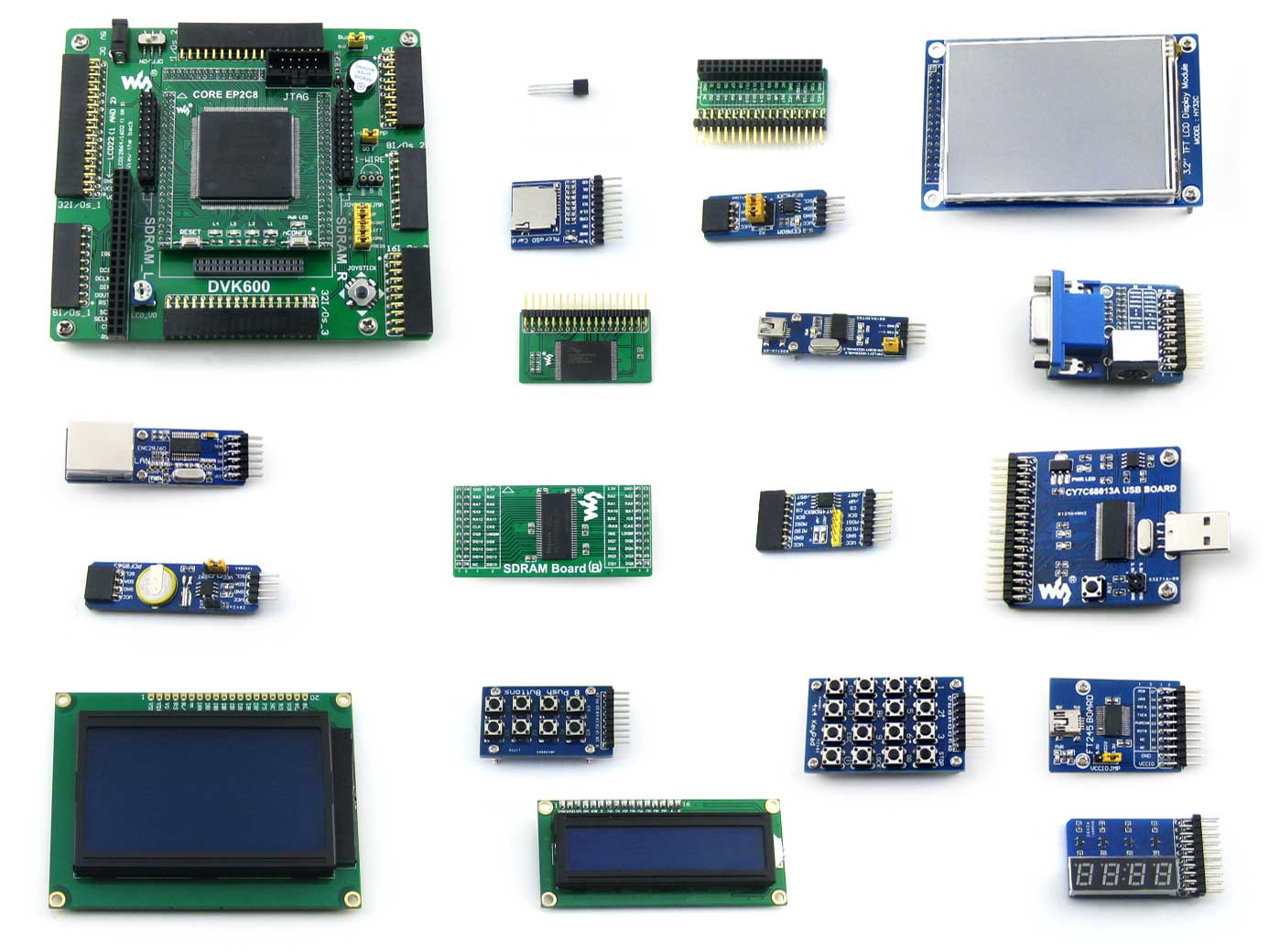

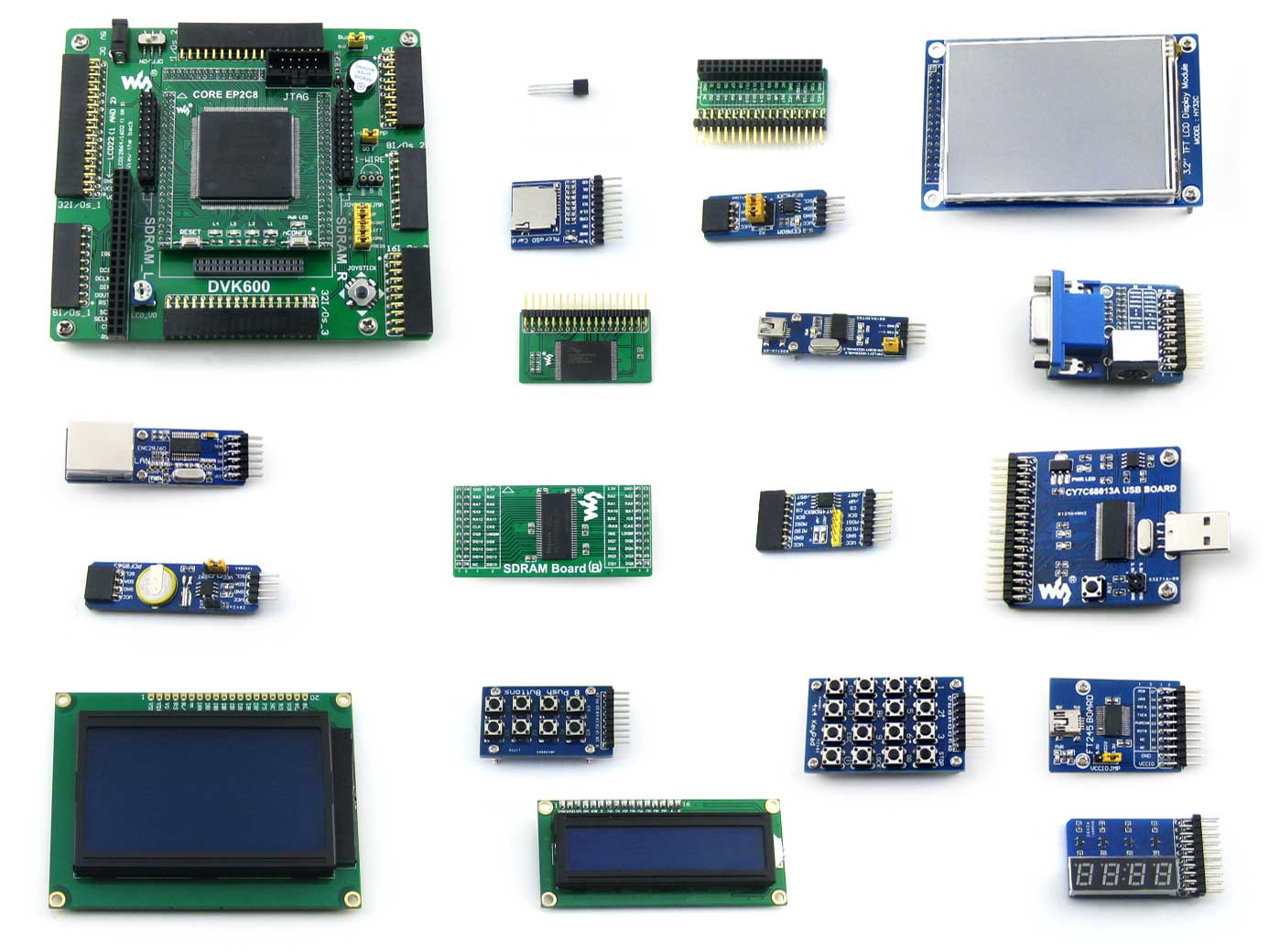

EP2C8Q208C8N开发板 学习板 套餐B 含18款模块

引出常用接口,含LCD、串口、按键、USB通信等模块

型号 OpenEP2C8-C (套餐B)

2019-12-20 15:04:27 2564

2564

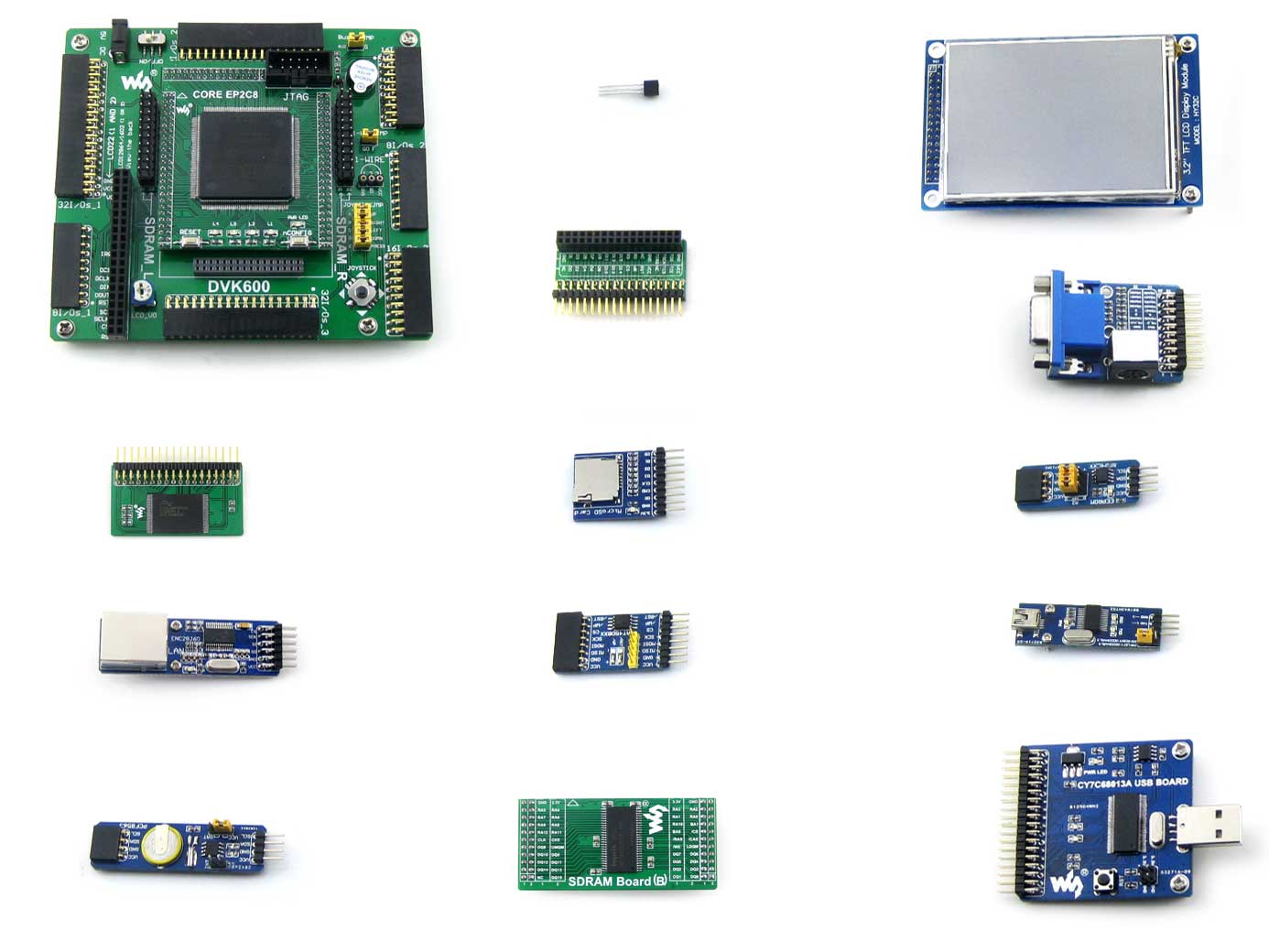

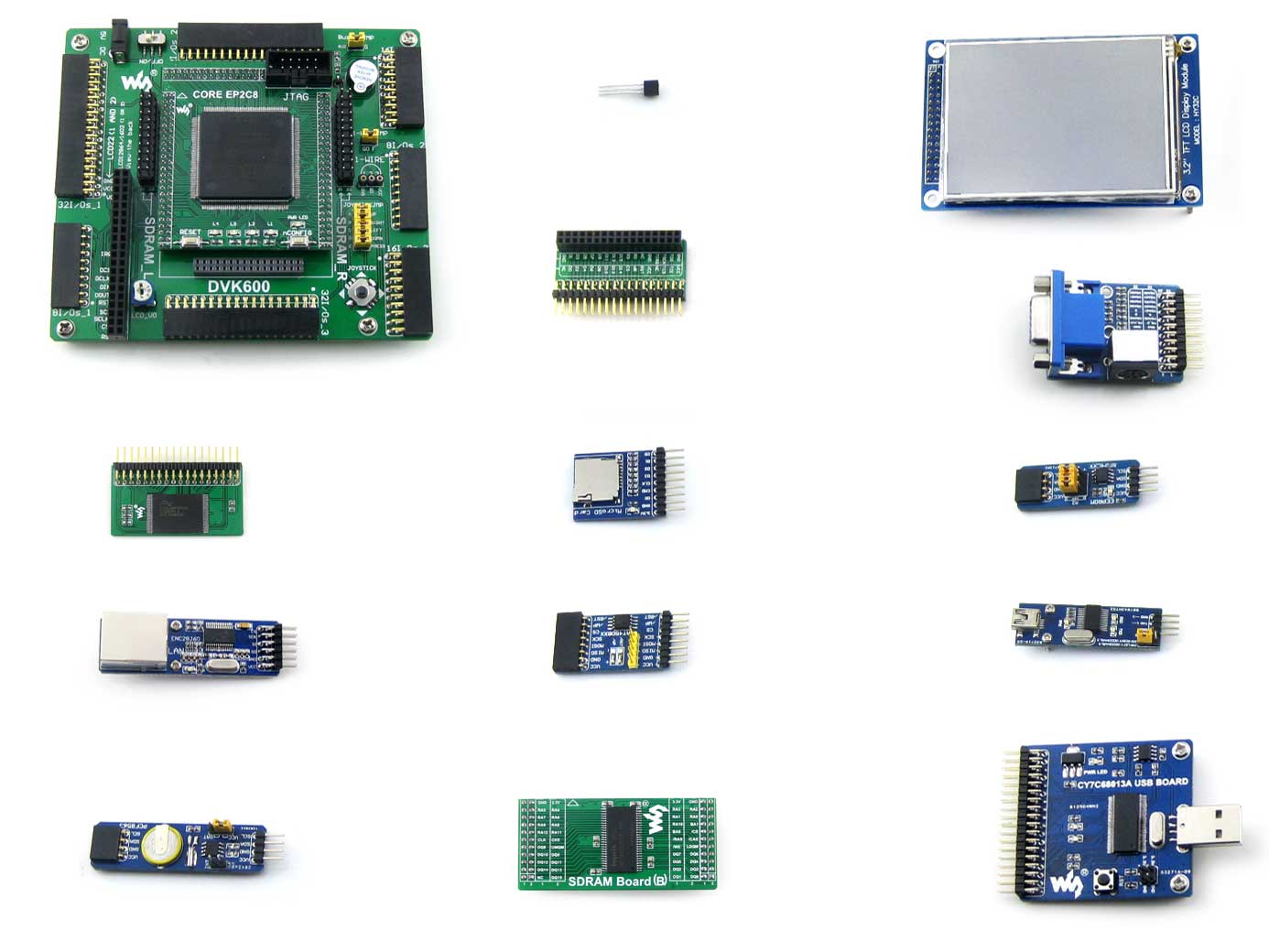

EP2C8Q208C8N开发板 学习板 套餐A 含12款模块

引出常用接口,含LCD、串口、按键、USB通信等模块

型号 OpenEP2C8-C (套餐A)

2019-12-20 15:14:19 2342

2342

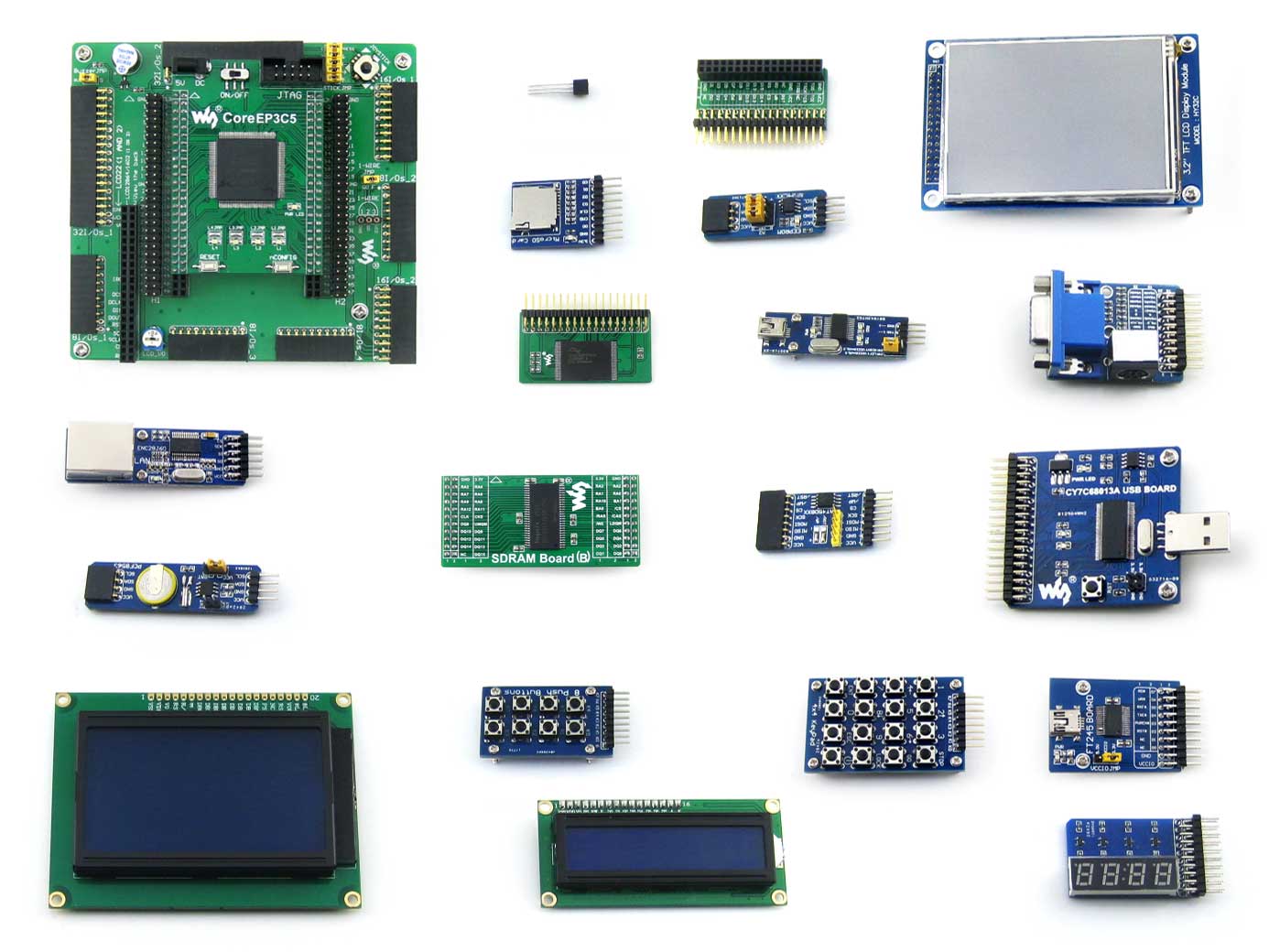

,包括实用新型专利及外观专利,仿造必追究其法律责任! FPGA开发板OpenEP3C5-C是一块以Cyclone III EP3C5为主控芯片的开发板,它带有丰富的扩展接口,支持各类外围模块的接入

2019-12-23 11:23:08 2483

2483

FPGA开发板OpenEP3C5-C是一块以Cyclone III EP3C5为主控芯片的开发板,它带有丰富的扩展接口,支持各类外围模块的接入。

2019-12-23 11:30:13 1776

1776

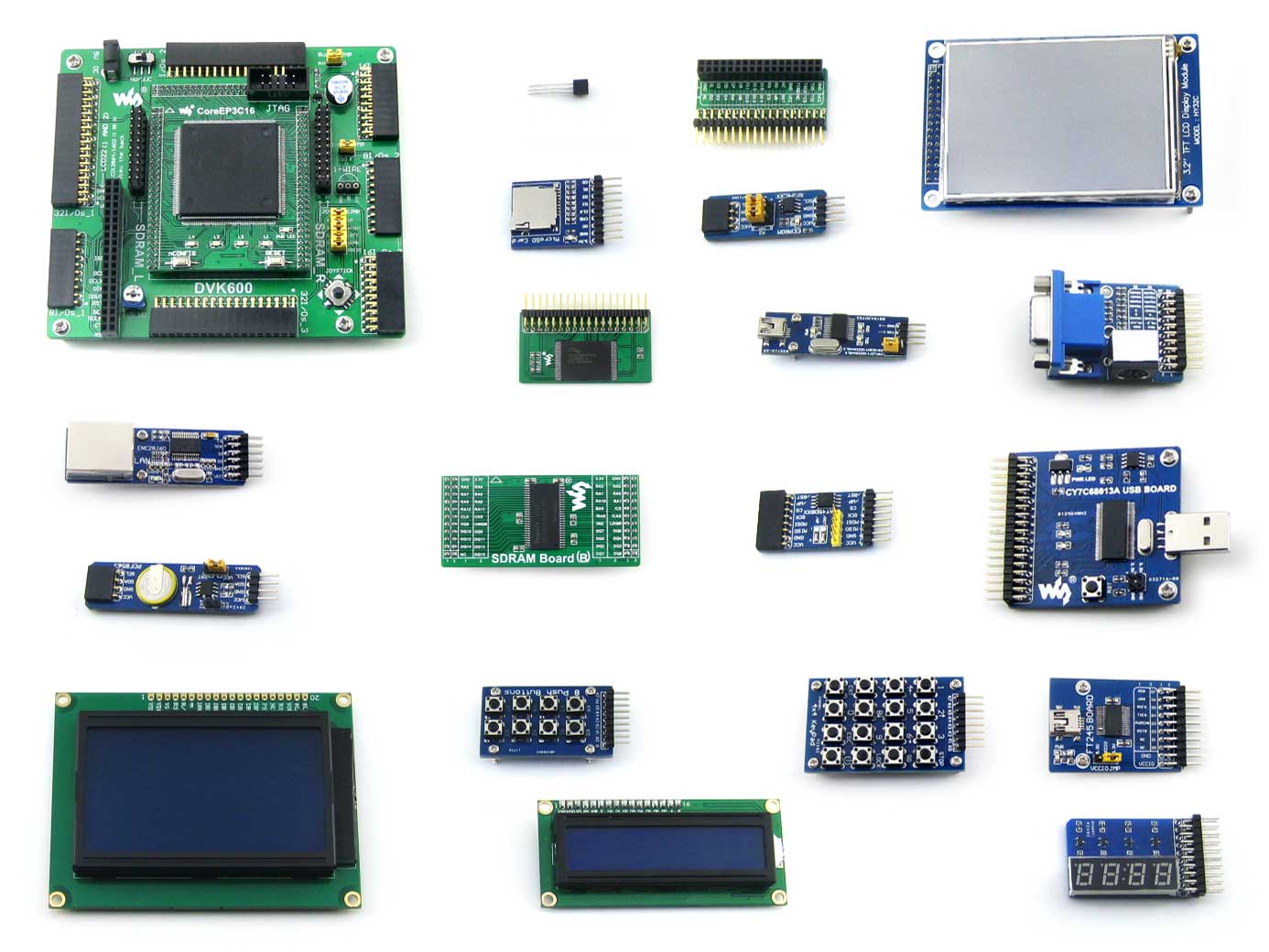

EP3C16Q240C8N开发板 学习板 套餐B 含18款模块

引出常用接口,含LCD、串口、按键、USB通信等模块

型号 OpenEP3C16-C (套餐B)

2019-12-23 11:32:24 1908

1908

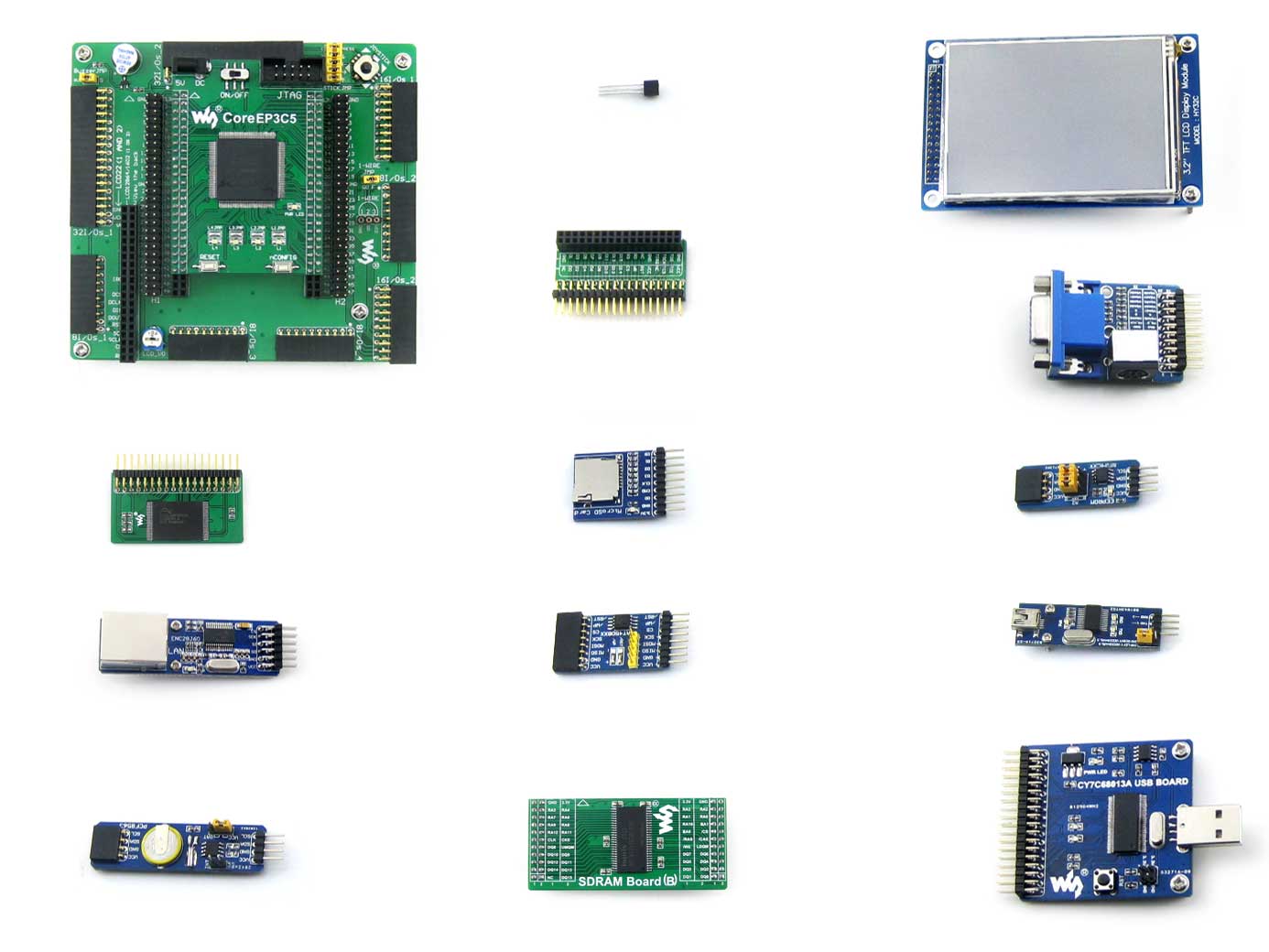

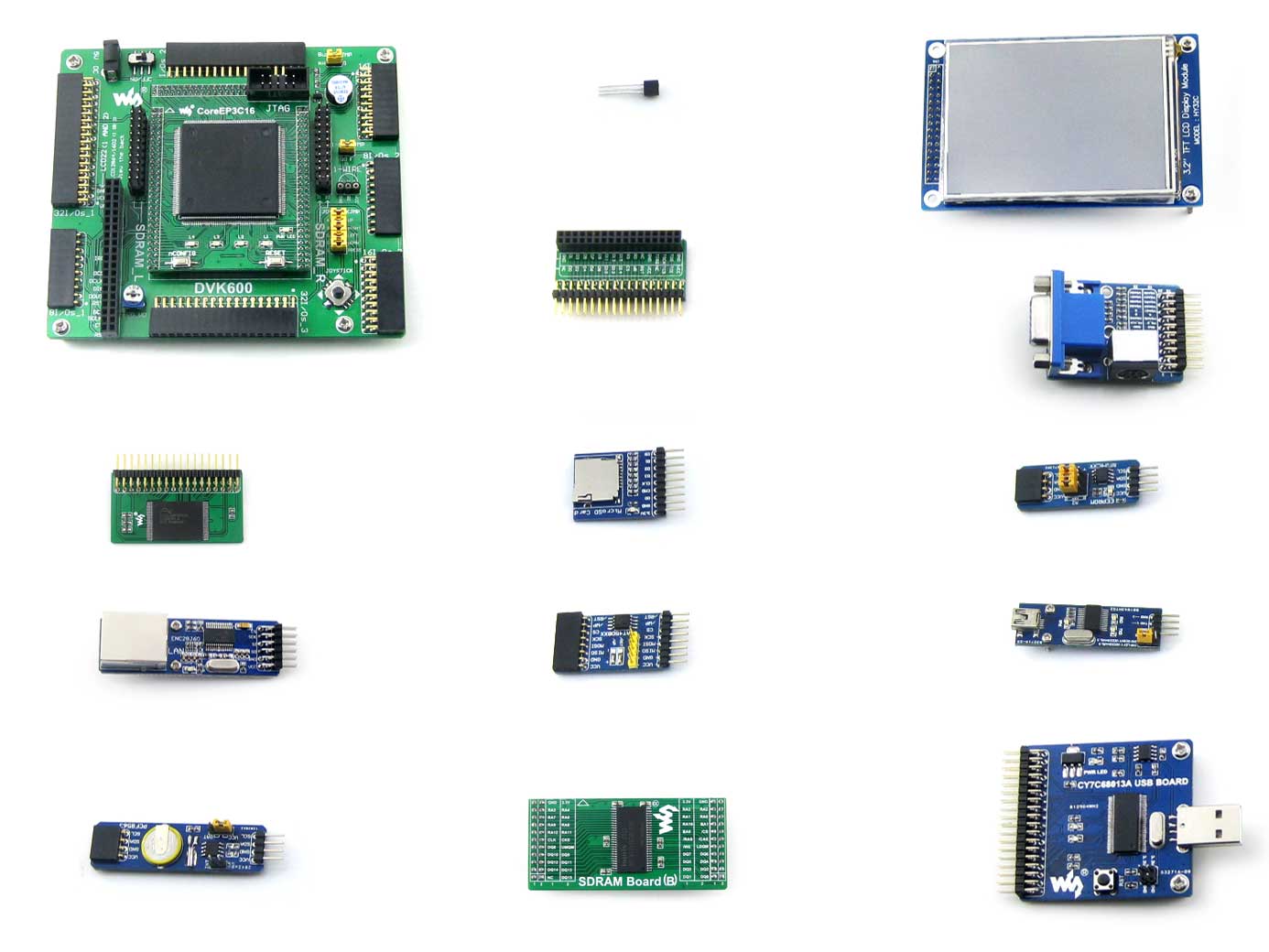

EP3C16Q240C8N开发板 学习板 套餐A 含12款模块

引出常用接口,含LCD、串口、按键、USB通信等模块

型号 OpenEP3C16-C (套餐A)

2019-12-23 11:28:08 2065

2065

EP2C8Q208C8N开发板 学习板 核心板 标准版本 引出常用接口,可接微雪外围模块 型号 OpenEP2C8-C (标准版) FPGA开发板OpenEP2C8-C是一块以Cyclone II

2019-12-23 14:17:24 2878

2878

FPGA开发板OpenEP3C16-C是一块以Cyclone III EP3C16Q240C8N为主控芯片的开发板,它带有丰富的扩展接口,支持各类外围模块的接入。

2019-12-23 14:26:41 2004

2004

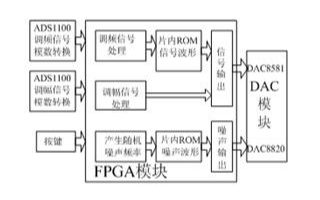

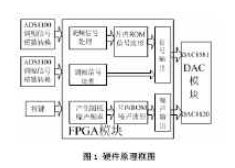

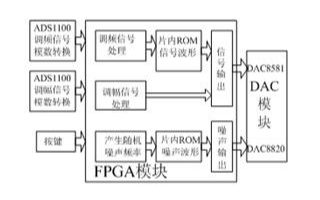

利用FPGA开发振动模拟器研制开发费用低,不承担投片风险,通过开发工具在计算机上完成设计,电路设计周期短。所以本文采用FPGA实现振动模拟器设计,由ADC模块接收调频和调幅信号,传给FPGA模块

2020-08-05 14:29:16 1694

1694

振动模拟器的原理框图如图1所示,图中由ADC模块分别接收调频和调幅信号给FPGA模块,FPGA模块将串行的调频和调幅信号,经串并转换,分别变成一个16位的并行调频信号和一个16位的并行调幅信号

2020-08-06 17:42:11 2724

2724

传统的运动控制卡多采用单片机作为微处理器, 通过一些大规模集成电路实现对伺服电机的控制。由于其结构较为复杂,因此在工作时,存在高频响应慢、控制精度低等缺点。本文提出一种以FPGA

2020-08-12 17:02:03 2814

2814

,进而用FPGA和D/A转换器进行硬件实现。文中基于FPGA对长度为10000m,特性阻抗为55Q的同轴电缆进行了仿真线的硬件实现,实验结果验证了该方法的有效性。该方法可以推广到传递函数未知的传输网络的仿真应用中。

2021-02-03 16:26:00 14

14 基于FPGA的RBF神经网络硬件实现说明。

2021-04-28 11:24:23 27

27 基于FPGA的神经网络硬件实现方法说明。

2021-06-01 09:35:16 51

51 FPGA开发板EP4CE22F17C8原理图及封装

2021-08-10 09:31:21 183

183 电子发烧友网站提供《基于FPGA的RBF神经网络的硬件实现.pdf》资料免费下载

2023-10-23 10:21:25 0

0 可编程门阵列(FPGA)作为一种灵活、高效的硬件实现方式,为神经网络的加速提供了新的思路。本文将从FPGA实现神经网络的基本原理、关键技术、实现流程以及应用前景等方面进行详细阐述。

2024-07-10 17:01:42 4397

4397 今天我们分享几个用FPGA实现的小型神经网络,侧重应用。

2024-07-24 09:30:16 2389

2389

电子发烧友App

电子发烧友App

评论