完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

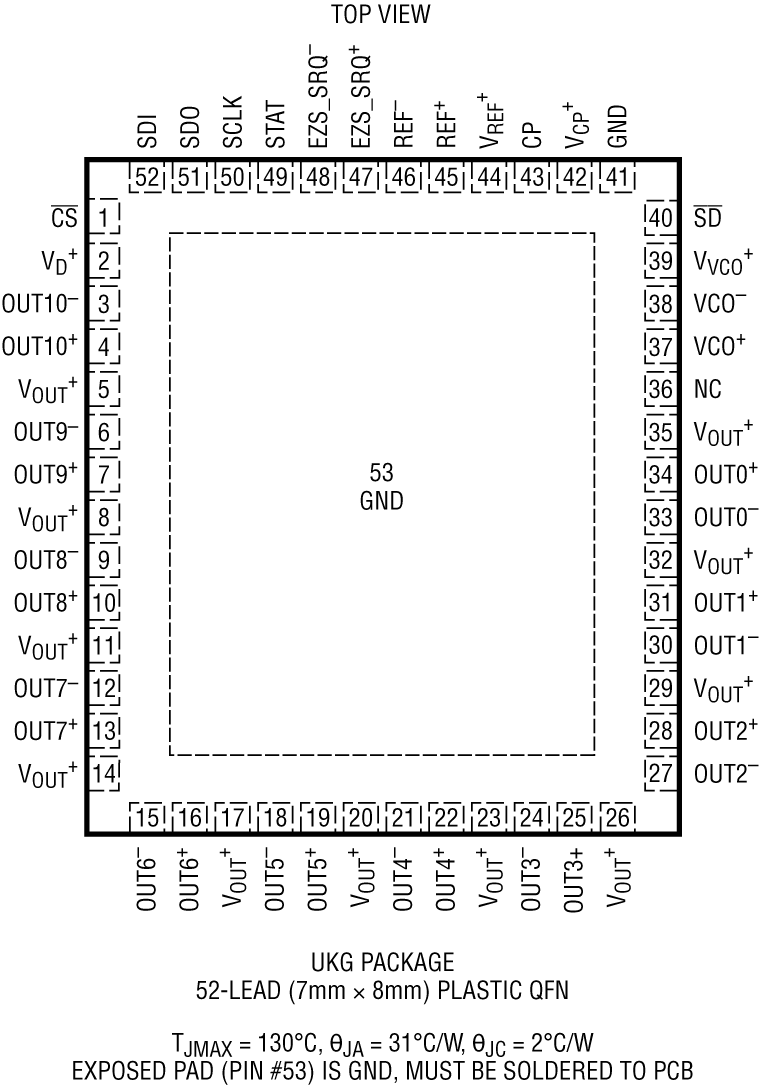

LTC6952 是一款高性能超低抖动的 JESD204B/C 时钟生成和分配 IC。它包括一个锁相环 (PLL) 内核,由基准分频器、具有锁相指示器的相位频率检波器 (PFD)、超低噪声电荷泵和整数反馈分频器构成。LTC6952 的 11 个输出可配置为最多 5 个 JESD204B/C 子类 1 器件时钟/SYSREF 对以及一个通用输出,或简单的 11 个通用时钟输出,用于非 JESD204B/C 应用。每个输出都有自己的可单独编程的分频器和输出驱动器。所有输出也可以通过单独的粗半周数字延迟和精细模拟时间延迟进行同步,并设置为精确的相位对齐。

对于需要 11 个以上总输出的应用,可以使用 EZSync 或 ParallelSync 同步协议将多个 LTC6952 连接在一起。