在FPGA调试过程中,除了逻辑代码本身的质量之外,FPGA板子上PCB走线、接插件质量等因素的影响也非常重要。在刚上板调试不顺利的时候,不妨拿示波器看一下信号的质量,比如时钟信号的质量、差分信号

2020-11-20 12:11:30 4454

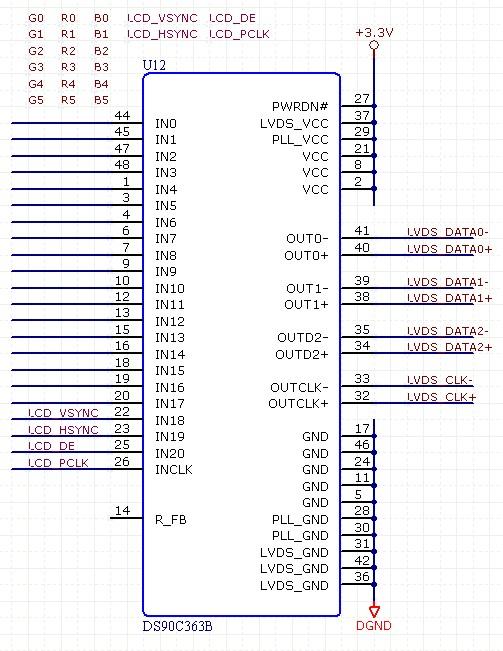

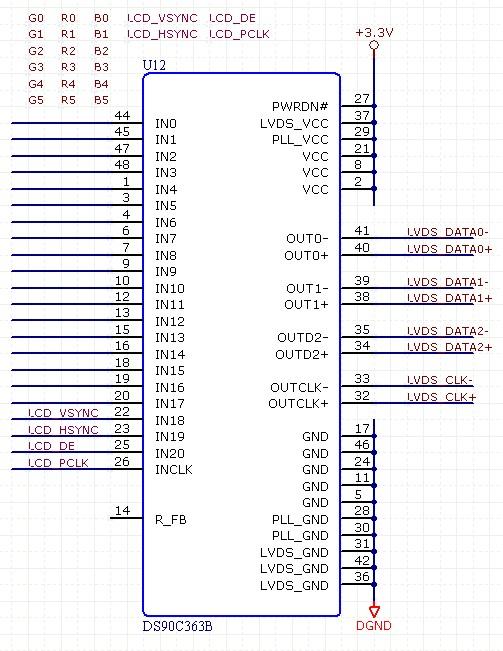

4454 这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。此,也称18位或18bit LVDS接口。

2023-03-28 11:46:23 2931

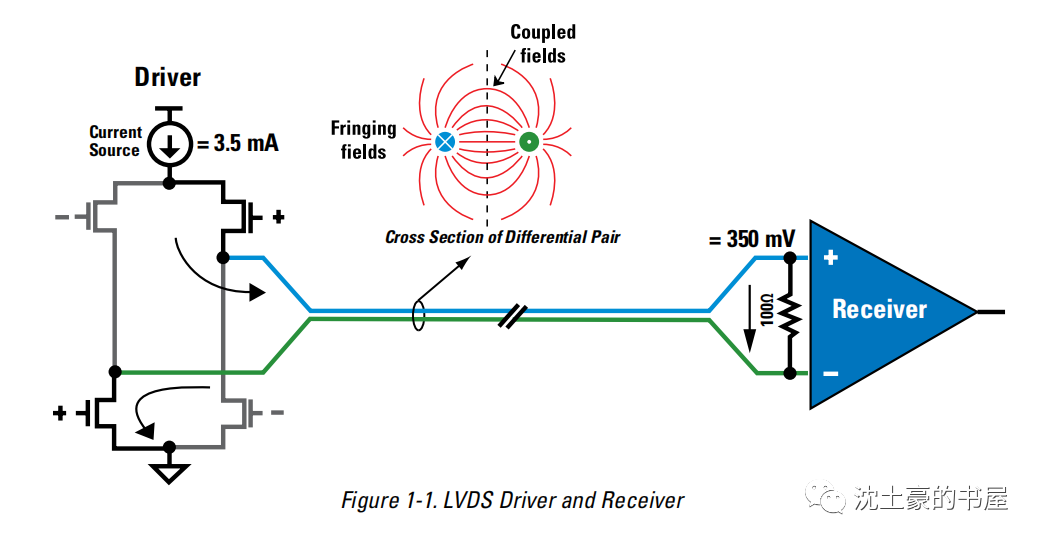

2931 LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

2023-10-02 16:44:00 589

589

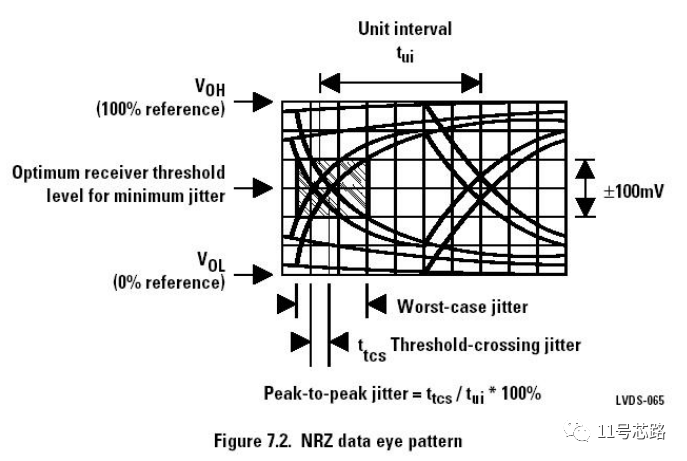

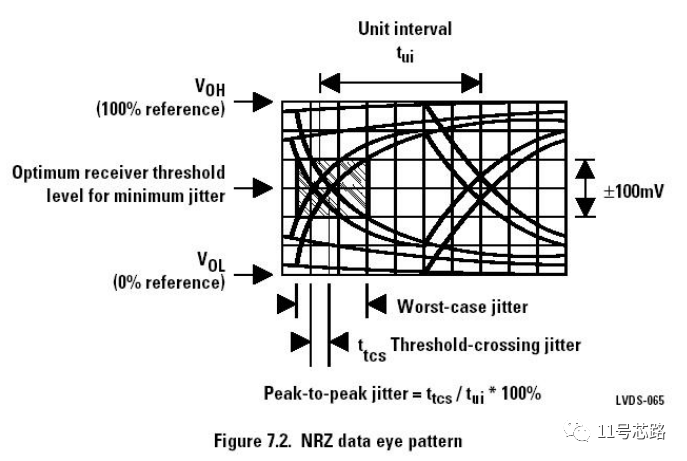

示波器屏幕上看到的图形就称为眼图。示波器一般测量的信号是一些位或某一段时间的波形,更多的反映的是细节信息,而眼图则反映的是链路上传输的所有数字信号的整体特征。观察眼图的方法是:用一个示波器跨接在接收

2020-03-02 18:19:16

最近接手一个LVDS信号转接板制作的任务,本人对于设计高频layout一点都不懂,完全是小白的概念,查了些资料了解LVDS要设计特性阻抗,知道了LVDS特性阻抗为100Ω,首先说明一下情况,信号

2018-12-16 16:55:27

本帖最后由 eehome 于 *** 编辑

我的单色屏,视频信号是LVDS现在我换成了彩屏,彩屏仅支持AV输入我想在彩屏上显示以前单色屏的内容所以就得把LVDS信号转为AV信号求大神帮忙啊!!!

2012-09-23 13:44:52

请教大家, 怎么样测量LVDS的具体定义。 在没有屏规格书,并不知道这5组LVDS那组是什么信号,且哪个是+ -信号, 我们应该怎么去测量, 首先时钟我们可以测量出来,那么其他4组怎么去区分D0+

2015-10-10 15:23:27

你好,我一直试图在论坛中找到对我的怀疑的答案,但我找不到确切的答案。我们目前正在为VC709开发套件设计FMC扩展板,我有几个问题:1.我们需要使用差分(LVDS)和单端信号(3.3V)。两种信号

2019-09-20 11:56:39

用什么方式能够做双路LVDS信号的切换,损耗最小

2023-05-15 16:49:33

LVDS:Low-Voltage Differential Signaling 低电压差分信号。一种信号传输模式,是一种电平标准,LVDS接口又称RS-644总线接口,是一种数据传输和接口

2016-04-15 16:13:33

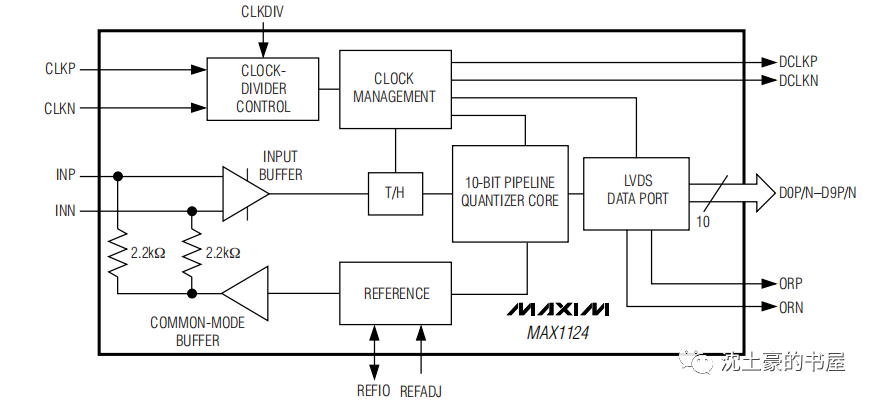

LVDS接口常常与控制和调节系统一起使用,大数据量必须在电子电路之间或短电缆之间发送。它还能将时钟信号非常快速地 分配给完整应用中的不同器件,从而使相应器件同步。工业测量应用和控制系统中的模拟前端

2019-08-02 07:16:56

看到的图形就称为眼图。示波器一般测量的信号是一些位或某一段时间的波形,更多的反映的是细节信息,而眼图则反映的是链路上传输的所有数字信号的整体特征。如果示波器的整个显示屏幕宽度为100ns,则表示在

2020-09-25 11:54:26

,但是在线径粗细发生变化的时候,会发生一些反射的现象。拐角方式对于线的粗细变化情况,直角是最差的,45度角好一些,圆角是最好的。但是圆角对PCB设计来讲处理比较麻烦,所以一般是看信号的敏感程度来定,一

2018-09-18 15:55:57

老师给的一些应用实例

2013-08-13 10:04:05

最近用到的一些东西,分享一下!

2014-06-15 11:32:28

眼图及眼图在信号测试中的运用

2015-05-21 23:42:52

本文介绍了什么是眼图,眼图是如何构建的,触发是生成眼图的一个共同方法。然后描述了使用不同的方式切割眼图,可以获得更多深入的信息。同时还讨论了一些发射机、传输链路和接收机测试的基本方法。本文的目的是为了工程师掌握眼图这个新领域的基本概念。

2019-07-12 07:30:00

眼图测试测试项目: >消光比>眼交叉比>信号上升时间与下降时间>Q因子(Q Factor)>平均功率>抖动测试环境: 在实时示波器中通常使用连续比特位的眼图生成

2019-10-10 14:36:04

华为编写的介绍眼图基本知识的资料,介绍如何从眼图的中看出一些量化的数据如信号的上升、下降时间、交叉点位置、消光比、Q因子、信噪比、抖动等,以及如何从各个方面来衡量一个眼图的优劣。

2012-08-02 15:14:23

本帖最后由 sdf1994 于 2014-10-25 23:02 编辑

这是关于Arduino的一些教程

2014-10-25 22:55:23

各位大神,小弟这边先谢过了,真的很急!目前我需要使用FPGA技术来处理一款1对时钟LVDS信号和8对数据LVDS信号摄像头模组,我这边只能对并口信号和MIPI信号输出的摄像头模组进行测试调焦,对于LVDS信号的模组没有相关技术,请大神帮忙啊!!!非常感谢!!!可付报酬!!!

2014-07-17 16:40:58

亲爱的Xilinx人,我有一些简单的问题要问。我正在使用Virtex 6 SX475T进行PCB设计。我正在考虑添加一个扩展端口,它有2对CML和6对LVDS信号。从用户指南,我认为一个GTX银行

2020-06-13 08:38:27

:Android 12-1.0.0

内核:5.10.72

另外,我们并没有直接从SOC端(通过USB-HUB)连接到USB主机连接器,那么IMX8是否支持 眼图测试的一致性模式?

我找到了一些关于 USB 眼图的文档,但无法下载,如果有人能提供正确的文档链接,我将不胜感激。

2023-05-04 06:00:08

一些资料,希望可以帮到你们

2016-06-24 23:50:45

SI工程师给出的约束规则来完成布局布线的,这些也就是俗称的“拉线工”。他们重复而机械的完成一块块PCB设计,一段时间设计后,他们中的一些或许已经有了这样的一些经验:哪些要做等长,哪些要走粗、哪些要平行

2016-12-20 17:34:18

以下是USB底层信号的一些定义及时序图,虽然很简洁,但能理解后,对后续的USB学习是很有帮助的,特推荐给大家!BTW,本月(4月20号周六)在深圳有一场很接地气、很容易入门的USB线下、小型技术交流

2019-04-08 16:30:26

本帖最后由 912293097 于 2012-10-25 21:58 编辑

分享一些avr的一些资料

2012-10-25 21:54:52

labview的一些文章

2012-05-26 21:43:40

labview的一些文章

2012-09-24 17:44:36

,各种电子产品的PCB设计,积累了非常多的一些经验,对于一些电子工程师来说,可以起到一个借鉴和参考的作用,也希望下面的一些经验或者技巧能够帮助电子工程师在产品的设计中应对PCB设计面临的各种挑战

2012-04-27 16:01:01

的周期同步,这时示波器屏幕上看到的图形就称为眼图。示波器一般测量的信号是一些位或某一段时间的波形,更多的反映的是细节信息,而眼图则反映的是链路上传输的所有数字信号的整体特征。 3、眼图和实时波形的区别

2019-07-12 05:00:00

作为仪器厂商目前唯一支持的。 8、快速眼图的测量 (一键式眼图测量) 当我们需要测量眼图时,需要先进行一系列的设置后才能形成波形的眼图,比如波形的大小调整、信号速率的设定以及阈值的设定等。对于一些

2019-07-12 05:30:00

值抖动或截至目前所测得的时间间隔误差 (TIE)(比较图3所示的眼图和直方图)。有一些抖动是随机图3. ADN4651的眼图和直方图相比之下,确定性抖动(DJ)的为了完整地估算特定误码率下的总抖动

2018-10-30 14:44:43

纯当作一个开关器件来看,会出现许多问题。在这里总一下问题和对出现问题的一些原因做一些分析。个人知识有限,很多地方思虑难免有所不足,希望能够与网上各位一起学习交流。目前我们一般将H桥驱动当作电机或步进

2021-09-13 08:14:12

可靠地采集数据。2. 常用术语在数字电路系统中,定时是最重要的因素之一。 数字通信的可靠性和精确度均取决于定时的质量。 然而,在实际应用中,任何事物都不是理想的。 以下是一些可以帮助您理解特定数字信号

2019-06-12 08:00:00

安川伺服调试的一些经验在查找惯量比的过程中看到的,这是伺服电机的驱动过程中发生的问题,首先应当匹配惯量,伺服电机应当考虑刚性,还有速度,速度高,惯量还会大。再生电阻还是不知道怎么配置。 安川伺服调试的一些经验: 1、 安川伺服在低刚性(1~4)负载应用时,惯量比显得非常重要,以同步带结构而论

2021-09-07 08:05:06

嗨, 我计划在我的设计中使用SERDES(LVDS)作为背板。我已经浏览了virtex5用户指南中的advnced IO部分,并看过ISERDES_NODELAY和OSERDES宏。我已经看到了一些

2020-07-13 15:54:49

本人最近在做一个项目,从核心板出单8路的LVDS信号,意图转成VGA信号,直接输出到显示器上。请问大家有没有什么好的方案提供。谢谢各位了,好心人总会有好回报的。LVDS频率是50HZ,最高支持1280*800.

2017-07-10 11:37:32

BANK VCCIO为2.5V,下载后,分别测出两个差分引脚的电压波形,奇怪的是两个引脚的电平不满足LVDS的电平范围(1.0v-1.4v),而且两个信号的VPP幅值还不一样,一个是2.95一个是2.0

2018-04-03 18:39:33

1、rk3288点亮lvds屏幕之前有点亮过23.6寸的双8液晶屏,这次手上刚好有块10.1寸屏幕,记录一下过程。屏幕的型号。修改firefly-rk3288.dts 设备树信息一个通道,16.7M=2^24,即r,g,b各8位信号宽度原作者:风见暗含

2022-05-11 14:16:02

1、怎样学习使用Altium Designer、Proteus、Keil等与电子相关的一些软件?是看指导书好,还是看视频教程好?有没有必要全面熟悉所有功能的实现方法,还是熟悉常用的一些功能就好?2

2013-08-28 12:36:25

芯片的,不知有无错误?如下图:3. 想问下工程师是否可以给我们一些有益的建议呢,非常感谢! 请工程师指点,非常感谢!

2019-05-22 07:26:16

分享一些资料

2019-03-13 17:31:05

fofa,钟馗之眼,shodan等等一系列的公网设备搜索引擎,其中fofa和shodan使用的最多,本文就来整理一些shodan的搜索语法Shodan:www.shodan.ioPs:均来自互联网

2021-07-12 06:33:01

分享一些实例,免得大家不好找

2014-07-15 15:32:37

的内部驱动器和接收器是否足够?另外,我应该使用一些电线作为从一个电路板到另一个电路板的接地,还是没有必要,因为lvds信号是相互参照的?最后,在设计中我是否应该采取任何其他预防措施(除了通常的阻抗匹配

2019-06-24 15:44:23

的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种

2019-07-29 07:03:50

`基于labview的信号采集于分析系统的一些资料`

2015-03-23 16:33:36

你好,我正在尝试生成LVDS信号。在代码中我使用PS的1Mhz时钟。但是有一些时间问题。我不知道如何解决它。体系结构TDC_EvaluationSignal的行为是signal

2020-05-07 09:31:42

大家好我正在使用Xilinx Spartan 3e芯片。我可以在严格的输入信号或严格的输出上使用LVDS。但有没有人知道如何编码verilog在双向信号上使用LVDS标准?非常感谢你花时间陪伴。以上

2019-01-08 10:17:47

你好,现在我正在考虑如何通过I2S接收一些信号。即使这些信号不是听觉信号,但它们都与I2S接口通信。但是时钟速率大约为40.96Mbps。我只想通过HS U***接口接收/存储/保存/转储到PC上

2019-08-14 07:05:51

本片文章包含了定时器的一些使用,包括下面五个实验:1.测量信号的脉宽2.PWM 输出3.PWM 互补输出4.PWM 输入5.电容按键检测

2021-08-16 07:00:43

嗨,我试图产生一些随机SPI信号在各种SPI时钟速率。我使用的PIC是PIC16LF1618。当MCU运行在16 MHz时,SPI模块可以在4 MHz产生时钟。然而,当使用锁相环(X4)以

2019-08-27 13:09:50

可靠地采集数据。2. 常用术语在数字电路系统中,定时是最重要的因素之一。 数字通信的可靠性和精确度均取决于定时的质量。 然而,在实际应用中,任何事物都不是理想的。 以下是一些可以帮助您理解特定数字信号

2016-01-18 15:31:09

小弟目前大一学生准备接触ARM在论坛里潜水几天 很多事情不知道想请教下各位学长们。小弟目前会C语言, 应该属于入门级别的C语言还有PCB绘制用的DXP, 还掌握了51单片机的一些技巧在以及VB

2015-06-22 20:06:10

是否可以在放置后手动路由一些关键信号,但在路由之前?我有一些非常关键的信号,我想用最好的路径进行路由,但是如果我使用已实现的设计,我必须解决现有的路由(或者手动取消路由它们!)。看起来如果我可以加载

2018-11-05 11:41:09

此前一个项目。它有一些MAP问题。如下:位置:1333- 具有输入/输出编程的IOB锁定到不支持此类值的Bank 1标准:名称= LVDS_25,VREF = NR,VCCO = 2.50,TERM

2018-10-15 11:53:42

某些比特。• 眼图很好,可以说明信号品质没有问题吗?当然可以。代表整体。4、眼图的衡量指标在对于一个眼图进行好和坏的评估时,通常都有一些常见的衡量指标,比如眼高,眼宽,抖动,占空比等,如上图。通过对眼

2018-09-14 21:12:08

设计人员应该同等重视的问题。今天整理本人接触的电源完整性PI的一些原理,从不的角度去看PI,会有不同的理解,下面开始喽!!!提到互连的电源设计,可能首先想到的电源分配网络(Power

2021-11-15 07:20:09

发生变化的时候,会发生一些反射的现象。拐角方式对于线的粗细变化情况,直角是最差的,45度角好一些,圆角是最好的。但是圆角对PCB设计来讲处理比较麻烦,所以一般是看信号的敏感程度来定,一般的信号用45度角

2017-03-27 13:32:46

发生变化的时候,会发生一些反射的现象。拐角方式对于线的粗细变化情况,直角是最差的,45度角好一些,圆角是最好的。但是圆角对PCB设计来讲处理比较麻烦,所以一般是看信号的敏感程度来定,一般的信号用45度角

2016-11-04 10:42:42

请教一些关于CC2541F256这颗芯片的一些问题。 1、该芯片是使用32M的外部晶振作为时钟倍频到2.4G作为蓝牙信号发射出去,我们的整机做了500套发现所有整机频率有偏移,落在-20KHZ到

2021-08-02 11:44:05

各位专家好,我需要使用C6678处理信号,该芯片有提供数据处理的一些函数那么,类似FFT变换,巴特沃兹滤波器等。有没有文档介绍这些函数用法以及需要包含哪些库,如果有在哪里下载?麻烦提供下,非常感谢。

2018-07-24 07:24:19

你好,有人以前在PSoC 5LP上使用LVDS吗?或者有人做了一些可以用在PSoC 5LP上实现LVDS的东西吗?至少有一些建议是很好的。谢谢大家, 以上来自于百度翻译 以下为原文Hello

2019-07-29 14:48:38

之间的单端I / O.我可以将一些差分信号对配置为单端信号吗?或者它们是硬编码的。我还注意到一些连接到FPGA(U1)的信号看起来不像差分信号对。它们是我可以自由使用的单端唱法吗?例如,在表

2019-09-30 06:11:58

如何对LVDS接口屏的频率进行设置呢?如何对LVDS接口屏的时序参数进行设置呢?

2022-03-04 07:34:04

考虑。下面我根据自己平时维修的一些经验与朋友们谈谈我对替换电容的一些看法。在强电电路中更换电容时要注意的事项

2021-11-16 07:47:06

步一些技术的发展方向和趋势。还有是许多功能实现的算法本身,是非常值得研究和学习的。 因此关注本拦的朋友,希望您的目的首先是为自己做些技术储备,如果想马上应用在产品设计中,可能不会非常顺利的。 下面做

2012-11-16 15:34:58

为什么眼图里会有两个波信号, 如果是传输一个信号的话不是因该只有0或者1吗?谢谢指教 ;)

2011-08-10 14:00:52

1 LVDS信号介绍LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。LVDS是一种低摆幅的差分信号技术,它使得信号能在差

2008-10-16 13:44:45 153

153 基于低电压差分信号(LVDS)的高速信号传输

2010-12-17 17:21:46 40

40 什么是lvds信号

LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。LVDS是一种低摆幅的差分信号

2008-10-16 13:49:11 7844

7844 LVDS信号电平特性

LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。LVDS驱动器由一个驱动差分线对的电流源组成(通常电

2008-10-16 13:50:25 16632

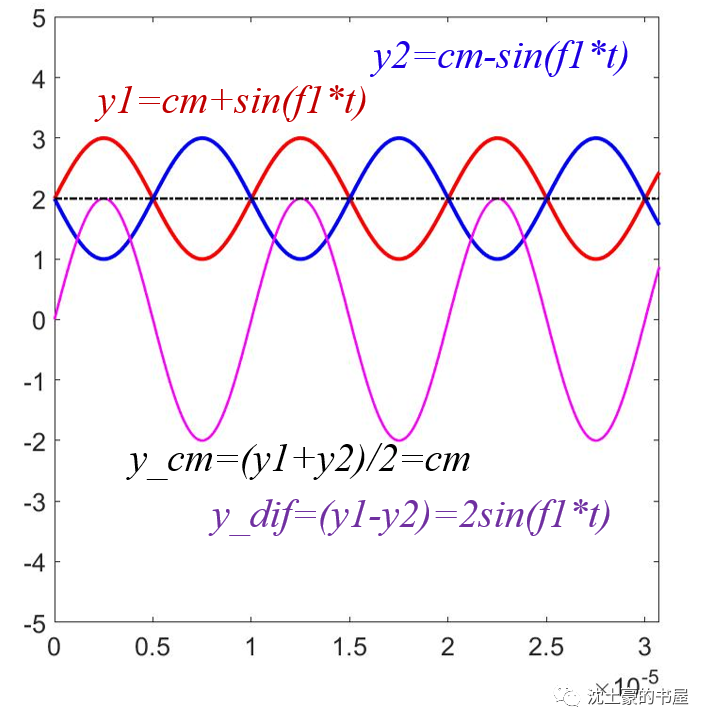

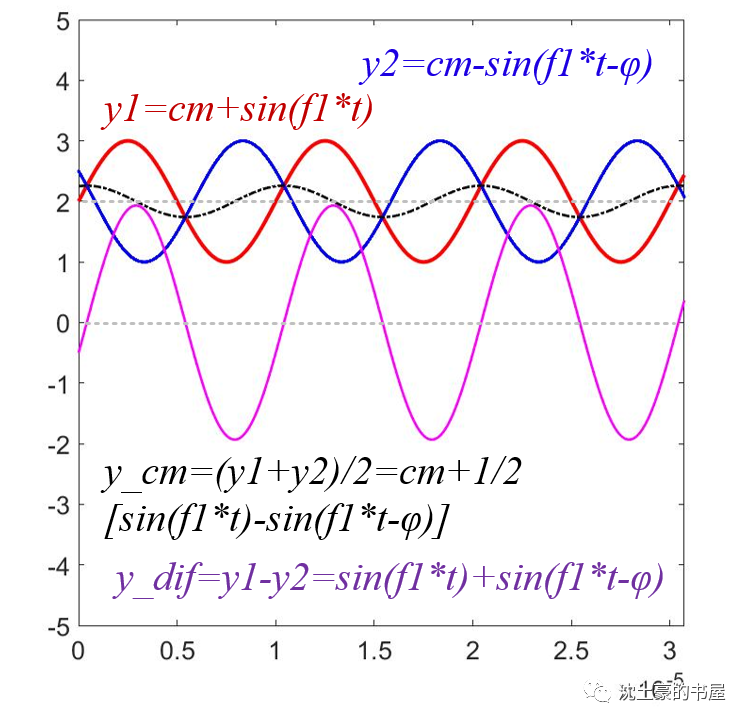

16632 LVDS差分信号抗噪特性

从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:

2008-10-16 13:53:16 1507

1507 LVDS信号的PCB设计

1 LVDS信号的工作原理和特点 对于高速电路,尤其是高速数据总线,常用的器件一般有:ECL、BTL、GTL和GTL+等。这些器件的工艺成

2008-10-16 13:57:52 3359

3359 摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-04-24 16:05:19 1273

1273

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-05-01 11:14:27 1655

1655

本文描述TI 的客户在不用 LVDS (低压差分信号传输)驱动器时,如何采用LVDS 接收器于其他驱动器配合解决一些简单的问题。

2011-07-18 15:21:36 30

30 文中以基于FPGA设计的高速信号下载器为例,从LVDS的PCB设计,约束设置和信号完整性仿真等多方面研究LVDS信号的实现。

2012-04-20 10:37:02 58

58 低电压差分信号(LVDS)是一种高速点到点应用通信标准。多点LVDS (M-LVDS)则是一种面向多点应用的类似标准。LVDS和M-LVDS均使用差分信号,通过这种双线式通信方法,接收器将根据两个互补

2013-08-22 16:09:00 92

92 它差分信号标准类似,LVDS由于消除了磁场,因而比单端信号辐射的噪声要低得多。同时外来噪声作为共模信号耦合到两根线上(即两根线上的噪声电平相同),因此它的抗噪声能力比单端信号要强得多。另外,LVDS驱动器的输出采用电流驱动方式(图1),与其它差分信号标准中的电压

2017-04-06 16:11:31 6

6 GM8827C实现以7:1的压缩比将27位CMOS/TTL信号(RGB 8位和HSYNC、VSYNC、 DE)换成串行 LVDS 输出数据流。输入时钟经内部锁相后,同频率输出,同时转换为 LVDS

2021-11-30 21:06:05 8

8 ANSI EIA/TIA-644 低压差分信号 (LVDS) 标准比更传统的 ECL、PECL 和 CML 标准提供更低的功率和更低的噪声发射,用于高速信号分配。本应用笔记比较了这些通信标准的一些特性,并讨论了LVDS标准的一些优点。

2023-03-29 11:05:07 662

662

本应用笔记讨论了EIA/TIA-644低压差分信号(LVDS)标准在3G移动通信中的应用。LVDS具有低功耗和低辐射特性,非常适合WCDMA、EDGE和cdma2000®基站中的高速时钟和信号分配。提供MAX9205串行器、MAX9206解串器、MAX9150多端口中继器和MAX9152交叉点开关。

2023-03-29 11:14:33 750

750

LVDS (Low Voltage Differential Signaling)是一种小振幅差分信号技术,它使用非常低的幅度信号 (250mV~450mv)通过一对平行的PCB走线或平衡电缆传输数据是一种专业的低电压差分信号

2023-04-06 09:46:43 1286

1286 LVDS发送芯片的输入信号来自主控芯片,输入信号包含RGB数据信号、时钟信号和控制信号三大类。

2023-10-17 17:28:13 583

583

LVDS传输的是什么信号?判断LVDS信号正常的方法 一、LVDS传输的是什么信号? LVDS是一种低电压差分信号,有两种电压状态,即高电平和低电平,它类似于RS485协议。LVDS信号作为一种数字信号

2023-10-18 15:38:13 2929

2929 什么是LVDS和RSDS图象信号?帮忙解释一下LVDS和RSDS这两种传输协议吧 LVDS和RSDS都是用于传输数字图像信号的串行通信协议。它们都是由电子工业界制定的标准,旨在提高图像传输速度

2023-10-18 15:38:16 1232

1232 什么叫做LVDS信号?请问TTL信号与LVDS信号有什么区别? LVDS信号 LVDS(Low Voltage Differential Signaling)又称低压差分信号传输技术,是一种采用

2023-10-18 15:38:18 1265

1265 LVDS中的时钟脉冲信号是干什么的? LVDS(Low Voltage Differential Signaling)中的时钟脉冲信号(Clock)是用于同步数据传输的,是整个LVDS接口的重要

2023-10-18 15:38:20 662

662 两个独立的信号流传输。这两个信号流被称为“正”和“反”信号,每个信号流包含一个有效数据线和一个共享地线。双路LVDS接口在图形和视频传输中得到广泛应用,通常用于解决一些高速传输需要,比如在某些具有高像素密度的液晶显示器(LCD)中

2023-10-18 15:38:22 972

972

电子发烧友App

电子发烧友App

评论