LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

LVDSB是一种高速点到点应用通信标准,比如M-LVDS(多点LVDS)则是一种面向多点应用的类似标准。LVDS和M-LVDS同时提供远距离数字接口,通过电气互连实现串行通信。

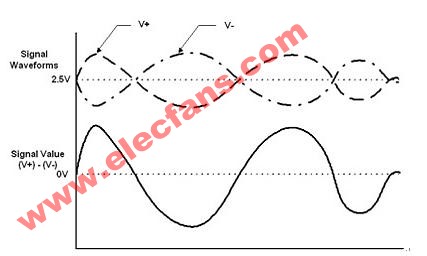

1、差分信号

就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。而承载差分信号的那一对走线就称为差分走线。

2、差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面:

A、抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消;

B、能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少;

C、时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路

3、测试要求

A、差分信号的模拟带宽取决于信号的边沿时间,不等于信号的比特速率,一般都比信号的比特速率高的多,比如480Mbps的信号的带宽可能高达1GHz。所以选择示波器时需要注意信号的带宽要求。在进行眼图测试的时候,要求示波器有相应的眼图模板;

B、应该尽量采用差分探头,对于在线测试,要求示波器的探头为高阻输入。由于LVDS信号的速率一般比较高,应当选择寄生电容比较低的示波器探头的型号;

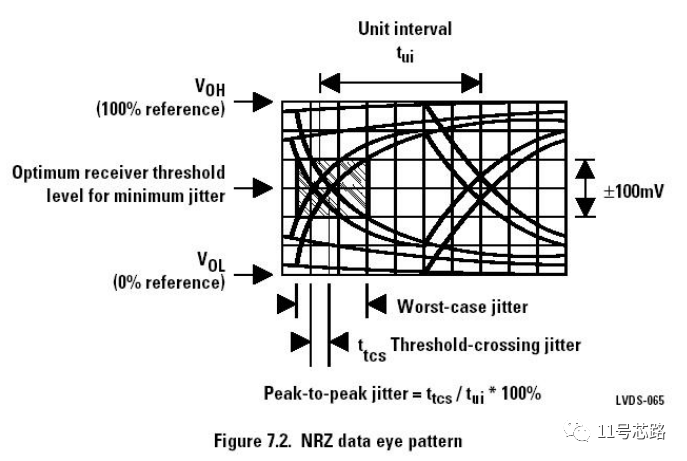

C、可以采用眼图测试的方式来观察信号的质量,眼图张开的宽度决定了接收波形可以不受串扰影响而抽样再生的时间间隔

4、波形测试

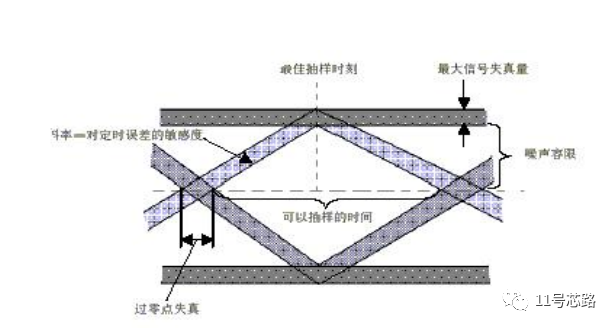

如下眼图最佳抽样时刻应选在眼睛张开最大的时刻。眼图斜边的斜率,表示系统对定时抖动(或误差)的灵敏度,斜边越陡,系统对定时抖动越敏感。眼图左(右)角阴影部分的水平宽度表示信号零点的变化范围,称为零点失真量,在许多接收设备中,定时信息是由信号零点位置来提取的,对于这种设备零点失真量很重要。

在抽样时刻,阴影区的垂直宽度表示最大信号失真量。在抽样时刻上、下两阴影区间隔的一半是最小噪声容限,噪声瞬时值超过它就有可能发生错误判决;图中水平方向上虚线位置对应的电压为判决门限电平。

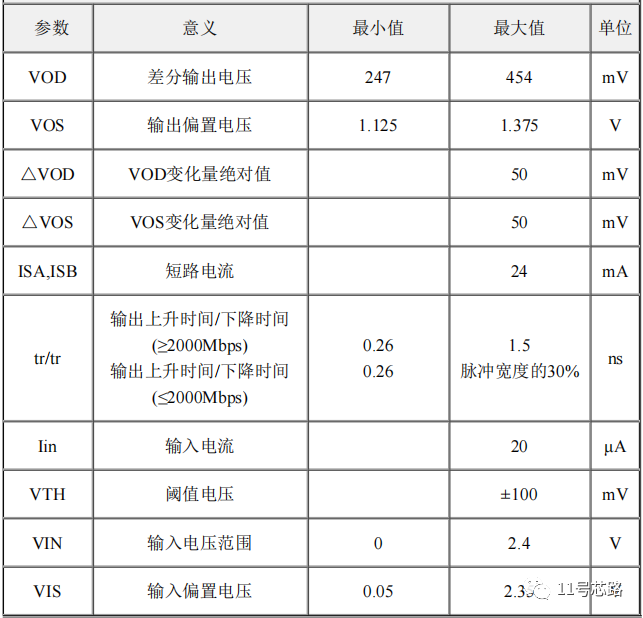

5、LVDS信号特性说明

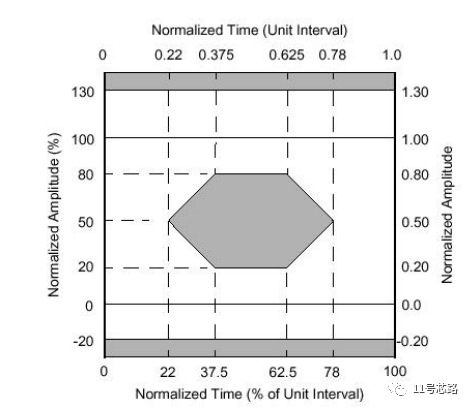

6、眼图测试应采样波形数1500-3000个,而且没有一个点掉入眼图模板中即为合格的数据。如下眼图模板模型。

-

示波器

+关注

关注

113文章

6967浏览量

194629 -

寄生电容

+关注

关注

1文章

301浏览量

20191 -

差分信号

+关注

关注

4文章

405浏览量

28868 -

PCB走线

+关注

关注

4文章

135浏览量

14498 -

LVDS信号

+关注

关注

0文章

18浏览量

8174

发布评论请先 登录

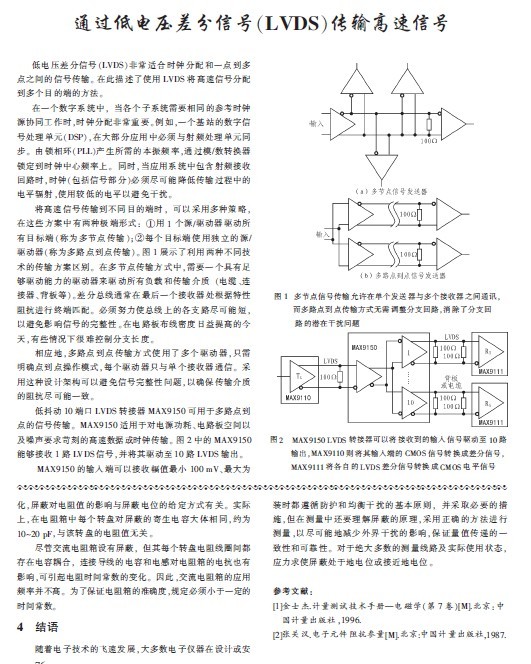

通过低电压差分信号(LVDS)传输高速信号

通过低电压差分信号(LVDS)传输高速信号

怎样才能充分利用低压差分信号LVDS

高速LVDS(低压差分信号)接口电路设计

LVDS差分信号技术质量初勘

LVDS差分信号技术质量初勘

评论