由于FPGA技术和ARM技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解决快速传输数据的需求,因此设计满足系统要求的FPGA并行总线显得尤为重要。本文设计的FPGA的ARM外部并行总线接口,满足了总线的时序要求,并在某航空机载雷达应答机中进行了应用.

2013-08-15 10:44:19 7204

7204

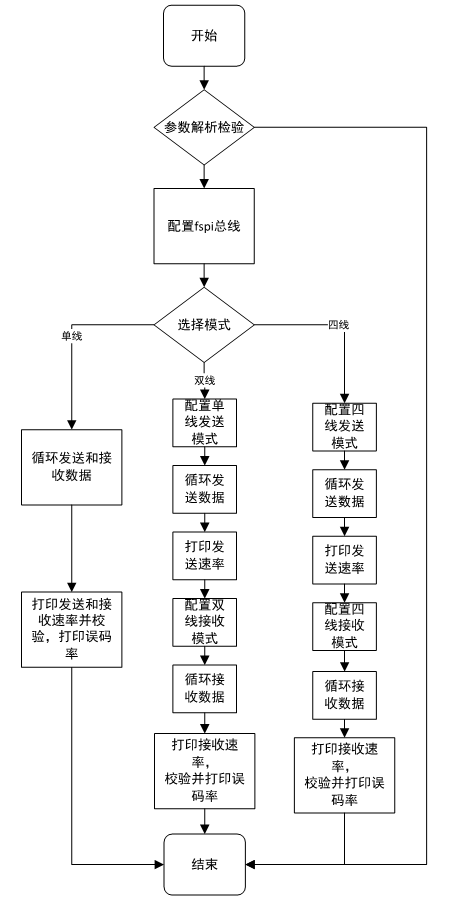

最近学习了ARM+FPGA的设计架构,ARM和FPGA结构的通信大致可以分为两种。

2015-05-25 10:35:04 21452

21452 FPGA+ARM是ZYNQ的特点,那么PL部分怎么和ARM通信呢,依靠的就是AXI总线。这个实验是创建一个基于AXI总线的GPIO IP,利用PL的资源来扩充GPIO资源。通过这个实验迅速入门

2020-12-25 14:07:02 2957

2957

作为一名PCB设计工程师,具备一些高速方面的知识是非常有必要的,甚至说是必须的。就信号来说,高速信号通常见于各种并行总线与串行总线,只有知道了什么是总线,才能知道它跑多快,才能开始进行布线。

2022-12-29 14:23:12 1438

1438

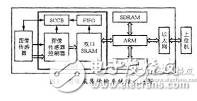

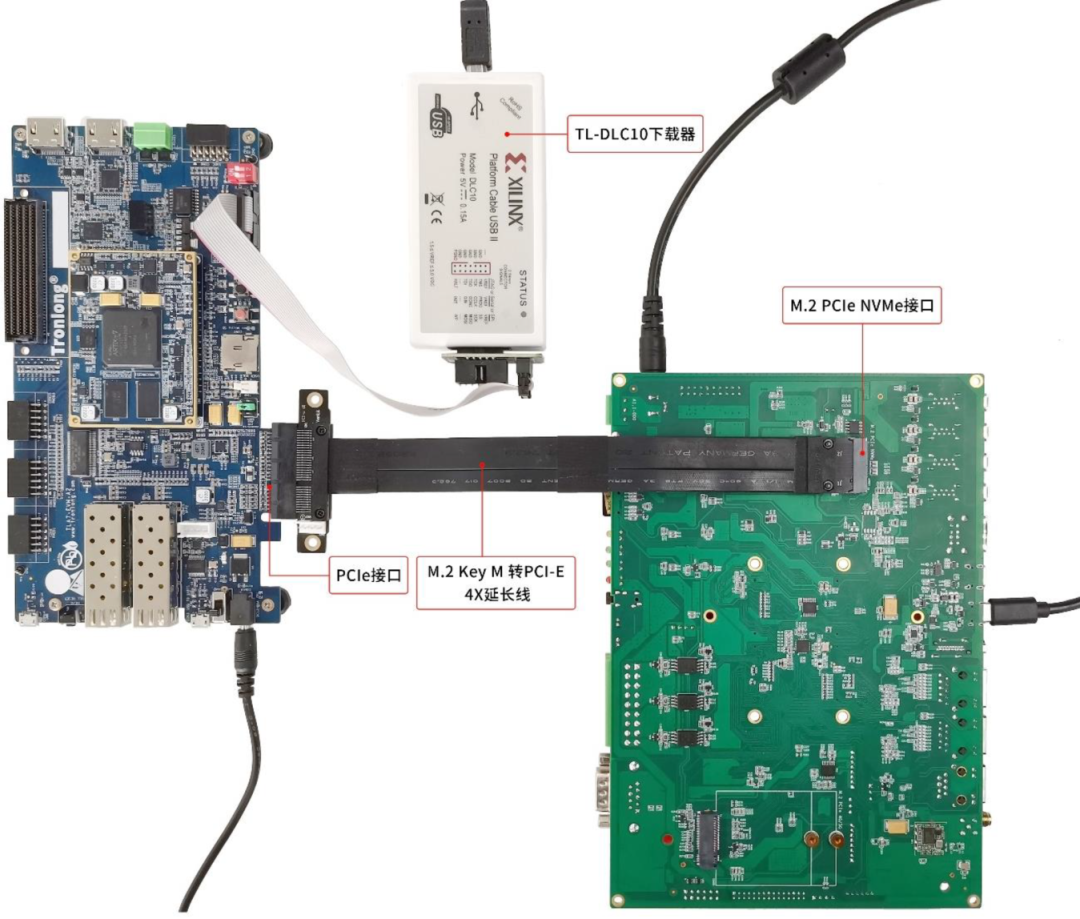

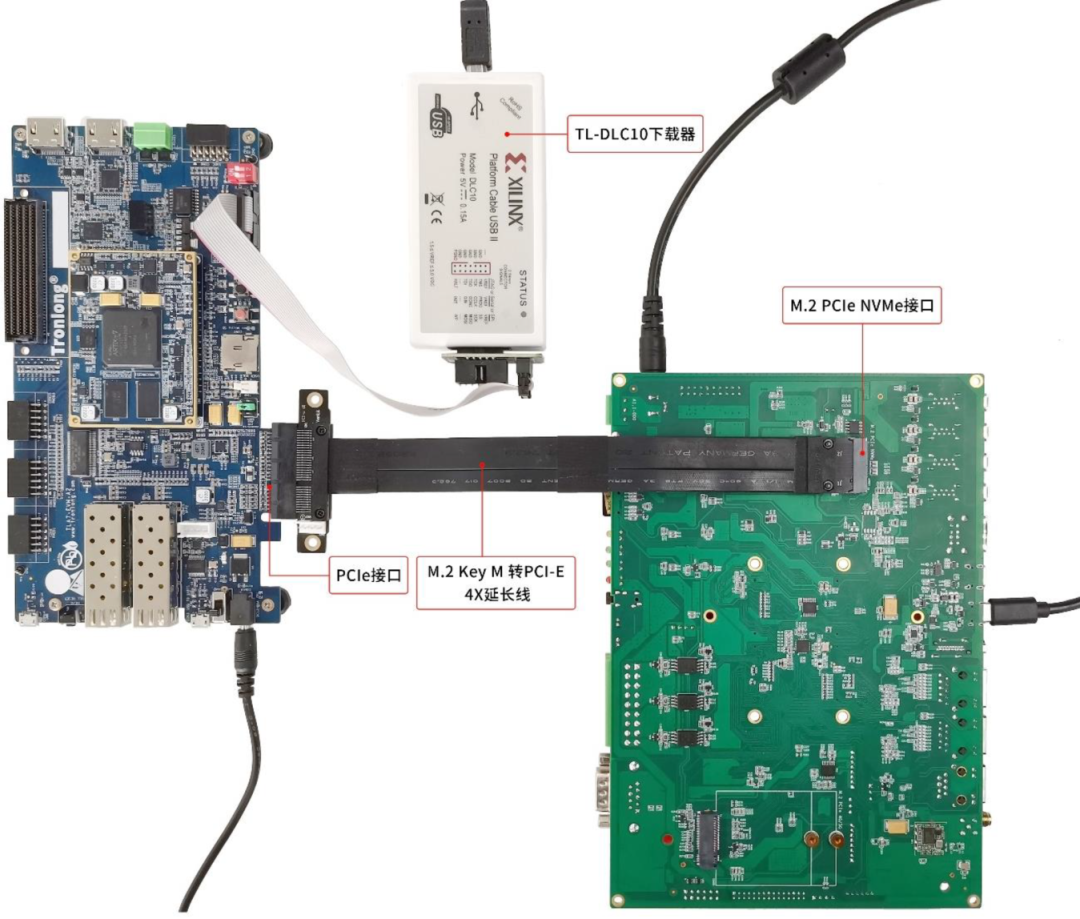

的处理器平台来实现例如多路 / 高速 AD 采集、多路网口、多路串口、多路 / 高速并行 DI/DO、高速数据并行处理等特定功能,因此 ARM + FPGA 架构处理器平台愈发受市场欢迎。 ARM + FPGA 架构能带来性能、成本、功耗等综合比较优势,ARM 与 FPGA 既可各司其职,各自发挥原本架构

2024-01-29 15:13:43 1536

1536

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。

2024-02-22 16:15:03 1624

1624

1、Cortex-M0、端口与总线介绍与配置在ARM DesignStart网址下载的Cortex-M0 DesignStart Eval文件资源中找到名为“cortexm0ds_logic.v

2022-08-08 16:30:08

模式,串行主模式,并行从模式和并行主模式。JTAG模式常用于调试时,将主机好的程序加载到FPGA,优先级高于几种模式。加载模式取决于 FPGA上加载模式管脚(M0,M1,M2)的设置。用外部处理器给

2019-12-10 17:42:18

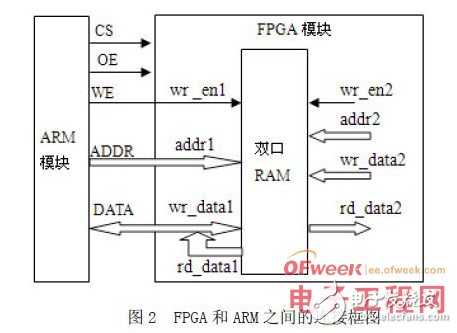

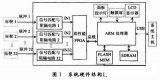

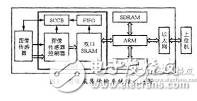

)结合使用完成多通道检控任务的一种实现方法。 各部分功能简介 图1为此系统的结构连接框图。如图所示,ARM芯片与FPGA芯片之间通过数据总线、地址总线及读写控制线相连,而与终端PC则通过串口通信

2008-06-17 12:00:27

·诺依曼结构。所谓哈佛结构就是将数据与指令分开存储,独立编址,可以提高数据调用的效率,TI的DSP也是用这个结构;与之对应的是冯·诺依曼结构,数据与指令共同编址,节省一条总线ARM(Advanced

2021-09-08 17:49:20

FPGA笔记1-ARM单片机和FPGA有什么区别–ARMFPGA总线结构哈佛总线或冯诺依曼结构查找表执行方式串行执行并行执行运行层面软件硬件所用语言C或汇编Verilog HDL/VHDL概念上

2021-07-16 06:54:03

支持GNET、USB固件升级(ARM/FPGA/DSP固件)尺寸87×62×5MM搭配接插件型号FX10A-168P-SV(X1)+FX10A-96P-SV(X2)工作温度-45至85℃存储温度-45至

2017-07-18 10:28:53

V soc以及 Xilinx 的 zynq 7000平台 将 ARM+FPGA 构建到 一个芯片上,串行计算能力和并行的完美结合。感觉还是有点厉害的。本人小白,,希望大家一起来讨论下,FPGA+ARM 这个神奇的东东。。。

2015-08-05 13:48:27

用于:1.与ARM子系统通信2.与DSP子系统通信3.两个FPGA子系统通信4.两个96pin扩展插槽,用于扩展外设板卡5.8个26pin的扩展与测试排针,主要用于并行检测与测试主要应用领域

2010-12-25 15:47:19

FPGA与ARM、DSP的区别在嵌入式开发领域,ARM是一款非常受欢迎的微处理器,其市场覆盖率极高,DSP和FPGA则是作为嵌入式开发的协处理器,协助微处理器更好的实现产品功能。那三者的技术特点以及

2014-06-26 14:23:43

在嵌入式开发领域,ARM是一款非常受欢迎的微处理器,其市场覆盖率极高,DSP和FPGA则是作为嵌入式开发的协处理器,协助微处理器更好的实现产品功能。那三者的技术特点以及区别是什么呢?下文就此问题略

2013-05-06 15:56:02

FPGA与ARM进行并行通信,这个接口应该如何设置?是否要考虑异步时钟域的问题?

2014-11-20 10:50:37

读取到“.”(点)这个字符,通过LED灯定位(板子的FPGA没有引出JTGA端口),发现FPGA可以读到读信号和片选信号,甚至可以读到某一个地址,说明这些信号都没有问题,可以排除,现在唯一确定是总线

2020-07-23 23:22:42

FPGA 中模拟 I²C 接口已成为 FPGA 开发必要的步骤。I2C 协议作为一个串行总线标准尽管没有并行总线的数据吞吐能力,但是它的以下特点使其有着广泛的应用:• 只需要两条总线—串行数据线 SDA

2018-09-29 09:37:11

FPGA的并行多通道激励信号产生模块FPGA的并行多通道激励信号产生模块.docx

2012-08-11 10:35:50

输出。这两个芯片的管脚虽然很多,但大多数都是与硬件设计有关。其实几乎所有的并行ADC和并行DAC与FPGA之间的接口只有一条时钟线与一组数据总线,数据总线的位宽即为ADC/DAC的位数。每个时钟周期

2020-09-27 09:40:08

fpga的硬件换成我们自己的arm设备。不过经过研究这种设想不可行。个人看法,也许不对哦。!!!!arm是一款多核心,单进程处理器,目前为止arm处理器都不支持多线程。所以多线程概念不能将并行计算优化

2015-12-30 14:33:38

`fpga基础篇(二):三大并行结构最近小编比较忙,所以这期给大家介绍一个基础篇,比较简单,但却是FPGA编程的基础。我们知道FPGA与单片机最大的区别就是FPGA是并行执行的,而单片机是串行的,说

2017-04-13 10:23:27

AD1847串行端口音频编解码器如何与并行总线接口的实例

2009-05-13 09:57:27

CC2530并行I/O端口应用是什么

2022-01-25 07:50:29

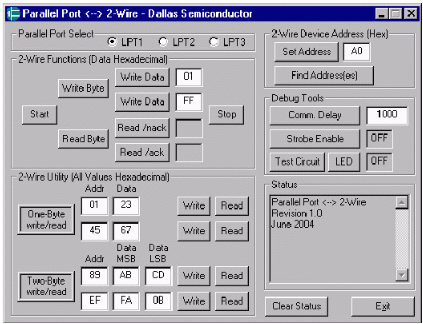

目前,计算机中的并行接口主要作为打印机端口,接口使用的不再是36针接头而是25针D形接头。所谓“并行”,是指8位数据同时通过并行线进行传送,这样数据传送速度大大提高。

2020-03-23 07:32:49

嗨,我在我的PC上安装了PCI并行端口卡以提供LPT2。我想运行XILINX并让它检测卡,以便我可以使用XILINX Parallel Cable IV来处理它。 XILINX检测到该卡但发出

2019-05-22 09:27:37

数据,验证、停止,并用其他的输入端口控制读写操作,充分利用片上系统的优良功能 ,使FPGA能够作为主机与外部含IIC总线设备互相通信。

2012-05-16 16:08:36

增强型并行端口EPP的主要特点是:提供了一个并行端口双向沟通,即一种方法来读取和写入外围设备连接到您的PC的并行端口。交易是8位宽和原子。主机(PC)始终是交易的始作俑者,读取或写入。有没有突发

2012-03-22 16:56:03

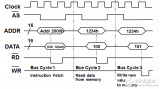

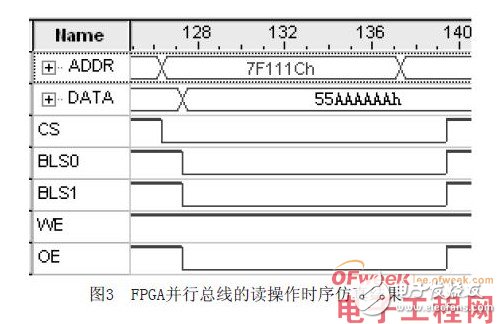

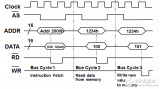

等串行总线接口只能实现FPGA 和ARM 之间的低速通信 ;当传输的数据量较大.要求高速传输时,就需要用并行总线来进行两者之间的高速数据传输.

2019-09-17 06:21:10

为什么,8位位宽的信号[7:0]data_1 ,通过一条连线wire,到另一条 输入端口 [7:0]data_2,只是一条线就把8位数据同时传输。我理解的并行,不是8条线同时存在,同时传输吗

2017-03-13 12:34:16

国外的融合技术专家展示了一项基于FPGA的数据采集系统,用于合成孔径成像技术。采用了Xilinx ISE设计软件,支持ARM AMBA AXI4接口。文风犀利,观点新颖,FPGA中使用ARM及AMBA总线中不可多得的资料在赛灵思FPGA中使用ARM及AMBA总线[hide][/hide]

2012-03-01 15:48:17

ARM跟FPGA通信,要采用8位地址总线、8位数据总线、读写控制线,怎么实现,地址总线是要映射到FPGA的内部还是直接ARM的内存空间?最好有ARM端简单的C程序描述下,谢谢。

2022-11-22 14:58:26

PCI9656,通过CPCI 总线经J1和J2口传输到雷达系统的其他功能模块。对于并行信号而言,32位带宽的信号首先通过J3口发送到F-PGA内部寄存器中FPGA接收到数据后 将数据写入输入缓存区,并在完成一帧

2019-05-21 05:00:19

如何实现单片机与PCI总线接口的并行通信?

2021-04-29 07:14:26

我想解码一个以50 MHz时钟速度运行的8位并行总线。我想使用FPGA开发板实现这一目标,但我不知道要获得哪一个。我还需要在计算机屏幕上显示解码信息有人能给我一些适合我需要的可用FPGA开发板的信息吗?板越便宜越好。如果需要更多信息,请告诉我。谢谢大卫。

2019-09-05 10:00:38

大、通信速率要求较高的情况,就要采用并行总线的方式了。这时把FPGA当做ARM的一个片外的SRAM访问就可以,可以在FPGA内部生成一个双口RAM,输出的数据总线管腿直接连接到ARM的并行总线的数据总线

2017-01-12 19:00:53

本文结合实际系统中的前端图像处理和图像数据传输需要.充分利用ARM的灵活性和FPGA的并行性特点,设计了一种基于ARM+FPGA的图像快速采集传输系统。

2021-05-07 07:01:28

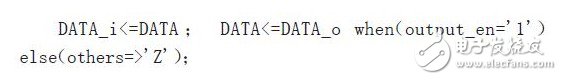

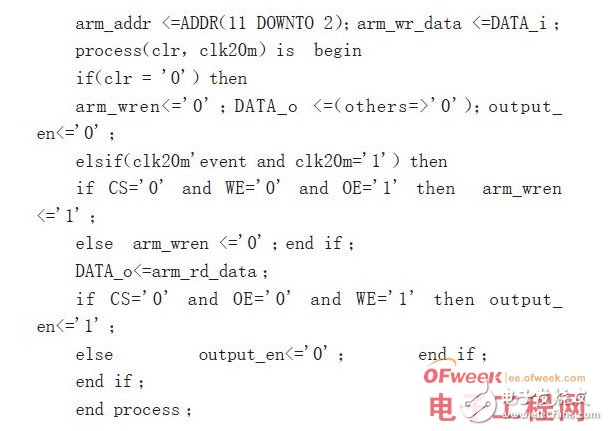

各位前辈,小弟现在刚开始学习ARM,想用ARM与FPGA并行总线通信。实验过程是这样的,我现在FPGA内部建立了一个双口RAM,现在想通过ARM并行总线读写RAM,下面的是FPGA中RAM与ARM

2022-11-22 14:53:52

和W/R,左端口数据线(D0L~D15L)和地址线(A0L~A14L)也分别与局部总线的数据和地址线相连。双口RAM右端口和标准VME总线通信,由FPGA负责译码标准VME总线控制信号线产生接口控制

2019-04-22 07:00:07

最近做的东西涉及到将原有的DSP+FPGA架构的程序移植到ZYNQ-7系列FPGA上,请问如何将原DSP程序移植到ZYNQ-7的ARM上,可不可以做一个EMIF总线和AXI总线转换的模块呢?

2014-05-12 21:51:09

对于60M10路并行总线一般采取多大的线宽和线间距,保证不会有串扰。芯片手册上说的是这10路电平的上升和下降沿的时间为1ns,我用Allegro 定义的约束规则是:传输线阻抗70欧姆,传输延迟为0.1ns~0.5ns。板材为4层板,FR4。谢谢!

2014-04-12 23:15:26

高速串行总线与并行总线的差别是什么?高速测试方面的挑战是什么?远端环回的优点是什么?

2021-05-12 06:31:54

AD1847串行端口音频编解码器如何与并行总线接口的实例

2009-05-13 09:54:41 25

25 AD1847串行端口音频编解码器如何与并行总线接口的实例

2009-05-15 15:13:14 27

27 采用 ARM7 内核芯片S3C4510 的高性能网络控制器结合使用CPLD 设计VME 总线控制器逻辑时序,研制出了类似3U VME 的并行设备总线控制器。开发嵌入式系统uClinux的网络通讯软件,实现提供

2009-06-15 08:54:42 14

14 基于FPGA的PCI总线接口设计::PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接

2009-06-25 08:17:18 48

48 CAN总线是一种应用广泛的实时性现场总线,提出了基于具有ARM7TDMI内核的32位微控制器的CAN总线智能节点设计方案。详细介绍了ARM控制器(LPC2294)的特点、智能节点的结构以及系统软

2009-12-01 14:27:35 18

18 PCA9564是一款采用CMOS工艺,支持并行总线与串行I2C总线通信转换的接口器件,适用于微控制器/处理器使用并行总线扩展I2C总线接口。它支持并行总线与I2C总线双向通信,在I2C总线上

2010-03-10 15:47:12 51

51 PCA9665是一款并行总线与串行I2C总线接口转换的器件,适用于微控制器/处理器使用并行总线扩展I2C总线接口。它支持并行总线与I2C总线双向通信,在I2C总线上,它可以设置为主机或从

2010-03-10 15:49:10 46

46 PCF8584是一款采用CMOS工艺制作的集成电路,微处理器/微控制器通过它可以将并行总线转换成串行的I2C总线,它支持并行总线和串行I2C总线间的双向通信。它既可以作为主机也可以作

2010-03-10 15:52:32 35

35 基于Actel FPGA 的双端口RAM 设计双端口RAM 芯片主要应用于高速率、高可靠性、对实时性要求高的场合,如实现DSP与PCI 总线芯片之间的数据交换接口电路等。但普通双端口RAM 最大

2010-11-15 17:44:19 82

82 ARM I2C 总线接口的寄存器设置

控制ARM 12C总线接口需要配置总线控制寄存器(rIICCON)、总线状态寄存器(rIICSTA

2009-03-14 18:00:43 1636

1636 并行端口工作原理

并行端口的基本知识

2009-07-27 12:16:13 2976

2976 本文设计的靶场破片测速系统以ARM处理器为控制核心,利用了FPGA强大的多路并行处理能力进行数据处理,在基于嵌入式Linux的平台上采用Qt/Embedded设计了友好的人机交互界面。

2011-02-21 09:39:57 874

874

本文介绍的基于PCI总线的FPGA计算平台的系统实现:通过在PC机上插入扩展PCI卡,对算法进行针对并行运算的设计,提升普通PC机对大计算量数字信号的处理速度。本设计采用5片FPGA芯片及

2011-08-21 18:05:31 1970

1970

本设计开发出了一套基于双FPGA+ARM架构的高速计算机屏幕图像压缩系统。系统通过对图像压缩系统任务的划分,利用FPGA的并行计算能力和灵活的编程方式,完成图像压缩算法。

2011-08-22 11:44:31 2039

2039

针对现场可编程门阵列(FPGA)芯片的特点,研究FPGA中双向端口I/O的设计,同时给出仿真初始化双向端口I/O的方法。采用这种双向端口的设计方法,选用Xilinx的Spartan2E芯片设计一个多通道图像信

2011-09-27 16:17:21 89

89 本文介绍PC并行端口在单片机等控制系统中作为数字I/O口的应用。现在常见的并口有五种:SPP型、PS/2型、EPP型、ECP型和多模式接口.

2011-11-23 13:47:35 7318

7318

并行端口常为计算机开发人员作为用户扩展端口使用。增强型并行端口协议从根本上改变了这一状况,它不但与SPP兼容,又能进行双向的高速数据传输。

2011-11-23 13:54:49 2214

2214

并行端口在接口设计工程中是最常用的。该端口在任何规定时间内将允许输入达到9比特,输出达到12比特。该端口由4条控制线,5条状态线和8条数据线组成。在PC机后部常常可以见到作

2011-11-23 16:51:41 62

62 提出了利用12c总线扩展单片机的并行口的方法。对于不具有12C总线的单片机,可以利用其I/O口模拟来实现。

2012-04-13 15:11:17 8

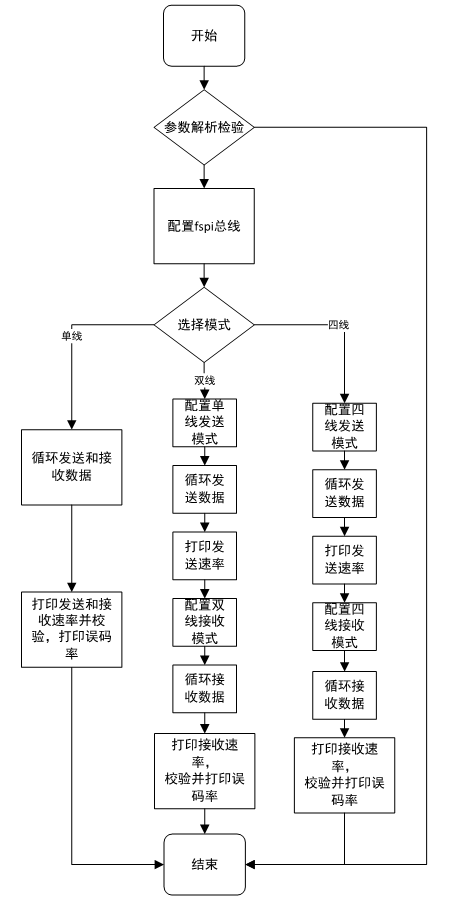

8 基于FPGA的ARM并行总线研究与仿真

2017-01-24 16:54:24 19

19 FPGA与ARM、DSP的区别

2017-03-15 08:00:00 9

9 本文介绍了FPGA电源设计并行工程的合理性,讲解了并行工程(CE)技术及其作用,讨论了FPGA电源系统设计的复杂性和不确定性。

2017-10-13 13:00:35 5

5 基于FPGA和多DSP的多总线并行处理器设计

2017-10-19 13:40:31 4

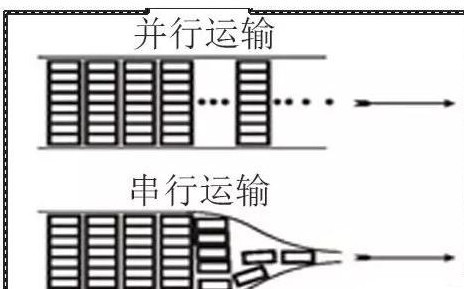

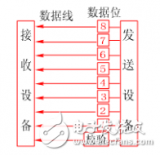

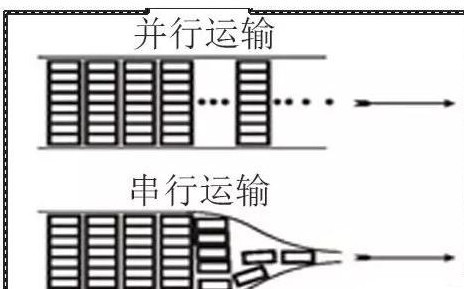

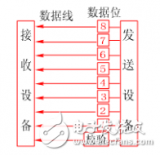

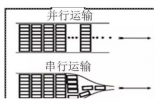

4 并行通信传输中有多个数据位,同时在两个设备之间传输。发送设备将这些数据位通过 对应的数据线传送给接收设备,还可附加一位数据校验位。串行数据传输时,数据是一位一位地在通信线上传输的,先由具有几位总线的计算机内的发送设备,将几位并行数据经并--串转换硬件转换成串行方式

2017-11-13 09:15:29 40722

40722

并行总线,就是并行接口与计算机设备之间传递数据的通道。采用 并行传送方式在 微型计算机与 外部设备之间进行 数据传送的接口叫并行接口。

2017-11-13 09:19:47 78731

78731 并行总线,就是并行接口与计算机设备之间传递数据的通道。采用并行传送方式在 微型计算机与外部设备之间进行数据传送的接口叫并行接口,它有2个主要特点;一是同时并行传送的二进位数就是数据宽度;二是在计算机与外设之间采用应答式的联络信号来协调双方的数据传送操作,这种联络信号又称为握手信号。

2017-11-13 09:55:07 12563

12563

本文结合实际系统中的前端图像处理和图像数据传输需要.充分利用ARM的灵活 性和FPGA的并行性特点,设计了一种基于ARM+FPGA的图像快速采集传输系统。所选的ARM体系结构是32位嵌入式RISC

2017-11-24 09:23:21 3937

3937

增强型并行主端口 (Enhanced Parallel Master Port, EPMP)提供了并行的 4 位 (仅适用于主 模式)、 8 位 (主模式和从模式)或 16 位 (仅适用于主模式

2018-06-22 05:20:00 1

1 本文主要介绍了dsPIC33F系列参考手册之并行主端口(PMP).

2018-06-25 06:20:00 0

0 PIC32系列中文参考手册—第13章 并行主端口(PMP)

2018-05-25 17:29:29 14

14 并行总线波形捕获与分析。

2018-06-25 15:44:00 3560

3560 AT24C04是具有I2C总线接口的EEPROM.大小为512*8bit.单片机AT89S52本身不具有I2C总线结口,所以可编写程序用并行端口模拟I2C总线协议读写AT24C04.

2019-08-14 14:34:25 2347

2347 在以51单片机为核的小型电路设计中,没有足够的I/O端口与内部时钟中断实现I2C总线功能。本文运用VHDL语言对FPGA进行必要的编程,在不影响51单片机地址分配的同时能够将8位并行数据转化为符合

2019-08-19 08:00:00 3

3 作为一名PCB设计工程师,具备一些高速方面的知识是非常有必要的,甚至说是必须的。就信号来说,高速信号通常见于各种并行总线与串行总线,只有知道了什么是总线,才能知道它跑多快,才能开始进行布线。

2020-10-21 14:14:21 4413

4413

早些年的老式设备都采用并行传输,而现在的设备都采用串行传输。为什么并行传输会被串行传输所取代呢?

2021-06-11 15:19:49 16154

16154 51单片机系列--并行I/O端口基本概念数据的传送方式I/O 端口特性基本概念51系列单片机的每个端口都是8位准双向口,共占32位引脚。每个端口都包括一个锁存器(一个D触发器构成)、一个输出驱动器

2021-11-20 11:21:05 12

12 CC2530并行I/O端口应用CC2530总共具有21个数字I/O引脚,这些引脚可以组成3个8位端口,分别为端口0、端口1和端口2,通常表示为P0、P1和P2。其中,P0和P1是完全的8位端口

2021-11-29 21:06:03 7

7 ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和并行DAC芯片。

2022-04-21 08:55:22 5774

5774 SOT 降压型 DC-DC 转换器可有效地从并行端口“窃取”电源,同时 SIM/智能卡电平转换集成电路 (IC) 完成接口。这允许并行端口为低压逻辑供电并与之通信。同样的技术也可以应用于USB设计。

2023-01-10 15:15:26 680

680

图1所示电路从并行端口或任何有限的能量源窃取能量。这种功率转换应用通常需要非常高的效率来利用可用的能量。例如,并行数据端口在2.6V时每条数据线可提供高达2.4mA的电流。当八条数据线通过软件配置

2023-02-09 15:46:48 356

356

ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密。

2023-02-16 09:26:57 11450

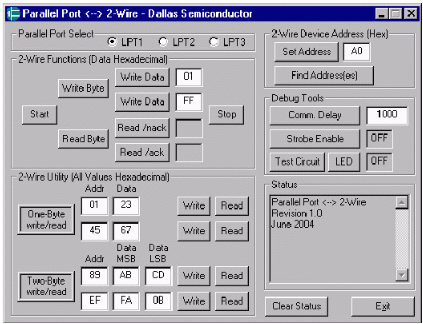

11450 本应用笔记讨论了为有兴趣为应用笔记AN2中所述的并行端口硬件开发3230-Wire软件的客户提供的C源代码。源代码可在达拉斯半导体的FTP站点上免费获得,并且可以在任何使用Windows 95

2023-06-13 17:17:56 318

318

,例如多路/高速AD采集、多路网口、多路串口、多路/高速并行DI/DO、高速数据并行处理等。那么我们先来看看ARM+FPGA架构有什么优势?ARM:接口资源丰富、

2022-10-24 16:25:04 8615

8615

近年来,随着中国新基建、中国制造2025的持续推进,单ARM处理器越来越难满足工业现场的功能要求,特别是能源电力、工业控制、智慧医疗等行业通常需要ARM + FPGA架构的处理器平台来实现特定的功能,例如多路/高速AD采集、多路网口、多路串口、多路/高速并行DI/DO、高速数据并行处理等。

2023-08-01 11:40:32 1201

1201

的灵活性和FPGA的并行性的特点,设计了一种基于ARM+FPGA的高速图像数据采集传输系统。所选用的ARM体系结构是32位嵌入式RISC微处理器结构,该微处理器拥有丰富的指令集且编程灵活;而FPGA则在速度和并行运算方面有很大优势,适合图像处理的实时性要求

2023-09-27 10:45:02 783

783 电子发烧友网站提供《基于FPGA的ARM并行总线设计原理.pdf》资料免费下载

2023-10-10 09:31:31 0

0 电子发烧友网站提供《基于ARM9平台和FPGA的1553B总线测试系统的设计与实现.pdf》资料免费下载

2023-11-08 10:10:29 0

0 并行总线和串行总线的区别 并行总线和串行总线是计算机系统中常见的两种数据传输方式,它们有着不同的工作原理和应用场景。在这篇文章中,我将详细介绍并行总线和串行总线的区别,并探讨它们各自的优势和劣势

2023-12-07 16:45:27 1519

1519 FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

2024-03-15 13:58:14 80

80

电子发烧友App

电子发烧友App

评论