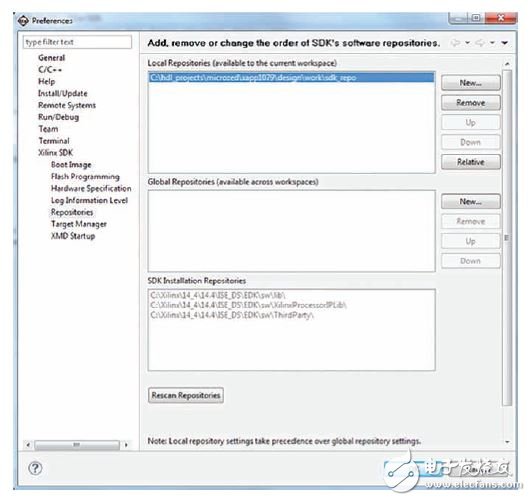

本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

2018-02-26 09:52:53 7957

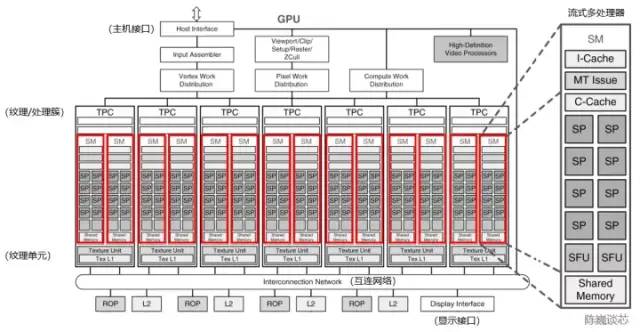

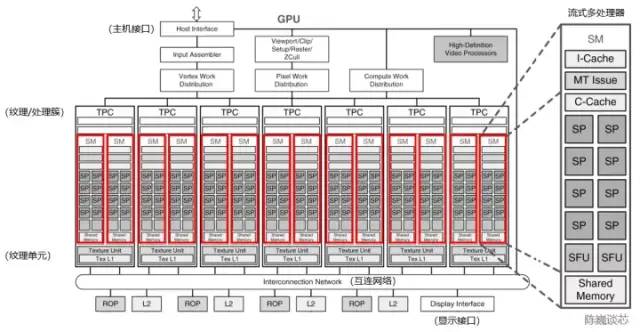

7957 流式多处理器(Stream Multi-processor,SM)是构建整个 GPU的核心模块(执行整个 Kernel Grid),一个流式多处理器上一般同时运行多个线程块。每个流式多处理器可以视为具有较小结构的CPU,支持指令并行(多发射)。

2023-03-30 10:14:24 597

597 专注于引入新品并提供海量库存的电子元器件分销商贸泽电子 (Mouser Electronics)即日起备货Xilinx的Zynq® UltraScale+ 多处理器片上系统 (MPSoC)。

2019-11-25 15:28:48 1102

1102 我想运用生成即保证正确(correct-by-construction)规则设计多处理器混合关键性系统,请问生成即保证正确(correct-by-construction)规则可用吗?在什么情况下可用?

2016-02-17 16:18:34

大家好,我们是一群学生在Zynq 7000 AP SoC上做项目。我们已经提供了一个基本代码,OV7670摄像头可以捕获实时视频并将其发送到电路板。电路板直接在VGA屏幕上显示视频。内存缓冲区已用

2020-04-10 09:51:09

Cortex-A9 处理器,但该器件上的 FPGA 数量存在差别,如表 1 所示:[td]Xilinx Zynq SoC可编程逻辑单元块 RAM 的容量大小 (Mb)DSP 切片

2018-08-31 14:43:05

多处理器通信和LIN模式区别是什么?

2021-12-08 07:32:14

性能要求同时保持足够的灵活性以满足多种应用的需求)的特定需求。配备了多达两个ARM®Cortex®-A15内核、两个C66x DSP内核、若干视频/图形加速器、一个四核可编程实时单元(PRU)以及两个ARM

2018-09-04 09:54:55

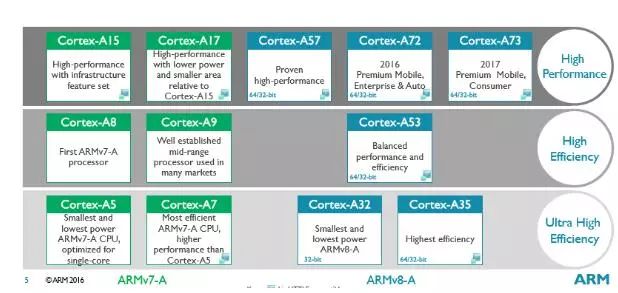

Cortex-A15 MPCore处理器是一款高性能、低功耗的多处理器,采用ARMv7-A架构。

Cortex-A15 MPCore处理器在具有L1和L2缓存子系统的单个多处理器设备或MPCore设备中具有一到四个Cortex-A15处理器。

2023-08-17 07:37:22

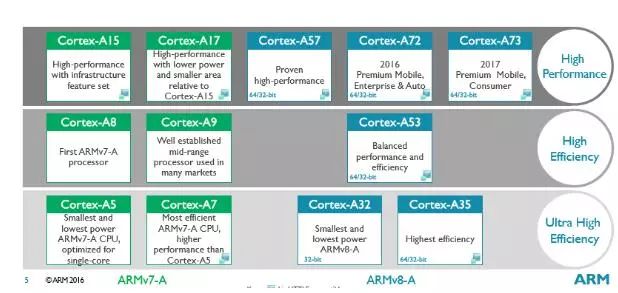

ARM Cortex系列那么多处理器,该怎么区分?

2020-05-29 13:43:08

,ARM7TDMI, ARM9), Cortex-M处理器有一个非常不同的架构。例如:—仅支持ARM Thumb指令,已扩展到同时支持16位和32位指令Thumb-2版本—内置的嵌套向量中断控制负责

2018-05-08 16:27:28

和数据缓存,包括具有

未命中(HUM)

•两个缓存的64位接口

•可旁路写入缓冲区

•一级紧密耦合存储器(TCM),可用作本地RAM

•矢量浮点(VFP)协处理器

•跟踪支持

•基于JTAG的调试

2023-08-02 09:15:45

耳内监听),以及非常高的、超过 2 600 倍Dhrystone 2.1 标准(测 量处理器的运算能力标准)MIPS(百万条指令/每秒)性能的多处理器技术。上面对几个 ARM 处理器内核做了简单的介绍

2019-09-27 09:28:51

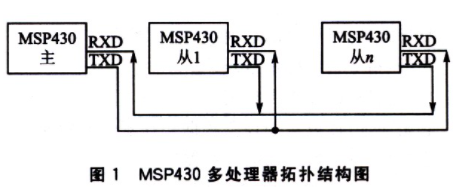

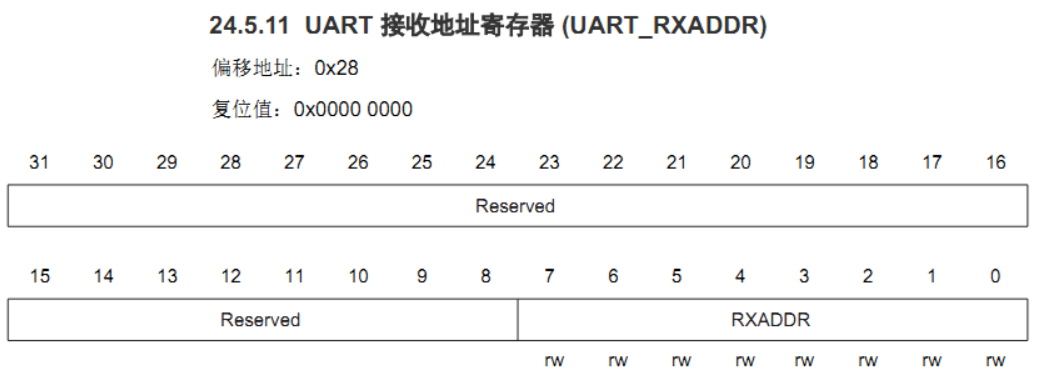

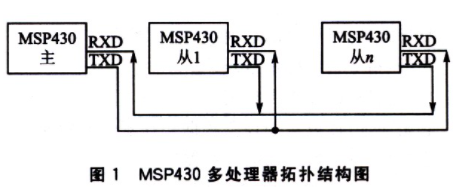

很多处理器通信,即将几个USART连接在一个网络里。比如某个USART设备可以是主机,它的TX输出和其他USART从设备的RX输入相连接;USART从设备各自的TX输入输出与本地,并与主设备的RX输入

2023-04-28 16:24:14

CM3之STM32如何实现多处理器通信

2015-09-17 10:11:58

自旋锁是专为防止多处理器并发而引入的一种锁,它在内核中大量应用于中断处理等部分(对于单处理器来说,防止中断处理中的并发可简单采用关闭中断的方式,即在标志寄存器中关闭/打开中断标志位,不需要自旋锁)。

2020-03-31 08:06:08

普遍认为开发多处理器系统软件的难度要大于单处理器系统。但实际情况并非总是如此。我们这个在 TRW 汽车公司下属的咨询部 TRW Conekt 工作的设计团队最近接管了一个项目,展示了如何根据手中的问题发挥硬件的功能,并通过使用许多个处理器开发出高效系统。

2019-10-23 08:00:03

SPC58EC 有一个中断控制器,支持两个处理器。您可以为每个核心提供不同的向量表。假设两个内核处于活动状态并且发生了一个外部中断(ADC,定时器),这之后的过程是什么?哪个内核将运行中断处理程序?

2022-12-12 08:10:22

dlpc3439只有红绿蓝三色的显示接口,很多处理器没这个接口了。怎么办?

只能选有这个接口的处理器吗?

2018-06-23 07:38:45

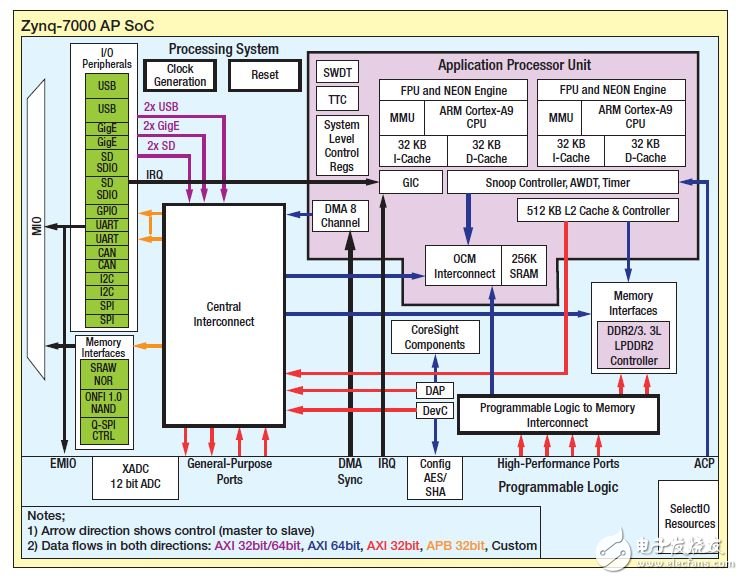

ZYNQ的内部结构包含处理器的系统(PS)和一个可编程逻辑(PL)两个部分。应用处理单元(APU)位于PS部分。应用处理单元APU包括两个ARM的Cortex-A9双核处理器和两个Neon协处理器

2015-07-07 20:22:49

我使用的开发板是HPM6750MINI,我想让HPM6750工作在双核模式。为何我在RT-Thread Settings中打开对称多处理器会报错:报错内容:error: conflicting

2023-02-07 10:39:17

墨水等等。同样地,卡片阅读机和硬币接收器也有复杂的信号和控制需求。多处理器方法把所有这些控制和信号线从VMC的配线中分离出来,用一个简单的从处理器和VMC之间的通信总线来替代它来。通信总线的特性是一个

2018-12-06 10:20:18

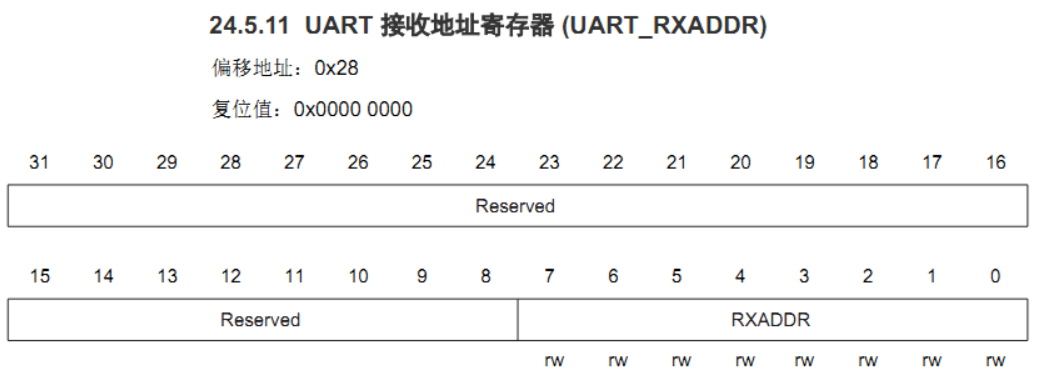

什么是MSP430多处理器?MSP430多处理器有哪些技术要点?

2021-05-27 06:52:20

STM8多处理器通信是什么

2020-11-12 06:27:01

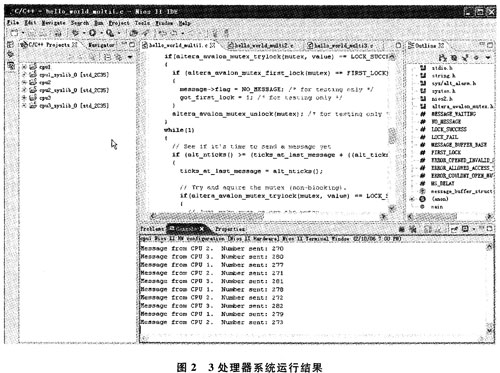

本文将对基于NiosII的SOPC多处理器系统的实现原理、设计流程和方法进行详细的讨论。

2021-04-19 08:51:23

、通信、军工等应用领域都有广阔的发展前景。在异构多核SoC处理器上,OpenCL将其中一个可编程内核视为主机,将其他内核视为设备。在主机上运行的应用程序(即主机程序)管理设备上的代码(内核)的执行,并且还

2020-09-08 09:39:19

类别:嵌入式系统处理器知识产权许可商ARMHoldingsplc已经成功开发出双内核Cortex-A9处理器设计(被称为Osprey)的两个实现。Cortex-A9处理器能与其他Cortex系列

2021-12-13 06:03:17

Zynq-7000是Xilinx推出的一款全可编程片上系统(All Programmable SoC)。Zynq-7000 器件配备双核 ARM Cortex-A9 处理器,该处理器与基于 28nm

2018-06-07 15:36:43

两个方面的内容:IP核生成和IP核复用。文中采用IP核复用方法和SOC技术基于AVR 8位微处理器AT90S1200IP Core设计专用PLC微处理器FSPLCSOC模块。

2019-07-26 06:19:34

。HPI8数据的传输必须以字节为单位。在DSP与主机传送数据时,HPI能自动地将外部接口传来连续的8位数组合成16位数后传送给主机。HPI主机由以下五个部分组成:HPI存储器(DARAM)。HPI

2019-06-06 05:00:39

视频监控嵌入式平台的可选方案。双内核汇聚式处理器——BF561ADSP BF561处理器是Blackfin产品家族中的一个具有高性能成员,它包括两个独立的ADI处理器核,每个处理器核包含一个双乘法

2010-03-16 10:52:08

随着嵌入式处理需求的快速增长,系统架构正朝着多处理器设计的方向发展,以解决单处理器系统复杂度太高和计算能力不足的问题。凭借其高逻辑密度及高性能硬模块,新一代FPGA已经使功能强大的芯片多处理(CMP

2019-08-01 07:53:43

CC-NUMA(Cache Coherent NUMA)。对于CC-NUMA中的并行处理任务,操作系统的调度器要格外小心。在实际应用中,不同层次存储可以用不同的组织方式互连。比如,一个多处理器系统可能包含多个

2022-06-07 16:46:44

多内核是指在一枚处理器中集成两个或多个完整的计算引擎(内核),多核处理器是单枚芯片(也称为“硅核”),能够直接插入单一的处理器插槽中,但操作系统会利用所有相关的资源,将它的每个执行内核作为分立的逻辑

2019-06-20 06:47:01

机)节点集成到同一芯片内,各个处理器并行执行不同的线程或进程。在基于SMP结构的单芯片多处理机中,处理器之间通过片外Cache或者是片外的共享存储器来进行通信。而基于DSM结构的单芯片多处理器中,处理器间

2011-04-13 09:48:17

我想在多处理器系统中使用 EMIF。 为此,应不时将地址和数据总线设置为高阻抗状态。 可能吗? 我找不到图纸中连接 EMIF 总线的位置? 直接连接到 PIN 或

2024-03-05 06:51:37

你好,我打算建立通信以在两个处理器之间读写。一方面是ASIC(MCIMX6)上的四核ARM Cortex A9处理器,另一方面是FPGA(ZC7020)。我在FPGA端没有任何PCIe硬端口。因此

2020-04-16 09:04:30

随着时代的发展,单核片上可编程系统SOPC(Systern On a Programmable Chip)解决复杂问题的能力与处理速度已很难满足用户的需求,面向多处理器SOPC系统的设计成为片上系统

2021-03-16 07:44:35

求一种多处理器并行计算机系统的设计方案

2021-04-27 06:58:57

高速缓存作为中央处理器 (CPU) 与主存之间的小规模快速存储器,解决了两者数据处理速度的平衡和匹配问题,有助于提高系统整体性能。多处理器 (SMP) 支持共享和私有数据的缓存,Cache 一致性

2021-02-23 07:12:38

本文设计了一种在多处理器系统中的Nios II软核处理器的启动方案,这个方案在外部处理器向Nios II的程序存储器和数据存储器加载数据时,可以控制Nios II处理器的启动。

2021-04-27 06:52:42

`在上一次的灵动微课堂中和大家分享过MM32F013x-UART 9bit通信实例,本次微课堂在此实例的基础上实现UART多处理器通信。MM32F013x系列MCU支持UART多处理器通信,其

2020-12-04 16:52:53

原子哥,论坛上的大神们,有做过串口的多处理器通信么?如果有,大家是用空总线检测还是用地址标记的方式啊?

2019-09-05 04:35:13

本文提出了一种全新的总线可重配置的多处理器架构。该架构结合了多核与可重配置处理器的优势,具有并行性高、计算能力强、结构复杂度低并且应用领域广泛灵活的特点。对

2009-06-13 14:11:04 11

11 定义了一种完全基于局部处理器的多处理器系统,讨论了系统的实现条件,提出了一种共享总线结构,建立了处理器域之间基于固定地址窗的信息交换机制,实现了无主多处理器

2009-06-15 08:57:52 11

11 分析了Intel-21554 非透明桥的结构特点,建立了利用LookupTable 基地址模式实现多处理器地址窗的映射机制,描述了实现所述地址映射的详细过程,提供了利用标准非透明桥实现无主多

2009-08-24 10:09:46 16

16 SoC技术的发展使多个异构的处理器集成到一个芯片成为可能,这种结构已成为提高微处理器性能的重要途径。与传统的多处理器系统一样,Cache一致性问题也是片内异构多处理器系统

2009-09-26 15:02:01 11

11 多处理器实时调度理论是目前实时系统的关键技术。论文研究了PFair 调度算法在多处理器中的调度理论,在此基础上,提出了一种基于PFair 调度算法的处理器分组调度算法。该算

2009-12-18 15:38:02 11

11 基于NiosII的SOPC多处理器系统设计方法

两个或多个微处理器一起工作来完成某个任务的系统称为“多处理器系统”。传统基于单片机的多处理器系统

2009-10-17 09:28:42 1069

1069

满足多媒体需求,便携电子风行多处理器架构

随著多媒体应用要求越来越高,在小小的行动装置内,除了要有即时动态影音呈现,又必须处理大量图型化

2009-12-15 10:30:02 639

639 多媒体手机在满足传统语音通信的同时还必须提供稳定、高质量的多媒体表现,传统的单处理器方案不能满足这些并行任务的处理能力要求,采用具有视频、Java和安全专用硬件加速器的多处理器引擎系统级芯片能有效解决这些多媒体任务要求,并能有效降低系统功耗。

2011-02-25 11:01:21 82

82 嵌入式处理器分类 处理器造型需考虑的因素 多处理器在复杂系统中的应用

2011-02-28 11:57:26 64

64 摘要:提出一种嵌入式异构多处理器系统的结构模型,论述这种系统的通信机制,并阐述在基于这种嵌入式异构多处理器系统模型的实时图像处理系统中,运算节点采用由TI公司的TMS320C6416 DSP芯片构造的信号处理板时,在运算节点与主控节点之间实现高速数据传输的

2011-03-01 01:34:01 47

47 本篇论文采用微核心架构在异质性多处理器上建构核心,经由在不同处理器上执行相同设计之核心以提供上层应用程式统一的介面。上层应用程式可依据其所在处理器的特性执行相对应的报务等待其它应用程式的请求。藉由在不同处理器上执行相同核心以及不同特性的应

2011-03-01 13:40:11 23

23 本文提出了当多处理机系统工作时,为了实现快速有效的通信,采用使多处理器共享存储器方案。IDT7134双口RAM是本方案选择的共享存储器。针对该方案,本文给出了接口电路的硬件设计

2011-04-27 11:20:38 28

28 人们一般希望用一个处理器来处理整个系统,但有的时候加入一个新的处理器将是一个很好选择。尽管使用多处理器会带来一些成本增加,但多处理器把任务划分开可简化设计,并加快

2011-05-25 17:29:11 28

28 一个大型复杂系统往往有多个处理器,处理器间要协同工作依必须交换数据。给出基于存储体共享的处理器交换数据的三种方法,即:基于双口RAM 的方法、基于单向或双向FIFO 的方法、

2011-07-18 15:27:21 39

39 怎样使用Nios II处理器来构建多处理器系统 Chapter 1. Creating Multiprocessor Nios II Systems Introduction to Nios II

2012-10-17 14:51:06 19

19 中的一个,一种设计上的选择会潜在地限制了系统的性能。随着应用的发展,裸机程序可以同时运行两个处理器上,或者每一个处理器运行不同的操作系统成为一种需求。 在ZYNQ SoC系统中,使用两个处理器运行裸机

2017-02-08 02:23:11 247

247 作者:Adam Taylor 在上一篇博客中我们了解了Zynq SoC的OCM(片上存储器) ,利用它可以实现在AMP模式下内部处理器内核之间的通信。现在我们将写一些程序代码将这个设备(OCM)利用

2017-02-08 15:38:12 606

606 到目前为止我们摸索使用过的Zynq All Programmable SoC PS(处理器系统)部分的所有设备都是只利用了一个ARM Cortex-A9处理器内核(内核0),然而在Zynq SoC

2017-02-11 10:06:11 2262

2262

在我的上一篇博客中我介绍了利用Zynq SoC上的两个ARM Cortex-A9 MPCore处理器执行不同的任务程序,实现非对称的多进程处理模式的概念。

2017-02-11 10:08:38 1898

1898

智能化赋予了物联网更深刻的实用价值,但是在计算能力强与功耗低的之间寻求性能最优是目前物联网设备极难解决的问题.异构多处理器结构与单一或者同构的多处理器相比可以结合不同处理器的优势,同时满足高计算能力

2017-12-19 15:06:56 0

0 针对多处理器系统中随机到达的任务,设计了可靠性约束下的节能调度算法( ESACR)。该算法在满足任务截止期限的前提下选择一个预计产生能耗最小的处理器以节能,在单个处理器上运用最早截止期限优先策略进行

2018-01-08 14:20:44 0

0 Zynq-7000应用处理单元存在于PS内,包含带有NEON协处理器的两个Cortex-A9处理器。在多处理器配置中,将两个处理器连接起来共享一个512KB L2高速缓存。 每个处理器是一个高性能、低功耗的核,各自有两个独立的32KB L1数据高速缓存和指令高速缓存。

2018-03-19 16:40:27 45

45 对于一个具有多个CPU的多处理器系统,在单板或系统中的一个或多个设备中,CPU和内核有时可以相互作用或依赖于其他CPU或内核的动作。单个设备上的多个内核甚至共享一个普通的内存块,其中包含可执行代码或SysDeDATA。因此,经常需要调试多个CPU或多个内核,同时尝试调试提供处理器间通信的代码。

2018-04-25 15:36:51 8

8 ,可以为Zynq UltraScale+ MPSoC、 Zynq-7000 All Programmable SoC,以及MicroBlaze等处理器平台创建嵌入式应用,实现真正的同质及异构多处理器设计、调试和性能分析。

2020-05-31 08:40:00 2082

2082 了解如何在Zynq Cortex A9处理器之间执行处理器间通信。

处理器间通信有助于促进非对称多处理(AMP)系统设计。

2018-11-26 06:47:00 3446

3446 利用Visual DSP++4.0多处理器调试器可在硬件平台上对用户系统进行全面的程序测试和评估.同时支持I/0处理器间的通信和MMS数据传输。TigerSHARC DSP多处理器系统可以配置

2019-02-25 11:08:27 7

7 同步多处理器,英文为Synchronous Multi-Processors,缩写为SMP。同步多处理器系统在工作的时候,每当一个任务完成后,空闲的处理器会立刻寻找下一个新的任务,对于外部而言,这两颗处理器是一个整体,共同完成同一个工作。

2020-06-02 09:16:17 903

903 iWave的Xilinx ZU19/17/11 Zynq UltraScale+ MPSoC SoM集成了Xilinx Zynq UltraScale+多处理器SoC (MPSoC)。

2020-09-24 14:12:03 2433

2433 MM32F013x系列MCU支持UART多处理器通信,其工作原理是主从机设备采用复用漏极开路,主从机外部接上拉电阻,在空闲时使从机处于静默模式,主机要控制从机执行任务时主机发送指令唤醒从机并发送数据控制从机执行相应任务。

2022-02-21 10:05:22 950

950

MM32F013x系列MCU支持UART多处理器通信,其工作原理是主从机设备采用复用漏极开路,主从机外部接上拉电阻,在空闲时使从机处于静默模式,主机要控制从机执行任务时主机发送指令唤醒从机并发送数据控制从机执行相应任务。

2021-01-22 06:33:51 6

6 ADSP-BF561:Blackfin嵌入式对称多处理器数据手册

2021-03-21 06:39:02 9

9 AD14160:Quad-SHARC®DSP多处理器系列过时产品手册

2021-04-15 19:13:10 4

4 AD14060/AD14060L:Quad-SHARC®多处理器DSP系列产品手册

2021-04-25 19:23:54 1

1 EE-202:使用多处理器LDFS的专家链接器

2021-05-14 09:22:30 2

2 EE-167:使用VisualDSP++™的TigerSHARC®多处理器系统简介

2021-05-27 18:39:07 11

11 AD14160 Quad-SHARC®DSP多处理器系列过时数据表

2021-06-16 15:31:36 4

4 在单片机系统中,多处理器是指多个相同类型或者不同类型的单片机协作处理同一个系统的不同工作。它们之间必须具备一定的数据交换和协作处理能力,共同完成一个系统化的工作。不同处理器之间可以采用数据交换方式

2021-06-17 15:41:58 1751

1751

在上一次的灵动微课堂中和大家分享过MM32F013x-UART 9bit通信实例,本次微课堂在此实例的基础上实现UART多处理器通信。MM32F013x系列MCU...

2022-01-25 19:55:23 4

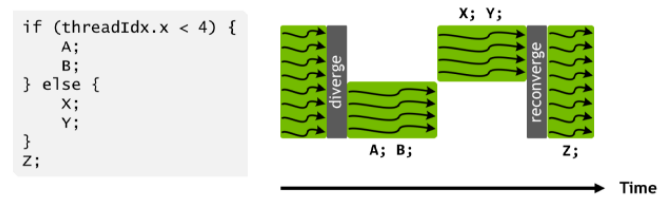

4 按照软件级别,SIMT层面,流式多处理器由线程块组成,每个线程块由多个线程束组成;SIMD层面,每个线程束内部在同一时间执行相同指令,对应不同数据,由统一的线程束调度器(Warp scheduler)调度。

2023-03-30 10:05:37 1370

1370 流式多处理器(Stream Multi-processor,SM)是构建整个 GPU的核心模块(执行整个 Kernel Grid),一个流式多处理器上一般同时运行多个线程块。每个流式多处理器可以视为

2023-04-03 14:28:09 1486

1486

流式多处理器(Stream Multi-processor,SM)是构建整个 GPU的核心模块(执行整个 Kernel Grid),一个流式多处理器上一般同时运行多个线程块。每个流式多处理器可以视为

2023-04-03 14:28:13 1343

1343

ARM Cortex系列那么多处理器,该怎么区分?

2023-10-26 15:45:58 1352

1352

电子发烧友网站提供《基于VPX6—460的多处理器通信设计.pdf》资料免费下载

2023-11-08 14:37:19 0

0 电子发烧友网站提供《基于VPX6-460的多处理器通信设计.pdf》资料免费下载

2023-11-13 10:13:17 0

0

电子发烧友App

电子发烧友App

评论