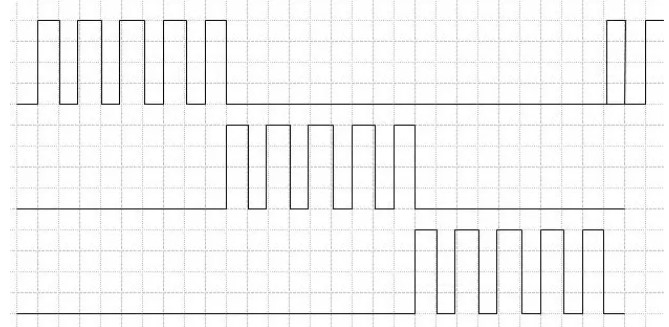

本文介绍了数字I/O和逻辑分析仪的常用术语和定义。

2015-12-31 09:46:02 1235

1235 本文介绍了数字I/O和逻辑分析仪的常用术语和定义。

2016-01-18 10:40:44 1018

1018 “掌握这50个与变频器设计、使用、实施和维护有关的术语定义,将使用户更容易正确地应用变频器。”

2022-09-14 15:52:37 1318

1318 引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-07-08 08:00:00

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

LED光电参数定义及其详解

2012-08-17 21:57:45

OPC UA Specification有哪些术语?分别有何含义?

2021-09-30 07:36:31

OpenGL常用术语解析

2021-03-18 06:57:35

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

LabVIEW的术语VIRTUAL INSTRUMENTS :虚拟仪器,其实VIRLTUAL 真实意思有一层与虚拟截然不同的意思,实质,真实...VIRTUAL INSTRUMENTATION:注意

2009-05-31 08:51:25

本文介绍了数字I/O和逻辑分析仪的常用术语和定义。

2021-05-06 06:39:26

安全的社会。实现这些所不可缺少的是检测状态的“传感器”。【IoT有关的术语定义】IoT: Internet of Things("物体"的互联网)指传感器嵌入到周围物体中,进行联网

2019-03-21 06:20:17

你都了解哪些Zigbee术语?

2021-05-20 07:12:05

接入网及其名词术语你都知道哪些?

2021-05-26 06:19:15

无线通信中的术语介绍

2020-12-21 06:02:30

大家好,时间报告中用红色标记的术语是什么意思?

2020-05-25 15:58:34

电子工程术语与定义列表

2021-02-26 07:12:58

电机行业专业术语

2021-01-26 07:30:36

直播报名:http://t.elecfans.com/live/719.html相关课程:http://t.elecfans.com/topic/45.html电磁兼容 综述 电磁兼容基本术语和定义的应用与解释《资料来自网络》

2019-01-16 22:59:19

磁性材料术语中英文对照及计算定义公式

2012-08-20 15:33:23

13个示波器常用术语解析

2021-03-02 06:40:03

1 范围本标准规定了风力发电机组常用基本术语和定义。本标准适用于风力发电机组。其它标准中的术语部分也应参照使用。

2 定义本标准采用下列定义。2.1 风

2009-03-02 11:56:43 34

34 力值、硬度计量名词术语及定义:1力基(标/校)准机 ( )1.1 力 ( Force) ( )1.2 万有引力 (Universal gravitation) ( )1.3 重力 (gravity) ( )1.4 弹性力 (elastica) ( )1.5 重力加速度 (gravity a

2009-03-11 17:19:29 24

24 本标准规定了移动通信所用的基本术语及其定义,包括移动通信业务、基本技术、移动通信系统及各类移动通信设备涉及的术语及定义等。本标准适用于移动通信的科研、教学、

2009-08-06 11:54:51 18

18 SQL Server术语词汇表

术语 定义 .NET Framework 支持生成、部署和运行下一代应用程序和 Web 服务的必备 Windows 组件。此组件为现有投资与下一代应用程序和服务间的集成提供

2010-03-26 17:29:10 32

32 固体激光材料名词术语 GB/T 11293-1989

本标准规定了固体激光材料常用名词术语的定义。

2010-04-23 14:45:29 8

8 这份术语表汇总定义了TI公司Ddlta-Sigma技术、逐次逼近寄存器SAR)和流水线模数(A/D),并详细说明了它们的桂河和性能特点.

2010-06-01 11:21:48 21

21 器件定义

软件工具概述

选择配置模式

编程/配置选项

XILINX的通用配置/编程的装置

2010-06-22 16:24:01 78

78 1 范围本标准规定了普通照明用LED 和LED 模块及相关的术语和定义。本标准适用于编写有关普通照明用LED 的各类标准及其有关的技术文献。2 犔犈犇和犔

2010-12-22 16:23:02 0

0 主题内容与适用范围本标准规定了可靠性,维修性领域基本的术语及其定义。本标准适用于各类产品所进行的可靠性,维修性活动。基本概念能够被单独考虑的任何元器

2011-01-03 16:32:32 60

60 下列术语和定义取自中国国家标准《无线电管理术语》(GB/T13622-92)、国际电信联盟

2006-04-16 19:01:03 1758

1758

LCD术语

2006-06-30 19:43:47 849

849

电源术语和定义

2006-06-30 19:44:49 1743

1743

技术术语之CPU术语篇

2006-06-30 19:45:16 1130

1130

技术术语之主板术语篇

2006-06-30 19:45:37 943

943 电视机术语

术语解释

一,微分相位:微

2008-10-19 12:13:15 1659

1659

术语、名词定义 1. 黑盒测试

黑盒测试也称为功能测试,它着眼于

2008-10-22 12:49:30 1259

1259 高清数字电视的定义和标准及其相关产品的认证

1.高清数字电视和高清数字电视接收(一体)机的定义数字电视DTV (Digital TV)

2009-05-05 09:15:11 1687

1687 滚动轴承常用术语及定义:轴心线、平面、方向

1. 轴承轴心线 bearing axis 滚动轴承的理

2009-05-14 09:43:58 5871

5871 运动控制术语

运动控制,如其他技术一样,有相当多的专用术语,虽然并非所有的术语都是严格定义的。以下是一些术语,或是耳熟

2009-07-04 08:28:33 1164

1164 有关环境管理物质术语和定义

3.1含有含有系指无论是否有意,所有在产品的部件、设备或使用的材料中添加、填充、混入或粘附的物质(包括在加工过程中无意混

2009-08-12 09:41:12 2591

2591 电池简单分类及其定义

⑴化学电池:将物质的化学能通过电化学氧化还原反应直接转化成电能的一种装置。⑵物理电源:在一定条件下实现能量直接

2009-11-05 08:35:34 1269

1269 CPU专用术语大全

文章内容如下 Intel公司的X86序列CPU以及其它公司所生产的兼容产品,是目前世界上个人电脑中装机最多的

2010-01-12 11:46:41 1029

1029 传感器关于水分常用术语定义

水是生物圈中最重要的物质之一,水蒸气在空气或其它气体中存在与否在很大程度上影响着体系的物理化学和生物过

2010-01-14 16:57:12 648

648 照明相关术语的定义

光 通 量:光源每秒种发出的可见光量之和,简单说就是发光量。单位:流明(lm)

照

2010-01-16 09:18:08 760

760 除胶渣与整孔制程术语定义

1、Conditioning 整孔此字广义是指本身的"调节"或"调适",使能适应后来的状况。狭义是指干燥的板材及孔壁在进入 PTH

2010-02-21 10:04:19 2843

2843 倍显光源技术定义及其工作原理

“倍显”技术应运而生 近年来,随着社会的不断进步,人们物质文化生活有了很大的提高

2010-02-21 16:48:39 439

439 三维多芯片组件的定义及其应用

一、前言

---- 三维多芯片组件(简称3D-MCM)是在二维多芯片组件(即2D-MCM,通常指的MCM均系二维)技术基础上

2010-03-04 14:56:07 1055

1055 综合布线术语大全(表)

术语或符号

英文名

2010-03-10 11:26:24 3259

3259 瞬态抑制(TVS)二极管的术语和定义

电撬设备

该类抑制器具有“电撬”特性,通常与4层NPNP

2010-12-23 11:13:45 2160

2160 1 总则 1 . 0 . 1 编制本标准的目的是为在自控系统及仪表的应用和工程设计中统一基本的术语及其定义。 1 . 0 . 2 内容及适用范围 第2 章 测量和仪表特性术语 这些术语有关测量及其概念

2011-05-06 18:47:51 0

0 这篇报告告诉你如何理解LDO的一些术语和定义,如稳压块的压降,静态电流,待机电流,效率,瞬态响应,线性/负载调整率电源纹波抑制比,输出噪声电压,精度,功耗等。而且在介绍

2011-05-10 14:58:34 73

73 瞬态抑制(TVS)二极管的术语和定义

2011-09-10 23:08:32 2265

2265 作者认为文中对高端彩电的一些术语解释,和分类方法,大部分还是比较确切的。对普通的家电消费者,和一般技术人员来说,具有一定的参考作用。因此推荐于此,供参考。我们期待

2012-01-19 00:37:51 2269

2269 LED 产业与传统照明产业都和照明技术有很大的关係,照明技术与其他任何技术一样,有其专有的术语。这些特殊术语及观念被用来定义灯及灯具的特徴并将测量单位统一化。以下为一些

2012-03-31 15:21:19 59

59 本文介绍连接器常用词汇,包括具体名词(含中英互译)及其相关术语解析。

2013-09-12 11:28:30 3441

3441 本系列标准的这一部分内容,定义了基础术语,并给出了通用信息。基础术语取自与传导和耦合的电骚扰相关的、在其它部分中使用的术语。

2016-04-26 17:53:46 16

16 Xilinx FPGA工程例子源码:EDK中PS2自定义IP

2016-06-07 11:44:14 4

4 LED光电参数定义及其详解

2017-02-08 00:50:11 19

19 摘要 本报告提供的术语和定义一个低压差稳压器(LDO)的理解,并介绍了基本概念,包括电压、静态电流、待机电流、效率、瞬态响应、线路/负载调节,电源抑制,输出噪声电压、精度和功耗。每个部分包括一个例

2017-06-22 16:23:35 20

20 高压开关设备术语及各自的定义 在高压电器产品样本、图样、技术文件、出厂检验报告、型式试验报告、使用说明书及产品名牌中,常采用各种专业名词术语,它们表示产品的结构特征、技术性能和使用环境。了解和掌握

2017-09-08 17:11:38 4

4 本文采用千兆和万兆作为参考而定义了以太网术语,旨在帮助设计师为自己的目标应用选择正确的规范。

2017-09-19 10:56:33 16

16 Xilinx 软件定义开发环境 SDAccel 现已上线亚马逊 AWS,可与亚马逊弹性计算云(Amazon EC2)F1 实例配合使用,让不太熟悉 FPGA 的软件开发人员现在也能够将工作负载的性能提升高达 50 倍之多。

2017-09-22 17:21:34 5342

5342 本文介绍了特高压输电的定义、概况及其过电压与绝缘配合、无功平衡和外绝缘特性等关键技术的分析。

2017-10-19 09:06:00 12

12 GB-T 24826-2009普通照明用LED和LED模块术语和定义

2017-11-20 17:51:15 1

1 Xilinx是全球领先的可编程逻辑完整解决方案的供应商。Xilinx研发、制造并销售范围广泛的高级集成电路、软件设计工具以及作为预定义系统级功能的IP(Intellectual Property)核。

2018-03-23 11:00:29 38729

38729 本文档内容介绍了基于USB连接器型号及其引脚定义,供参考

2018-04-17 11:12:55 14

14 很容易迷失在虚拟现实的术语中,所以在本集中,我们将定义一些在开发虚拟现实体验时会遇到的常见术语。

2020-05-31 12:19:00 974

974 区块链技术相关表包含了常见的区块链术语(概念)及其解释,及进一步阅读参考文章,以加深理解。 方便大家阅读博客或网络上其他文章时做快速索引。

2018-10-19 14:41:24 2828

2828 了解智慧农业中常用术语的定义,这些术语包括农业4.0、农艺数据、物联网、农业即服务、精准农业等。

2018-12-29 14:49:21 4651

4651 想必大家对无人机并不陌生,但是对无人机驾驶员相关的知识就不见得了,在这里我们详细介绍下给无人机驾驶员及无人机执照相关的术语定义。

2020-05-15 10:58:47 1700

1700 各种变频器说明书中有很多与时间有关的概念与术语,现将它们的定义解读如下。

2020-11-13 17:46:22 4981

4981 振荡器是一种在输出端子上产生AC信号的设备。“振荡”这个术语可以定义为“以有规律的速度往复运动”。

2020-12-27 11:04:43 7011

7011 引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

2021-05-01 09:47:00 10367

10367

我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。

2021-04-27 10:45:29 5650

5650

本标准规定了印制电路技术的常用术语及其定义。

2021-06-23 11:53:06 0

0 解决方案,满足了5G时代各种不同业务的差异化需求。 Flex-Algo主要术语定义 Flexible Algorithm Definition —— 一组计算类型、参数类型、约束条件的组合

2021-09-03 16:07:19 2599

2599 本文汇总和定义模/数转换器(ADC)和数/模转换器(DAC)领域常用的技术术语。

2022-04-15 12:59:51 2491

2491 下面我们从下到上依次来看一下各个定义。

2022-04-20 08:17:42 2297

2297 脉冲宽度调制 (PWM) 的良好定义就在名称本身。为了更好地理解 PWM 是什么,让我们首先看一些基本术语。

2022-11-23 16:49:38 1667

1667

随着工业互联网的发展和新理念、新技术的引入,围绕工业互联网出现了大量术语和定义。本篇文章主要对工业互联网术语和定义进行了汇总和梳理,可用于统一业界对关键术语和定义的认识和理解,加深应用。

2023-01-11 13:52:11 420

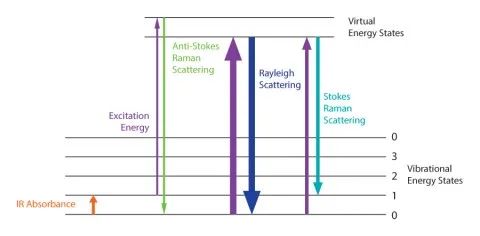

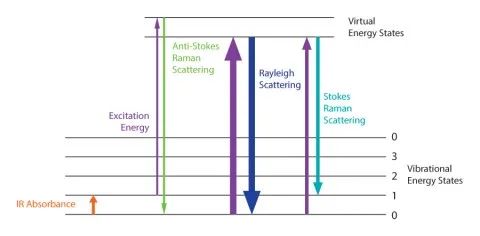

420 光谱学术语与定义可以帮助大家理解那些在海洋光学的产品介绍与报告中经常提到的术语。但根据我们的经验,即使是相同的术语,在不同产品的描述和定义上也会有细微的差别。

2023-04-12 10:30:28 955

955 光谱学术语与定义可以帮助大家理解那些在海洋光学的产品介绍与报告中经常提到的术语。但根据我们的经验,即使是相同的术语,在不同产品的描述和定义上也会有细微的差别。

2023-04-12 10:30:47 1547

1547 光谱学术语与定义可以帮助大家理解那些在海洋光学的产品介绍与报告中经常提到的术语。但根据我们的经验,即使是相同的术语,在不同产品的描述和定义上也会有细微的差别。

2023-04-12 10:30:55 1058

1058

测试中,我们经常会做校准,校准的定义有很多层面的,比如这些常见的术语: Calibration, Normalization/ Correction , Self-Test, Auto-Zero

2023-06-14 07:45:02 603

603

编辑搜图有机发光二极管照明术语和文字符号1范围本标准规定了有机发光二极管(OLED)照明优先采用的术语及其定义、文字符号及其单位。本标准适用于OLED作为照明光源的器件、屏、模块、灯具。2术语和定义

2022-04-08 10:28:16 220

220

有机发光二极管照明术语和文字符号1范围本标准规定了有机发光二极管(OLED)照明优先采用的术语及其定义、文字符号及其单位。本标准适用于OLED作为照明光源的器件、屏、模块、灯具。2术语和定义2.1

2022-03-25 09:24:01 213

213

在上期文章中,我们了解了现代GNSS模拟中的软件定义架构,并与传统架构进行了对比,本期文章中我们将继续深入探讨软件定义架构及其意义。

2023-02-08 10:40:48 400

400

作者|冰糖葡萄皮小编|吃不饱汽车世界在不断发展,“软件定义的汽车”等新术语证明了软件对当今汽车的重要性。无论是MiL、SiL、PiL、HiL、还是单元测试、集成测试,汽车软件测试的世界有很多技术术语

2023-06-13 10:45:03 467

467

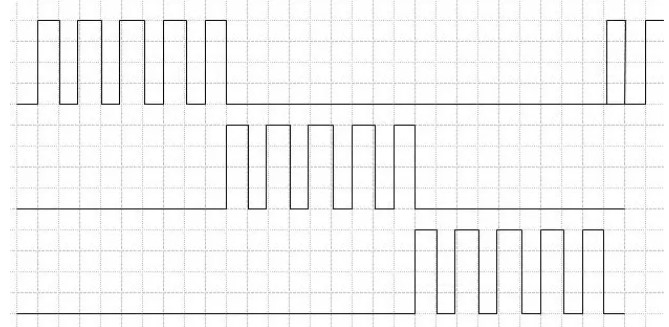

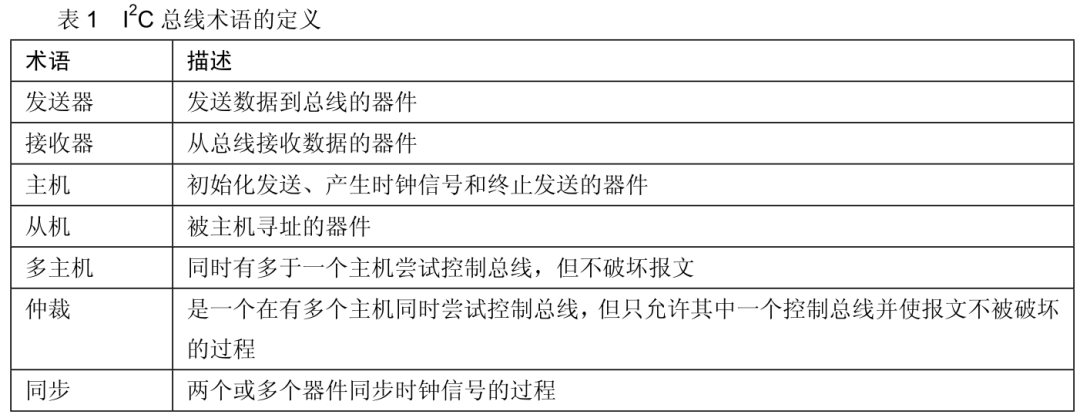

定义术语 1、数据有效性 在 SCL 高电平期间,SDA 必须稳定,所以一般情况下,SCL 高电平宽度小,SDA 高电平宽度大,用示波器看也是这样的。 2、起始条件和停止条件 起始条件:SCL

2023-07-25 09:36:41 264

264

焊接术语即焊接领域的专门用语,比如:短路过渡-熔化极气体保护焊过程中,焊丝通过反复的短路熔敷;飞溅-熔焊过程中排出而不成为焊缝一部分的金属颗粒。

2023-08-21 10:41:55 729

729

电磁兼容基本术语和定义的应用与解释

2022-12-30 09:21:53 2

2 在探讨半导体业界的常用术语前,我们需了解半导体行业是科技领域中最为活跃且技术含量极高的行业之一。它涉及到许多复杂的工艺和理论,因此产生了大量专业术语。以下是一些半导体业界常用的术语,及其解释。

2023-12-02 11:18:05 971

971

物联网领域有许多关键术语和缩写词。我列出了一些常见术语。由于物联网的范围极广,因此我无法在本帖中列出所有术语。请在此列表中添加任何可能对他人有益的术语。

2023-12-28 09:40:23 255

255 电能质量标准术语大揭秘,从PU到谐波源阻抗,一网打尽!电压暂降、谐波幅值,轻松搞定!

2024-01-15 11:44:22 221

221

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 215

215

电子发烧友App

电子发烧友App

评论