fpga I/O 引脚都一样吗?为什么有些管脚只能分配为输入,有的只能为输出?求大神指点

2015-05-27 08:12:40

时,一切看起来正常,但是I/O管脚没有问题。我把它们配置得很低。我不能像为XC8分配代码配置器那样给他们命名。如果有代码来处理I/O引脚,我试着用定时器0让他们闪烁。谢谢。

2019-10-21 06:38:23

这里写目录标题I/O端口原理单片机知识点补充实战1——闪烁LED指示灯I/O端口原理I/O英文全称是 Input/Output,即输入/输出。单片机端口是标准双向口,就是说,单片机的端口既可以

2022-01-20 07:55:51

组合运用多种智能IO规划工具能使引脚分配过程变轻松.pdf(195.84 KB)

2019-04-24 11:43:12

轻松实现高速串行I/OFPGA应用设计者指南输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐

2020-01-02 12:12:28

MSP连接到同一存储区的用户I / O引脚。由于某种原因,与ADC的数字化数据引脚接口的FPGA的一些用户I / O引脚被损坏。我们已经生产了6块FPGA板,所有这些板都在相同的引脚上出现问题。我已经

2020-04-07 12:26:15

选择输出模式(开路或推拉)模式寄存器(PnMDOUT)。第三步。使用端口跳过寄存器(PnSKIP)选择I/O交叉开关要跳过的任何管脚。第四步。将端口引脚分配给所需的外围设备(XBR0、XBR1)。第五步。启用纵横制(XBARE=‘1’)。...

2022-01-24 07:51:32

嗨, 我想把晶体振荡器的CLK带到FPGA里面的数字设计。该CLK连接到FPGA的I / O引脚。如果我在映射中运行Impliment设计,我将得到错误。所以我将在UCF文件中将网名命名如下。NET

2019-01-29 10:05:43

/1732.html由于核电厂工艺复杂,控制设备众多,导致控制和测量点的数量非常庞大;同时,传感器和执行机构的类型也是多种多样,供电方式、信号类型也有所不同。面对如此复杂的情况,将所有I/O点数合理地分配

2018-02-22 13:18:08

,选择生成的.tcl文件,点击Run,引脚分配完成。 说明:在实际的应用过程中,我们应该根据工程的子模块个数和引脚的使用多少来选择合适的引脚分配方式,笔者总结了以下几条:(不喜勿喷,还望多多赐教)1

2018-07-03 07:22:06

`引脚分配规划和扩展I/O电路本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 核心板上专门留了一个LED

2015-05-06 11:31:16

电路设计的可选择性丰富而言的。话说回来,这里的“自由”也还是要建立在一定的基础之上的。笔者根据多年的工程经验,对于I/O与外设的连接扩展,归纳出以下一些要点:●输入和输出时钟信号尽量分配到专用的引脚

2019-04-12 06:35:33

/O信号分配 可提供最多的多功能引脚、I/O标准、端接方案和差分对的FPGA在信号分配方面也具有最复杂的设计指导原则。尽管Altera的FPGA器件没有设计指导原则(因为它实现起来比较容易),但赛灵思

2020-09-07 11:01:46

单元有关的I/O引脚的文档。有人能给我指出正确的方向吗?谢谢。 以上来自于百度翻译 以下为原文 I'm planning the use GFX module on PIC24J256DA206

2018-10-17 16:26:01

使用INIT_B引脚(内部路由)作为标记非FPGASEU检查结果的通用I / O,此外还可以根据积分配置错误检查结果进行驱动。我看到INIT_B被描述为“Dedicated”(UG362,表2-2,第27页),所以我不确定它是否可以作为通用I / O运行。如果没有,我需要专门为此目的的另一个输出引脚。

2020-06-10 15:09:16

工业4.0指出了结合智能通信进行深入自动化趋势。因此,在过程工程、工业自动化和设备管理中,PLC需要配备更多的I/O端口。如果空间有限,控制器无法放入更多基板面,那么,我们必须增加模块密度才能支持

2022-11-16 07:41:11

我想知道是否有必要在“引脚工具”实用程序中分配所有电源引脚。

2023-05-09 09:00:46

STM32单片机---(二)I/O应用stm32I/O简介GPIO的8种工作模式stm32I/O简介在 STM32 中I/O 引脚,又称为GPIO (General-Purpose I/O),可以被

2022-02-16 07:04:02

,/BIO引脚作为单向输入,同时5410A的片上外设没有I2C接口,所以,当5410A需要控制外围芯片或与其他芯片进行通信时(如I2C通信),必须扩展通用I/O口,本文首先介绍5410通用I/O口的多种扩展

2018-12-04 10:35:48

的Aurora示例设计编写了我的Xdc文件。合成后,我打开合成设计,在I / O规划中,我可以在E2中分配o_tx_p的串行引脚,而在F8中分配i_rx_p。我检查了VC707的shcematic,我确信

2019-03-01 09:18:11

将这些信号和FPGA的引脚进行映射。 如图所示,点击ISE菜单上的“Tools à PlanAhead à I/O Pin Planning(PlanAhead) – Pre-Synthesis…”选项

2015-10-14 12:23:31

你好,我目前正在为我的Zynq 7020 FPGA做一个RTL引脚规划。我有一个非常基本的问题。我在PL EMI上的PS和AXI EMC v3.0 ip核心上只有很少的接口。在合成之前,我可以为此IP核进行引脚规划吗?另请告诉我针脚规划的整个步骤。

2020-04-10 10:21:22

我得到了pic32层套件三,所以sisapoint的I/O不能使用,因为它的平面奇怪连接器和昂贵的电路板是非常昂贵的!因此,我只想开始学习pic32使用3led板和3swuitch按钮,但当我建立

2019-10-28 13:23:56

我使用的是XC2s100e,有很多未使用的I / O引脚。做我必须使用外部上拉电阻或连接到地,否则我可以留下未使用的引脚悬空。未使用/未连接的引脚是否会导致任何故障模式?谢谢以上来自于谷歌翻译以下

2019-05-10 07:23:02

通讯等多种功能的家居控制系统。1.收集该智能家居套件的相关资料,包括原理图、例程及开发工具等;2.构建开发环境,具备程序下载的能力;3.使用I/O口实现对LED、RGB_LED、蜂鸣器、继电器

2020-09-25 10:04:06

今日讲解程序框图组合运用,利用While循环,条件结构,事件结构,反馈节点等多种程序框图编译小程序《温度采集》。程序界面如下:程序要求:点击开始采集按钮,采集进度条进行累计加一,同时随机输出

2020-08-05 21:24:14

其他14个I/O引脚。当我把这个引脚连接到作用域时,它看起来是浮动的。我假设我需要使用c配置位(这是我在pin8[OSCO]遇到同样的问题时所做的——我写过),但我似乎找不到什么。谢谢。

2019-08-22 13:10:44

本文旨在以具体案例探讨企业如何进行IPv6地址规划与分配,从而合理和有效地使用IPv6地址资源。

2020-12-28 07:14:11

大家好,我使用i / o规划为我的项目分配了引脚。我还需要在.xdc文件中写相同的内容吗?当我们修改i / o规划时,.xdc文件会自动修改吗?提前致谢,问候,Reshma以上来自于谷歌翻译以下

2018-11-06 11:35:37

##学习笔记一.相关表格1.PB3,PB4,PA13,PA14,PA15引脚可根据上表复用成普通IO口。在mcu复位的时候这几个引脚被作为jtag的功能。当我们要使用这些引脚作为普通的I/O时必须

2022-03-01 07:03:32

在使用数字I/O之后,PIN是否已经不再使用PIN?我有PSoC开发工具包和无意中分配一个数字I/O函数P0.5然后纠正分配回CapSense功能…,港口不再功能…CapSense功能我可以重新分配

2019-02-14 15:26:21

本文探讨的重点是PCB设计人员利用IP,并进一步采用拓扑规划和布线工具来支持IP,快速完成整个PCB设计。从图1可以看出,设计工程师的职责是通过布局少量必要元件、并在这些元件之间规划关键互连路径

2018-08-30 16:18:04

`勇敢的芯伴你玩转Altera FPGA连载49:PWM蜂鸣器驱动之引脚分配特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i

2018-02-27 21:50:07

,我找不到一个命令,我可以为其指定一个引脚子集,然后让工具只考虑它们。例如说我有四个可能的I / O引脚,AB1,AB2,AB3和AB4和内部有四个数据引脚D1,D2,D3,D4。如何让工具为这些数据

2018-10-22 11:05:25

大家好,我刚开始学习FPGA并试图弄清楚哪些FPGA引脚可以分配我的数据信号。我正在使用FPGA Spartan 6封装TQG114器件LX9。查看产品规格,有102个可用的用户I / O.这是

2019-04-23 06:55:23

嗨,我希望有人可能有经验,可以推荐一个可以支持的工具包:65个输出引脚5个输入引脚所有I / O引脚均可在1.8V电压下工作更多的I / O引脚将是一个奖励。我找不到一个带有足够I / O引脚的扩展

2019-08-21 09:59:25

在QUARTUSII9.1中怎样设置才能使EPM7256AE的普通I/O脚变为时钟输入脚:

2012-10-20 23:09:07

STM32 I/O引脚烧坏现象,检测方法以及原因分析(IID:从不产生代码和电路,只是代码和电路的搬运工)背景前言:在最近的项目中遇到两次烧坏STM32 I/O引脚的情况,第一次烧坏是在机器运行了有

2020-11-28 21:00:22

针对目前家庭智能化所存在的功能规划不详尽、设备功能单一、运用技术参差不齐等缺点,本文运用现场总线LonWorks技术开发家庭智能控制系统,来实现家庭中三表计费、三防(防火、防灾、防盗)、室内环境

2021-06-17 07:30:00

针对目前家庭智能化所存在的功能规划不详尽、设备功能单一、运用技术参差不齐等缺点,本文运用现场总线LonWorks技术开发家庭智能控制系统,来实现家庭中三表计费、三防(防火、防灾、防盗)、室内环境

2021-06-23 07:30:00

大家好,我使用PIC18F4620 40PIN DIP封装,大约30的I/O引脚没有使用。我不知道我应该把它们留在硬件中,还是应该把它们绑定到VDD或VSS?在软件中也推荐使用未使用的I/O引脚

2019-01-25 14:33:08

IAM使用PIC32 MX795F512LMI设备I/O与MIL连接器引脚连接,能帮助我计算I/O引脚上的输出电压吗? 以上来自于百度翻译 以下为原文 Iam using

2019-04-18 06:14:54

我正在使用cusotmised Virtex 6 Fpga(V6_XC6VLX550T封装FF1760)我正在尝试使用VREF和VRP和VRN引脚作为用户I / O引脚。任何人都可以帮助我,我能否根据我的要求使用这些引脚..

2020-06-11 12:06:58

=1;}我对pwm没有问题(这不是整个代码),I/O端口引脚有问题。当我调用init_pwm1函数并启用pwm时,我不能使用这些引脚(B10和B11)作为I/O引脚,我需要将它们设置为1或0,但我不能

2019-10-21 12:16:33

如何克服FPGA I/O引脚分配挑战?

2021-05-06 08:57:22

如何在PlanAhead I / O引脚分配中启动LVDS系统时钟? I / O STD列中没有LVDS选项?

2019-09-17 08:19:59

我需要使用PIN RA2作为其他职责,因为我的电路没有备件。我使用内部比较器来产生中断,但引脚RA2镜像在引脚上的比较器O/P。我没有多余的I/o,因此我不能使用PPS来重定向。看看比较器图,看起来

2019-10-29 14:01:33

你好先生:我有一个关于Spartan-6时钟I / O引脚的问题,数据表“UG382第24页”就是说“P和N输入遵循与时钟输入引脚上的标准输入相同的配置”,但我不知道其含义这个描述。我想这意味着

2019-07-15 14:04:11

你好Xilinx收发器使用CML IOSTANDARD。在xilinx 7系列示例设计中,有固定的GTREFCLK位置,但其他引脚未配置(txdata / rxdata)在下面的I / O表中,txdata和rxdata引脚未配置CML I / O标准。我如何配置CML I / O标准?

2020-08-13 10:10:53

MCU通用I/O引脚扩展 低端MCU由于I/O口数量不足导致部分功能无法实现,用户需要使用数字集成芯片进行扩展,如74LS系列移位寄存器,但是这种集成芯片也会由于引脚数量限制而无法确保单片机端口

2024-01-08 09:35:10

使用器件XC2S100E-6TQ144,我需要将4个GCK引脚中的3个配置为通用I / O引脚。第4个GCK用作100MHz时钟。当我使用其他3个GCK引脚作为通用I / O引脚时,在“器件

2019-05-08 08:00:24

您好!我将一个设计从EZ-UBFX2LPU微控制器迁移到EZ-UB-FX3。以前,我用I/O引脚控制一个缓慢的外围设备(2×16字符液晶面板与8位数据总线)。这是容易的-我刚才写了我想要的值在LCD

2019-09-11 09:08:41

你好,我正在使用ISE 14.1在CPLD(XCR3256XL)上实现设计。我完成了原理图,包含了所有I / O引脚并命名。原理图包含6个解码器和大量基本逻辑门(AND,NOR等)。当我选择我的顶级

2020-04-21 09:43:50

什么是I/O和控制引脚上的总注入电流?所有I/O和控制引脚上的总注入电流的值是多少?

2021-10-15 09:36:08

UG917,并在表格下方注明:1. CCLK是专用引脚,不需要IOSTANDARD或LOC属性。同时,我们在I / O规划板中找不到引脚“AA9”。所以,这个问题,如果我们不指定具体的位置约束,就会出现错误,如果我们想要指定特定的位置约束,我们就找不到建议的引脚数。我该怎么办?谢谢您的回答。

2019-10-17 09:01:19

通过前面的输入输出的内容(LED控制与按键的使用),我们对控制I/O口有了一个基本的了解。如果需要输出高低电平,可以对该引脚进行写"1"或者"0";如果需要

2022-01-24 07:38:13

你好。我来自俄罗斯,因此我为我的英语道歉。我在工作台ML402.I面临以下问题。在Virtex 4(XC4VSX35)“固件”期间,I / O输出状态处于高电平('1')。对于我的项目,这是不可接受的。是否有可能使I / O的固件输出期间处于低电平('0')?谢谢。

2020-06-18 08:51:59

大家好,物理封装引脚分配完成后,ISE自动推断I / O芯片分配使用LOC约束。有没有办法明确分配特定的I / O芯片垫?谢谢。以上来自于谷歌翻译以下为原文Hi All, ISE

2019-02-14 12:12:04

大家好,我想检查FPGA功能和I / O引脚功能在我的主板上使用“Selftest application”。在我的Selftest应用程序中,我可以使用哪些方法来检查这些?请提供一些想法。谢谢

2019-04-01 12:33:26

这是一个关于 CX3 上未使用的 I/O 引脚的简单问题。CYUSB306X 数据表(第 20 页)建议 \" 应使用内部上拉电阻 \" 将所有未使用的 I/O 拉高。 但是,我

2024-02-22 06:55:29

求西门子PLC控制沼气发电程序 I\o分配表谢谢

2016-10-15 16:16:11

你好,我使用PIC16F18326,并且用I/O引脚(RC0)供电电路。PIC在3.3伏特上运行,IO引脚是高的,所以它有3.3伏,直到它连接到电路,我想它的权力,然后它下降到2.8伏。它为I

2018-12-26 16:05:54

1、明确硬件总体需求情况,如CPU处理能力、存储容量及速度、I/O端口的分配、接口要求、电平要求、特殊电路要求等等。2、根据需求分析制定硬件总体方案,寻求关键器件及相关技术资料、技术途径和技术支持

2017-09-07 10:55:59

请问一下能不能使用软件进行系统规划?

2021-04-28 06:28:34

我需要为我的项目使用100Mhz时钟信号,我正在使用Zynq zc706板。我添加了我的clcok信号原理图。我的问题是我不知道我应该将哪个引脚用于我的时钟信号。我读了很多文件,比如/系列时钟规划或引脚和包装。我不能使用系统时钟引脚,因为它是o LVDS I / O st。有没有针的建议。我很困惑

2019-10-09 08:32:42

嗨,有没有可能使用PGM/PGC/PGD作为I/O引脚,并用它们来编程这些引脚的C?我怎样才能做到呢?也有可能用ASPEL(ATMEGA61M1)做“SPI编程”引脚吗?非常感谢你!祝您有个美好

2019-03-18 13:33:22

模拟引脚能否简单地用于数字I/O?

2019-09-10 05:55:35

如果通过Cros***ar寄存器使能并分配为P0.0和P0.1引脚,那么,我还可以用这两个引脚为通用I/O吗?

2019-09-09 02:26:57

通过实例在Matlab中展现了基于动态规划法,解决电力资源合理分配的问题,使得现实中电力资源的分配问题得到简化和程序化。结果显示,动态规划法在电力资源的合理分配问题上比较实用

2011-12-07 14:15:08 19

19 网组网和规划过程中遇到的一些问题,提出了相应的解决办法。既然是试验网,那么各种新的组网思想、方法和设计方案都可以在试验中充分运用和分析比较,以便在实践中探寻出一套最优的组合,以最佳的状态、最好的身手迎接即将到来的3G大潮。

2017-12-13 09:50:02 788

788

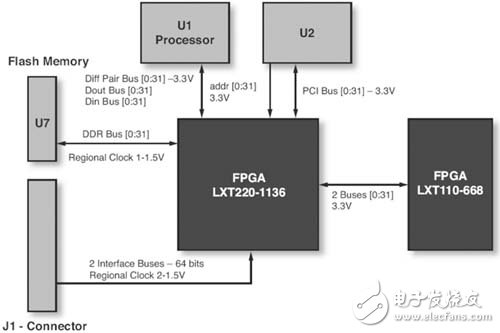

对于需要在PCB板上使用大规模FPGA器件的设计人员来说,I/O引脚分配是必须面对的众多挑战之一。 由于众多原因,许多设计人员发表为大型FPGA器件和高级BGA封装确定I/O引脚配置或布局方案越来越困难。 但是组合运用多种智能I/O规划工具,能够使引脚分配过程变得更轻松。

2019-06-03 08:06:00 2312

2312

电子发烧友App

电子发烧友App

评论