廉价的双倍数据速率(DDR)内存(以及DDR2和DDR3等后来的版本)为台式机和笔记本电脑的工作内存提供了支柱。通过在脉冲序列的前沿和后沿上为存储器提供时钟,存储器吞吐量加倍,而功耗仅略微增加。

2019-03-25 08:48:00 4083

4083

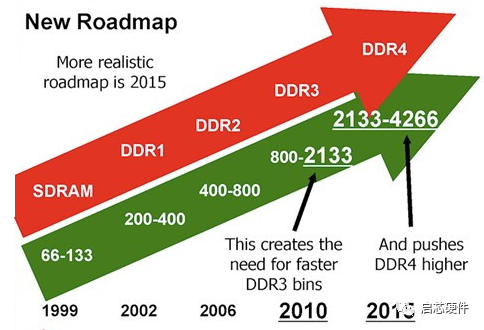

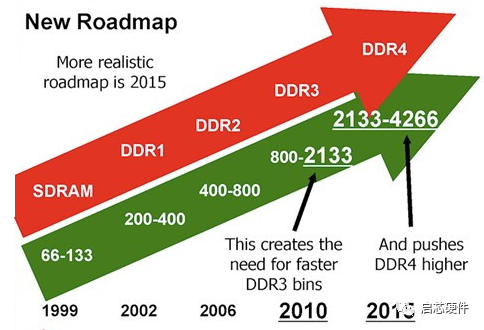

DDR存储器发展的主要方向一言以蔽之,是更高速率,更低电压,更密的存储密度,从而实现更好的性能。

2023-10-01 14:03:00 491

491

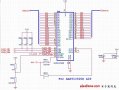

描述此参考设计展示了适用于 DDR3 和 DDR4 存储器的通用电源解决方案。同步降压转换器为 DDR3L 配置中的 9A 负载提供 1.35V 输出电压。线性稳压器提供为 2A 负载提供

2018-12-24 15:08:56

Altera公司近期宣布,开始交付业界第一款高性能28-nm FPGA量产芯片。Stratix V FPGA是唯一使用TSMC 28HP工艺制造的FPGA,比竞争解决方案高出一个速率等级

2012-05-14 12:38:53

Altera_Stratix_V_FPGA提供RLDRAM_3存储器支持

2012-08-13 22:17:28

DDR4 DESIGNDDR4 DESIGNDDR4 DESIGN拿走拿走!

2015-04-24 18:06:37

DDR4 SDRAM的封装和寻址你好! 这是你第一次使用 Markdown编辑器 所展示的欢迎页。如果你想学习...

2021-07-29 06:58:22

(UG583)“UltraScale架构PCB设计用户指南”的V1.10表示(通常)DDR4接口信号reset_n不需要满足适用于地址/命令/控制组中其他信号的偏移约束。但是,在专门引用DDR4

2020-08-27 17:10:06

、DRAM、DDR4。先说存储器,说到存储,顾名思义,它是个动词,以生活为例,假如有个酸奶,你不想吃的时候,将酸奶存到某冰箱、某层、某个位置,当你想吃的时候,在某冰箱、某曾、某个位置中取出该酸奶。这个过程,我们称为存储,结合生活,我们可以看到存储要有3个关键动作: 酸奶放哪了,你得知道。如果不知道放哪了

2021-11-11 07:13:53

DBI示例5 Error Detection功能随着DDR4数据速率的提升,误码率也随之提升,故DDR4中增加Error Detection技术对DQ和CMD、ADD信号。对于DQ信号使用内置的CRC

2019-11-12 12:40:17

由FPGA负责将数据分两路输出。 该系统对存储器的要求是能够高速地存储大量的数据,DDR SDRAM正好能满足这一要求,此时,FPGA是否能对DDR SDRAM进行有效控制就成为影响系统性能的关键

2018-12-18 10:17:15

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-24 05:00:34

还未接触过DDR4,在LAYOUT颗粒设计中,布局布线上DDR3与DDR4有没有区别?有哪些区别?

2019-03-07 10:11:39

传输;而DDR内存则是一个时钟周期内传输两次次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据

2011-02-27 16:47:17

Arria 10 FPGA和SoC设计中实现,666 Mbps DDR4存储器数据速率。三、Lattice官网:http://www.latticesemi.com建立时间:1983总部:Hill

2018-01-29 11:05:29

内存设备:

•双倍数据速率3(DDR3)SDRAM。

•低压DDR3 SDRAM。

•双倍数据速率4(DDR4)SDRAM

2023-08-02 08:30:00

`直播链接:http://t.elecfans.com/live/574.html直播内容及亮点:详解DDR高速存储器模块的布局布线的设计思路,从原理图分析到PCB布局布线,从一片到两片、四片DDR

2018-10-10 11:49:20

® ALTMEMPHY宏功能来构建所有的 DDR2或者 DDR SDRAM外部存储器。通过将 Altera DDR2 或者 DDR SDRAM 存储控制器、第三方控制器或者定制控制器用于特定的应用需要,可以实现控制器功能

2017-11-14 10:12:11

MT40A512M16LY-075E:B MT40A1G8SA-075:EMT29F64G08CBABAWP:BMT40A256M16GE-083E IT:BMT40A512M8RH-083E:B 镁光DDR4 时时发集团亚洲有限公司 QQ:535553245

2019-02-18 10:51:21

支持Xilinx FPGA中的32位 DDR4 SDRAM

2020-12-29 06:30:15

自旋转移扭矩磁阻随机存取存储器(STT-MRAM)是一种持久性存储技术,可利用各种工业标准接口提供性能,持久性和耐用性。 Everspin推出了STT-MRAM产品,该产品利用称为JE-DDR4

2021-01-15 06:08:20

目前在用FPGA+CYUSB4和PC机通讯,传输速率较低。设计时没有加DDR2存储器,是否导致该问题。

2024-02-29 07:28:57

为什么有的电子设备用eMMC存储器 ?而有的用DDR存储器呢?这两者有什么区别吗?

2021-06-18 06:13:25

DDR2电路设计在高速大数据的应用中,高速大容量缓存是必不可少的硬件。当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR

2016-12-30 20:05:09

DDR4存储器模块面世,运作电压同样在1.2V,同时宣布预计在2012年下半年开始大批量生产。此后的2012年5月,美光宣布将在2012年后期使用30nm制程生产DRAM及闪存颗粒。然而直到2014年

2022-10-26 16:37:40

的提升。出色的功耗和更加强劲稳定的性能给多任务处理和运行大型游戏提供了坚实的硬件基础,所以,朋友们在装机的时候最好选择DDR4高频低功耗的产品,这样才能DIY出一台优秀的PC,你们说是吗?

2019-07-25 14:08:13

,它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM 相同的总线

2019-08-01 10:17:46

28.05G和14.1Gbps收发器,与前一代器件相比,收发器功耗降低了50%; b. 1,066 MHz的6 x72 DDR3存储器接口; c. 2.5 TMACS信号处理性能; d. PCI

2012-09-21 13:49:05

佛山回收DDR4高价回收DDR4,佛山专业收购DDR4,深圳帝欧电子长期现金高价回收DDR4。帝欧电子赵生 ***,QQ:764029970//1816233102,mail

2021-07-15 19:36:21

佛山回收DDR4高价回收DDR4,佛山专业收购DDR4,深圳帝欧电子长期现金高价回收DDR4。帝欧电子赵生 ***,QQ:764029970//1816233102,mail

2021-12-27 19:25:08

内存储器在基于FPGA的嵌入式系统的存储器中具有最高吞吐量和最低反应延时。它的反应延时通常仅为一个时钟周期。通过流水线操作访问存储器,可以使吞吐量达到每个时钟周期进行一次数据处理。片内存储器的另一个好处

2016-10-10 17:08:22

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA进出。DDR3存储器系统在大多数情况下可以为这些基于FPGA的系统

2019-05-27 05:00:02

选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足

2019-06-24 06:07:53

高性能系统设计师在满足关键时序余量的同时要力争获得更高性能,而存储器接口设计则是一项艰巨挑战。双倍数据速率SDRAM和4倍数据速率SDRAM都采用源同步接口来把数据和时钟(或选通脉冲)由发射器传送

2019-04-29 07:00:06

Nios II系统中的紧耦合存储器是旁路缓存的片上存储器,该存储器具有最好的存储器访问性能,能采用与其它存储器一样的方法为之分配代码和数据。图1是包括紧耦合存储器和其他外设的Nios II系统图

2018-12-07 10:27:46

基于Xilinx FPGA的DDR2 SDRAM存储器接口

2012-08-20 18:55:15

DDR3存储器控制器面临的挑战有哪些?如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

2021-04-30 07:26:55

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

影响存储器访问性能的因素有哪些?DSP核访问内部存储器和外部DDR存储器的时延有什么不同?

2021-04-19 08:32:10

存储器件,带宽为32 bit,时钟速率为200MHz,数据速率为400 Mbps。视频解码芯片为TVP5147,视频DAC 采用高性能ADV7123。

2019-08-29 08:07:33

存储器的带宽提出了越来越高的要求,传统的DDR4带宽显然已经无法满足要求,Achronix看重了GDDR6在数据存储中的带宽优势,创新地将GDDR6引入到了FPGA,彻底解决了传统FPGA存储带宽不够

2021-12-21 08:00:00

描述此参考设计介绍高可靠性应用(基于 66AK2Gx 多内核 DSP + ARM 处理器片上系统 (SoC))中具有纠错码 (ECC) 支持的双倍数据速率 (DDR) 存储器接口的系统注意事项。其中

2018-10-22 10:20:57

作者:Robert Taylor1德州仪器双数据速率同步动态随机存取存储器。哇!真够拗口的。很多人甚至可能都不认识这个全称;它通常缩写为 DDR 存储器。图 1 是 PC 中使用的 DDR 模块图

2018-09-18 14:11:40

未来DDR4、NAND Flash存储器芯片该如何发展

2021-03-12 06:04:41

数据存储器 FLASH程序存储器 FLASH数据存储器 片内RAM数据存储器16M字节外部数据存储器各有什么区别?特点?小弟看到这段 很晕。ADuC812的用户数据存储器包含三部分,片内640字节的FLASH数据存储器、256字节的RAM以及片外可扩展到16M字节的数据存储器。求助高手。解释一下不同。

2011-11-29 09:50:46

在用DM642处理图像数据过程中,摄像头采集回来数据后是先存入ddr存储器,然后cpu从ddr中提取数据在进行处理,在进行输出,是这个过程吗?

2015-11-29 15:20:55

深圳专业收购DDR4深圳长期高价回收DDR4,专业收购DDR4,深圳帝欧电子长期现金高价回收DDR4。帝欧电子赵生 ***,QQ:764029970//1816233102,mail

2021-01-30 17:36:35

回收DDR4,收购DDR4,24h开心财富热线:赵生--135-3012-2202QQ-8798-21252 帝欧电子长期专业高价回收flash, 回收DDR,回收手机字库。回收全新flash,回收

2021-09-08 14:59:58

怎么用FPGA检测内存条DDR4坏的单元数呢?1.我可以用一个仅支持DDR3的memory controllor的FPGA和作为一个平台吗?(有人说只需设置下FPGA就可以,不知道是不是这样的)2.

2016-09-28 14:35:54

本帖最后由 dealicdz 于 2021-3-30 15:41 编辑

苏州专业收购DDR4晓色又侵窗纸。窗外鸡声初起。苏州长期高价回收DDR4,专业收购DDR4,深圳帝欧电子长期现金高价回收

2021-03-17 17:59:10

适用于Xilinx Virtex-7 FPGA开发板的32位DDR4 SDRAM

2020-12-30 07:39:14

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-03-04 11:13:54

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-03-11 11:07:39

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-03-18 11:16:02

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-03-25 11:34:03

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-04-01 10:53:42

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-04-11 14:45:24

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-04-18 14:12:57

功能特性q FPGA处理器性能:Ø FPGA处理器型号:EP4SGX530NF45I3N;Ø 逻辑资源:共有212480个ALMs,共有531K个LEs,共有424960个寄存器;Ø 存储器资源:共有

2016-04-27 11:51:14

利用Virtex-5 FPGA迎接存储器接口设计挑战:在不支持新的接口协议时,存储器接口设计师总是试图支持越来越快的接口总线速度。目前,源同步双数据速率 (DDR)存储器件,例如 DDR2 SDRAM

2010-04-25 10:28:16 57

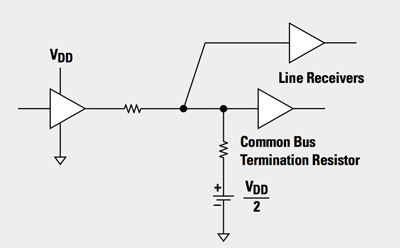

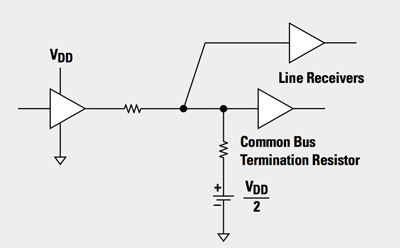

57 日前,德州仪器 (TI) 宣布推出一款可满足 DDR、DDR2、 DDR3 与 DDR4 等各种低功耗存储器终端电源管理要求的汲极/源极双数据速率 (DDR) 终端稳压器 TPS51200。该简便易用

2008-09-01 15:28:44 1906

1906 用中档FPGA实现高速DDR3存储器控制器

引言

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(D

2010-01-27 11:25:19 879

879

DDR4,什么是DDR4

DDR 又称双倍速率SDRAM Dual Date Rate SDRSM DDR SDRAM 是一种高速CMOS动态随即访问的内存美国JEDEC 的固态技术协会于2000 年6 月公

2010-03-24 16:08:39 3146

3146 Altera公司日前演示了使用FPGA的浮点DSP新设计流程,这是业界第一款基于模型的浮点设计工具,支持在FPGA中实现复数浮点DSP算法。

2011-09-15 09:07:10 613

613 Altera公司(Nasdaq: ALTR)今天宣布,开始批量发售FPGA业界性能最好、具有背板功能的收发器。

2012-08-03 09:38:03 865

865 FLASH存储器接口电路图(Altera FPGA开发板)

2012-08-15 14:36:31 6269

6269

使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 All Programmable技术和器件的全球领先企业赛灵思公司 (NASDAQ: XLNX)今天宣布推出业界首款面向All Programmable UltraScale™器件的高性能DDR4内存解决方案,每秒数据速率高达2400 Mb。

2014-03-11 10:47:29 1562

1562 本内容主要分析了基于FPGA的系统需求,赛灵思UltraScale FPGA DDR4和其他并行接口分析以及针对高性能高度灵活方案的PHY解决方案介绍。

2016-08-03 19:37:24 190

190 DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200MT/s。DDR4 新增了4 个Bank Group 数据组的设计,各个Bank

2017-11-07 10:48:51 52790

52790

赛灵思有90%的客户在使用DDR存储器。DDR4是倍受青睐的DDR存储器系列的最后一代。众多竞争者们正在虎视眈眈,意图抢占更大的DDR4市场份额。 存储器领域正在发生翻天覆地的变化,这一变化的根本原因在于倍受青睐的DDR存储器系列将在DDR4戛然而止。

2017-11-18 04:19:45 1969

1969 三星电子 30 日宣布,已开始正式量产全球首款 32GB 容量、适用于小型双列直插式存储器模组(SoDIMM)规格的电竞笔电 DDR4 存储器。而新的 SoDIMM 存储器模组是以 10 纳米制程技术打造,可以用户享受丰富的电竞游戏之外,并具有更大的容量与更快的速度,而且佣有更低的耗能表现。

2018-06-11 11:49:00 655

655 大家好,又到了每日学习的时间了,今天咱们来聊一聊SDR、DDR、QDR存储器。 首先先简单的了解一下,然后在做一下比较。 SDR:Single Data Rate, 单倍速率 DDR:Dual

2018-05-30 13:53:06 10650

10650 和Stratix III FPGA的接口。

Stratix III FPGA:

具有强大的DDR3写调平功能,实现和高速DDR3存储器的接口。

提供I/O电路,能够更灵活地支持现有以及新兴的高速外部存储器标准。

保持高速数据速率时的最佳信号完整性

2018-06-22 02:04:00 3477

3477 ,如屏幕上所示。

为了更好地进行演示,我们将使用这里所示的Stratix III DDR3存储器电路板。它上面有几个高速双倍数据速率存储器,例如DDR2 UDIMM插槽、RLD RAM

2018-06-22 05:00:00 8250

8250 本文介绍了DDR4技术的特点,并简单介绍了ANSYS工具用来仿真DDR4的过程。文章中主要介绍的对象为DDR4 3200MHz内存,因为硬件极客对DDR4性能的不断深挖,目前已经有接近5000MHz的量产内存。

2018-10-14 10:37:28 23341

23341 Xilinx推出业界首款面向All Programmable UltraScale™器件的高性能DDR4内存解决方案,每秒数据速率高达2400 Mb.UltraScale器件采用ASIC级架构

2018-11-30 05:33:00 3633

3633 系统架构师必须解决高性能系统应用的一些复杂问题,包括体系结构、算法和功能范围。一般而言,这些应用中一个基本的问题是存储器,作为系统性能的瓶颈和挑战经常位于存储器的体系结构中。由于外部存储器需要更快

2018-12-24 08:00:00 14

14 支持最新一代光纤通道协议(16GFC)的FPGA。背板、交换机、数据中心、云计算应用、测试测量系统以及存储区域网的开发人员采用Altera最新一代28-nm高性能FPGA,能够大幅度提高数据速率,快速进行

2019-05-27 10:33:26 1467

1467 当今电子产品一个很重要的区分元素是其所用的存储器。服务器、计算机、智能手机、游戏机、GPS 以及几乎所有类似产品使用的都是现代处理器和 FPGA。这些设备需要高速、高带宽、双倍数据速率 (DDR) 存储器才能运行。

2019-12-11 13:52:13 4259

4259 韩国存储器大厂SK海力士在2020年的CES上曾经展出过64GB的DDR5-4800存储器,其频宽和容量均比现在的DDR4高出不少,因此备受业界的期待。如今,SK海力士正式宣布,将在年底前量产并提

2020-04-07 14:34:27 758

758 Xilinx 提供了UltraScaleFPGA器件的高性能DDR4内存解决方案,每秒数据速率高达2400 Mb。UltraScale器件采用ASIC级架构,可支持大量I/O和超大存储带宽,并能够

2020-05-28 15:00:57 3996

3996 流媒体视频和星载人工智能。 我之前介绍过面向宇航应用的 Teledyne e2v 的耐辐射 DDR4 (DDR4T04G72),可提供 4GB 的存储容量,高达1.2GHz 的时钟频率和 2.4GT/s 的数据速率(带宽为 172.8Gb/s),本文将更深入地介绍这款宇航级 DDR4 存储器的细节。 本文的

2021-07-26 15:30:30 2464

2464 DDR4的工作原理以及寻址方式DDR4是什么?DDR4全称,DDR4-DRAM,与其他DDRDRAM一样,是当前电子系统架构中使用最为广泛的的RAM存储器。这句话可以分解出3个关键字:存储器

2021-11-06 13:51:01 143

143 电子发烧友网站提供《基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响.pdf》资料免费下载

2023-09-13 09:56:49 0

0 电子发烧友网站提供《TPS65295完整 DDR4 存储器电源解决方案数据表.pdf》资料免费下载

2024-03-06 10:17:54 0

0 电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0

电子发烧友App

电子发烧友App

评论