从操作系统能否满足实时性要求来区分,可把操作系统分成分时操作系统和实时操作系统,分时操作系统按照相等的时间片调度进程轮流运行,分时操作系统由调度程序自动计算进程的

2011-11-14 17:39:30 12251

12251 51单片机使用哈佛结构,它RAM和ROM的总线是同一套总线分时复用的还是两套总线?

2023-05-09 16:03:12

CPLD在DSP系统中的应用设计

2011-08-03 16:15:49

CPLD在汽车制动性能检测系统中的应用汽车制动性是汽车主动安全的主要性能之一,是汽车行驶安全的重要保障。因此,汽车的制动性能的检测研究为其制动性能试验研究和生产检测提供了条件,为提高制动性能提供了

2009-04-16 13:56:57

作为一个新的系统时钟,所有的设计都是基于这个时钟来设计呢在编译时候会出现警告,是一个关于buff的警告并且仿真时正确的,但是下载到硬件发现不是很符合设计要求查阅资料说有的CPLD里面会有PLL模块,可是有的么有。没有的用时钟分频后的信号作为新的时钟触发是不科学的,所以在此询问各位大神。给个经验说法吧

2013-04-25 09:39:35

分时操作系统(Time-sharing Operating System) 分时操作系统将系统处理机时间与内存空间按一定的时间间隔(划分时间片),采用轮转运行方式轮流地切换给各终端用户的程序

2021-12-14 08:28:38

的试验变压器。变频串联谐振试验装置在电力系统应用中的优点1、所需电源容量大大减小。串联谐振电源是利用谐振电抗器和被试品电容谐振产生高电压和大电流的,在整个系统中,电源只需要提供系统中有功消耗的部分,因此

2020-09-05 00:12:40

资料:AG32中cpld的基础

2024-01-03 10:20:43

]/ UHPI_HD[2]/ GP0[2]若系统中,通过EMIFA外挂了一个8位NAND FLASH,且同时支持SD卡,是不是意味着上述这类型管脚需分时复用,即操作SD卡配置为SD用途,操作NAND FALSH时又切换为EMIFA模块功能?

2020-05-25 06:42:18

的速度是480Mbits/s,完全可以满足图像采集、传输以及后续处理的要求。系统中采用 DSP+CPLD的硬件设计方案,采用现场可编程芯片 CPLD及两片 SRAM构成的图像采集和存储系统,可以根据

2019-06-20 07:31:29

是480Mbits/s,完全可以满足图像采集、传输以及后续处理的要求。系统中采用 DSP+CPLD的硬件设计方案,采用现场可编程芯片 CPLD及两片 SRAM构成的图像采集和存储系统,可以根据

2019-07-26 07:16:41

**本文转载自《#2023盲盒+码# OpenHarmony组件复用示例》,作者zhushangyuan_**

● 摘要:在开发应用时,有些场景下的自定义组件具有相同的组件布局结构,仅有状态变量等

2023-08-29 14:40:32

SPI复用时,调试之后读写数据总是不对是为什么?

2022-02-17 07:16:37

STM32外设为什么不需要开启复用时钟(AFIO时钟)呢?STM32外设什么时候需要开启AFIO时钟呢?

2021-11-24 08:05:59

lattice的LC4000的CPLD一个脚可否分时输出3.3、3、0V的电压呀?PCB打样找华强 http://www.hqpcb.com 样板2天出货

2013-03-28 16:00:26

如果输入时钟时差分时钟信号,如何编写testbench?

2014-09-15 19:37:38

文章目录1简介1uCOS-II中的任务1简介uCOS-II实时操作系统实时操作系统与分时操作系统的区别:分时操作系统将时间一块一块的分给不同的任务。实时操作系统提供给用户三样东西:内存管理

2021-12-14 06:42:55

串口通信为何要打开复用时钟???小白不是很理解,求大佬解释

2023-10-23 06:04:02

1、触摸屏中的外部中断初始化里面有个句子(如下红色的语句),明明是PC时钟使能,而且前面已经使能了, 再次赋值不是没有用吗?哪里有使能复用时钟?2、在触摸屏实验中怎么我找不到spi的使能的?直接调用

2019-10-31 22:44:38

什么是CPLD,怎么选择?CPLD在双轴位置检测系统中的应用设计

2021-04-30 06:24:23

特点:①多路性。用户通过各自的终端,可以同时使用一个系统。②及时性。用户提出的各种要求,能在较短或可容忍的时间内得到响应和处理。③独占性。在分时系统中,虽然允许多个用户同时使用一个 CPU,但用户之间

2011-11-02 10:47:56

低漏电多路复用器在高阻抗PLC系统中是否重要?

2020-11-27 06:25:59

关于STM32单片机的复用功能我有点疑问:什么时候用复用输出????什么时候开启复用时钟????谢谢!!!!

2017-08-13 10:22:47

特点:①多路性。用户通过各自的终端,可以同时使用一个系统。②及时性。用户提出的各种要求,能在较短或可容忍的时间内得到响应和处理。③独占性。在分时系统中,虽然允许多个用户同时使用一个 CPU,但用户之间

2011-11-23 08:48:34

请问,我要是只有一个iic,但有两个设备需要用到iic,那iic可以分时复用,会不会有冲突??????

2023-10-26 07:39:35

一.需求采用8脚MCU,需要检测5路输入信号,输出4路控制信号二.设计构思5路输入信号中,1路需要独占I/O口,分配给P3.5。其余4路与输出信号,可以分时使用I/O口,故4路输入与4路输出同时

2015-12-24 21:25:43

基于CPLD的系统中I2C总线的设计

2012-08-17 11:17:28

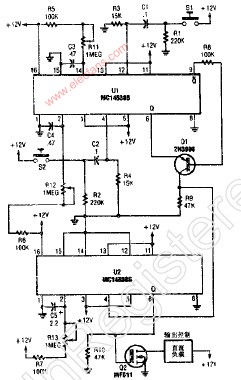

现在大多数的CPLD(复杂可编程逻辑器件)都采用可减少功耗的工作模式,但当系统未使用时,应完全切断电源以保存电池能量,从而实现很多设计者的终极节能目标。图1描述了如何在一片CPLD 上增加几只

2018-09-26 17:29:24

现在大多数的CPLD(复杂可编程逻辑器件)都采用可减少功耗的工作模式,但当系统未使用时,应完全切断电源以保存电池能量,从而实现很多设计者的终极节能目标。

2019-10-08 10:45:26

本文设计的基于CPLD的双CAN控制器已运用于实际应用中,电池管理系统运行可靠,CAN报文收发平稳,完全适合混合动力汽车的使用。

2021-05-06 06:51:07

嗨, 我正在通过App。关于如何连接CRII CPLD中的LED的说明805。该说明提到CPLD可以在LED的情况下吸收电流,即。如果连接的引脚处于逻辑0,那么LED将发光,反之亦然。如果连接的引脚

2019-08-08 06:20:48

本系统以AD7892SQ和CPLD(复杂可编程逻辑器件)为核心设计了一个多路信号采集电路,包括模拟多路复用、集成放大、A/D转换,CPLD控制等。采用硬件描述语言Verilog HDL编程,通过采用CPLD使数据采集的实时性得到提高。

2021-05-08 07:51:14

基于CPLD的三相五电平变频器PWM脉冲发生器的原理是什么基于CPLD的级联型多电平变频器脉冲发生器的设计

2021-05-08 06:18:39

从事便携式或手持产品设计的工程师都明白对于如今的设计,最大限度地降低功耗是必不可少的要求。但是,只有经验丰富的工程师理解尽可能地延长系统的电池寿命的那些微妙但又重要的细节。本文中我们的重点是,如何使用超低功耗的复杂可编程逻辑器件(CPLD)?如何在嵌入式设计中降低CPLD的功耗?

2019-08-01 08:19:42

不出来————小白 如果你存在按键Key和显示Led共用同一个IO时,需要分时复用的需求,则可以移植代码进行使用:代码所占code少于0.5K线程安全,中断安全可移植性高,配置容易注意:系统需要存在一个至少为1ms的时钟中断01 - PCB原理图例程 举2个Key和Led共用IO口的

2021-12-16 07:41:59

FDM系统中,波分复用器用于发射端将多个波长的信号复合在一起并注入传输光纤中,而波分解复用器则用于在接收端将多路复用的光信号按波长分开分别送到不同的接收器上,波分复用/解复用器可以分成两大类,即有源(主动

2016-08-11 15:42:21

电机变频调速系统主要优点电机变频调速系统主要缺点

2021-01-21 06:38:54

原子哥,***和sd卡和w25q16同时在战舰板子上如何使用分时复用而不影响各自的功能,求详细解说,实在不行我只能模拟spi来驱动***了。

2020-07-24 03:08:31

AFIO复用时钟什么时候打开?手册上说,在对寄存器AFIO_EVCR,AFIO_MAPR和AFIO_EXTICRX进行读写操作前,应当首先打开AFIO的时钟。但是我看STM32官方提供的《TM32

2020-07-29 05:21:21

请问DMA总线访问APB外设和SRAM1,CPU操作CCM RAM,这个是同时进行的,还是分时复用的呢?

2024-03-08 07:45:09

什么是复用?请问一下STM32的复用时钟何时开启?

2021-11-24 07:19:24

另外,在DSP系统中为什么要使用CPLD?有大侠指导吗?

2019-07-05 03:42:00

请问,我要是只有一个iic,但有两个设备需要用到iic,那iic可以分时复用,会不会有冲突??????

2019-03-15 06:35:07

如何实现CPLD的在系统编程?

2021-04-25 07:05:12

高速数据采集系统的硬件结构MAX7000系列CPLD及其开发平台介绍CPLD在高速数据采集系统中的应用

2021-04-08 06:11:56

基于CPLD的系统中I2C总线的设计 摘要: 在介绍I2C总线协议的基础上,讨论了基于CPLD的系统中I2C总线的设计技术,并结合工程实例设计了I2C总线IP核,

2008-08-13 13:43:38 31

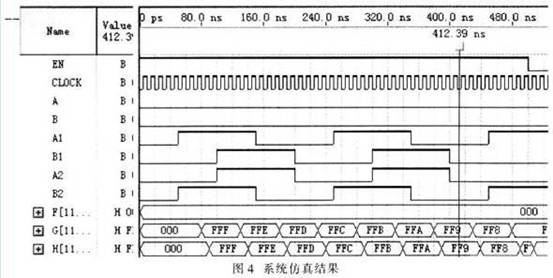

31 介绍了一种基于DSP 和CPLD 的十二相交- 交变频器的全数字化设计。实验表明,由定点DSP 和CPLD 构成的全数字交交变频器,设计、调试方便,控制性能优良,稳定性好,可靠性高。

2009-04-06 14:56:20 26

26 简要介绍利用MaxplusII 软件来实现VVVF 控制SPWM 变频调速的方法。设计中提出一种三相分时运算思路, 详细阐明其具体实现方式。试验证明,CPLD 应用于变频调速系统控制是非常有效的

2009-05-14 13:32:58 23

23 在单片机系统中使用CPLD,可使系统构成灵活,提高可靠性,缩短开发周期。介绍在MCS-51 应用系统中的CPLD 应用设计实例, 详细分析CPLD 的应用和实现方法,提出设计中选用和使用CPLD

2009-05-14 13:49:49 39

39 本文介绍了一种基于CPLD的温度采集系统的设计方法,设计分为温度采集和LED显示两个功能模块。与常用温度采集系统相比,本设计采用高精度数字温度传感器MAX6627与CPLD控制芯片E

2009-07-07 13:44:56 22

22 基于CPLD 和DSP 设计了线阵CCD 检测系统,CCD 的时序驱动由CPLD 实现,经过运放后的视频信号由TMS320F2812 进行采集和处理,此检测系统已成功应用于医药包装行业的数粒机系统,能够可

2009-08-13 14:53:46 22

22 介绍了基于CPLD 和EDA 技术的BIT(机内测试)系统的实现。本系统以CPLD 为控制核心,在MAX+PLUSII 环境下采用VHDL 语言实现了系统接口及测频电路。该系统具有集成度高、灵活性强、易于开

2009-09-03 09:30:51 9

9 复杂可编程逻辑器件(CPLD)结合了专用集成电路和DSP 的优势,既具有很高的处理速度,又具有一定的灵活性。因此,基于CPLD 的数字调制系统的研究具有重要的实际意义。本文论

2009-11-30 16:30:17 20

20 CPLD 器件应用随着生产工艺的逐步提高以及 CPLD 开发系统的不断完善,CPLD 器件容量也由几百门飞速发展到百万门以上,使得一个复杂数字系统完全可以在一个芯片中实现。HDL

2010-01-27 11:40:02 48

48 在单片机系统中使用CPLD,可使系统构成灵活,提高可靠性,缩短开发周期。介绍在MCS-51应用系统中的CPLD应用设计实例,详细分析CPLD的应用和实现方法,提出设计中选用和使用CPLD的

2010-07-14 14:04:25 39

39 介绍了基于CPLD的刷卡式电脑联网集控型自动存包系统的设计,并对系统的软硬件构成、CPLD内部逻辑设计、工作原理等进行了详细说明。该系统速度快、安全性好、可靠性高,而且具

2010-07-16 15:11:12 20

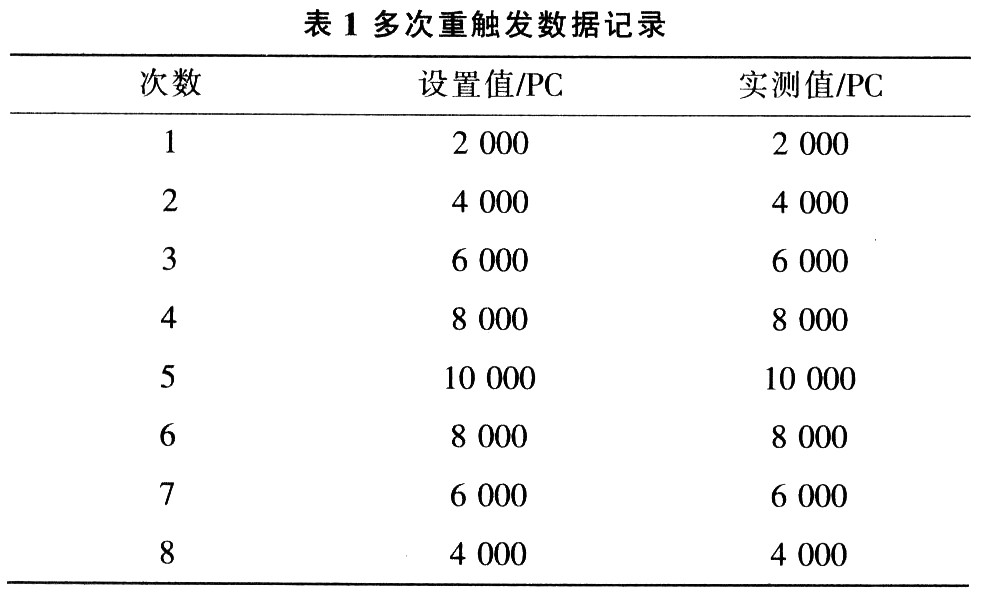

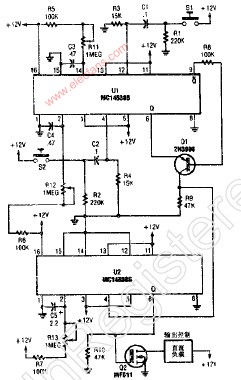

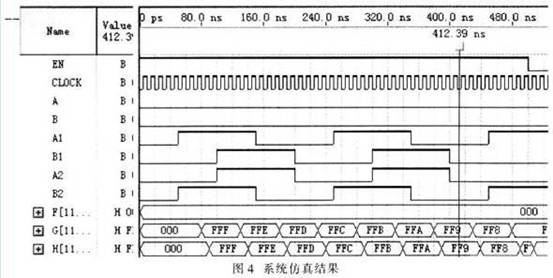

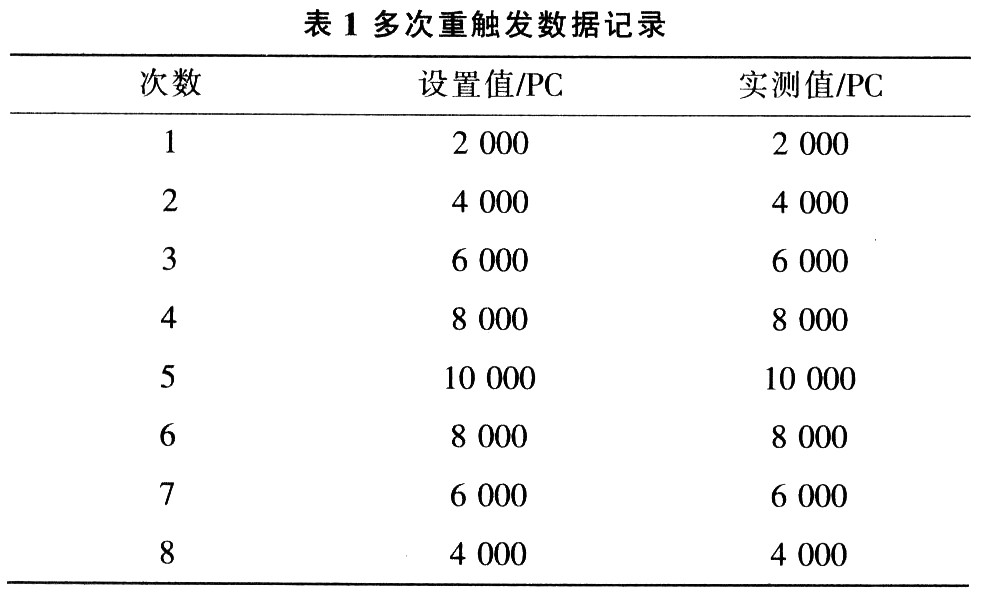

20 提出一种基于CPLD的多次重触发存储测试系统设计方案,详细介绍系统硬件设计以及CPLD内部控制原理,并对CPLD控制电路仿真。该系统体积小、功耗低,能够实时记录多次重触发信号

2010-12-30 16:05:11 22

22 基于CPLD的非多路复用与多路复用总线转换桥的设计与实现

微处理器对外并行总线接口方式一般分为两种,一种为多路复用方式,数据与地址采用共用引脚,分时传输;另一

2009-03-28 15:08:27 753

753

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的简称,一种较PLD为复杂的逻辑元件。CPLD是一种用户根据各自

2009-03-30 13:40:43 3143

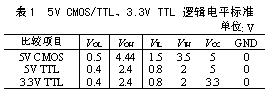

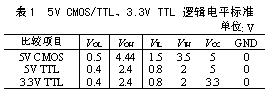

3143 摘要: 较详细地阐述不同逻辑电平的接口原理。以低压CPLD EPM7512A为例,给出在混合电压系统中的具体设计方案。

关键词: 低压CPLD 逻辑电平

2009-06-20 10:53:23 801

801

分时安全电路

当开

2009-10-05 15:02:18 429

429

基于CPLD和嵌入式系统的高速数据采集系统的设计与实现

介绍一种基于CPLD和嵌入式系统的高速数据采集系统,并详细阐述了系统的结构和软硬件的实

2009-10-15 23:46:59 616

616

CPLD在双轴位置检测系统中的应用

1 引言数控机床的加T精度主要南位置检测系统的精度决定,

2009-10-30 08:32:33 431

431

采用CPLD的多次重触发存储测试系统解决方案

概述:提出一种基于CPLD的多次重触发存储测试系统设计方案,详细介绍系统硬件设计以及CPLD内部控制

2010-03-17 11:37:51 531

531

波分复用系统(WDM),波分复用系统(WDM)结构原理和分类

波分复用系统简要介绍

光波分复用技术是在一根光纤中传输多波长光信号的一项

2010-03-19 17:17:09 5357

5357 CPLD,CPLD是什么意思

CPLD是指结构比较复杂的可编程逻辑器件,它包括下述输出宏单元结构:

(1)可编程I/O 允

2010-03-26 17:08:50 3081

3081 今天,大多数的CPLD(复杂可编程逻辑器件)都采用可减少功耗的工作模式,但当系统未使用时,应完全切断电源以保存电池能量,从而实现很多设计者的终极节能目标。图1描述了如

2010-07-16 09:47:26 685

685

本系统以AD7892SQ和CPLD(复杂可编程逻辑器件)为核心设计了一个多路信号采集电路,包括模拟多路复用、集成放大、A/D转换,CPLD控制等。采用硬件描述语言Verilog HDL编程,通过采用CPLD使数

2011-08-23 10:08:38 1447

1447

介绍了采用光纤陀螺器件共享、基于时分复用的三轴一体化光纤陀螺的结构及其工作原理。针对时分复用方案的特点,在满足相关器件工作要求的条件下,重点讨论了三轴陀螺时分复用工

2011-09-13 14:37:44 35

35 CPLD在高速数据采集系统中的应用! 介绍了高速数据采集系统的整体框架分析了其中的通用部分CPLD系列产品的特点及其开发软件.CPLD根据高速数据采集系统的需要VHDL语言的形式,介绍了由

2011-12-17 00:12:00 26

26 利用W INDOW S 消息驱动机制实现对任务的调度, 并给出一种基于分时操作系统原理的单片机多任务控制, 系统应用实例.

2012-04-10 14:30:29 81

81 导波雷达物位计是一种利用时域反射原理实现的高性能物位计。为了实现导波雷达物位计这一高精度时差测量系统,采用了CPLD和MSP430单片机协同工作的电路设计。CPLD为信号收发模块的

2012-11-26 14:49:42 53

53 基于CPLD的多路音频采集系统,有需要的下来看看。

2016-01-21 11:07:07 28

28 基于ARM和CPLD的无线内窥系统设计

2017-01-24 16:15:38 19

19 基于CPLD高速数据采集系统设计_鲜果

2017-03-19 11:45:23 3

3 硬件在回路实时仿真是研究复杂机电系统过程中的一个重要环节,由于仿真通道数量有限,不能满足复杂机电系统大量信号的同步仿真需求。提出一种信号复用/解复用算法,其基本思想是信号复用算法在仿真器的FPGA

2018-02-04 10:12:22 0

0 本文介绍了变频器、高性能变频调速系统、典型调速系统及控制环节以及其应用时的注意事项。它是笔者在该领域多年工作的体会和总结,其特点是以工程师和教授的双重眼光来看待和认识这项技术,既有原理介绍

2018-06-01 11:25:34 7

7 介绍了一种用CPLD(复杂可编程逻辑器件)作为核心控制电路的测试系统接口,通过时cPLD和竹L电路的比较及cPLD在系统中实现的强大功能,论述了CPLD在测试系统接口中应用的可行性和优越性,简单介绍

2019-01-01 16:18:00 1472

1472

现在大多数的CPLD(复杂可编程逻辑器件)都采用可减少功耗的工作模式,但当系统未使用时,应完全切断电源以保存电池能量,从而实现很多设计者的终极节能目标。图1描述了如何在一片CPLD 上增加几只分立

2019-04-18 16:00:42 516

516

变频器与自控系统配合使用时,由于变频器与调节阀的使用是不同的,所以有些问题需要重视和注意。

2019-04-29 16:00:59 1070

1070 晶闸管无换向电动机变频系统分AC-DC-AC(交-直-交)变频及AC-AC(交一交)变频。(1) AC-DC-AC变频系统。该类系统采用电流型变频器,它是由晶闸管构成电源侧变换器(整流器)及直流电

2021-11-08 18:21:01 15

15 什么是引脚的分时复用? 引脚的分时复用是一种技术,它允许在一组引脚上充分利用多种不同的功能,从而降低硬件成本和引脚数量。这种技术在许多电子产品中广泛使用,包括智能手机、计算机、电视机和汽车电子系统

2023-09-15 17:49:56 1208

1208

电子发烧友App

电子发烧友App

评论