|

A New Standard for Multiprocessing DSP Systems Today's applications for computer technology are more demanding than ever before, and no where is this more evident than in the world of digital signal processors (DSPs). DSP chip manufacturers and board vendors are responding to this need with products that possess an inherent ability to support scalable, multiprocessing system architectures. These systems are powerful enough to address the most demanding DSP applications of today and provide a clear upgrade path for the future. The most common DSP applications involve a completely embedded system that is dedicated to performing a particular task in real time. As with all computer applications, speed is of the essence both for processing and data I/O. In addition, constraints on available space and power may further complicate the picture. Requirements such as these present a significant challenge that DSP chip designers and board vendors must face head on. Multiprocessing computing has emerged as the only viable way of addressing a vast assortment of high-end DSP applications. Applications that require multiprocessing computing performance include medical, 3D graphics acceleration, military, industrial control, high end audio, telephony, and wireless communications infrastructure. The metrics that designers of these systems judge DSP performance by are processing per dollar, processing per watt, and processing per area. The real advantage of multiprocessing systems is the ability to tune the performance and cost of a system to yield the required functionality and processing performance. This feature of multiprocessing system architectures is known as scalability. A scalable architecture allows users to tune performance based on the number of processing nodes required. In fact, the ability of a multiprocessing system to scale is not just convenient, it's required; and the ability to design scalable multiprocessing systems starts at the chip level. The new ADSP-21160 SHARC processor, with its large internal memory blocks, multiple internal bus structure, and integrated I/O subsystem, possesses all of the features necessary to build multiprocessing systems that provide true scalability to any number of processors. Like its predecessor (the ADSP-21060 SHARC), the ADSP-21160 is setting the pace for high-performance multiprocessing floating-point DSP systems. |

| Defining Multiprocessing Systems |

|

Processor technology has progressed at such a fast rate over the past decade that most of us cannot even remember how impressed we were with the power of our new 80286 PCs in the late 80's. But while chip manufacturers have awed us with their huge strides in processor technology, they have also exposed the performance limitations inherent in single-processor systems. Thus it is not surprising that high-performance system designers have started using aggregates of processors to build more powerful (multiprocessing) computing systems. |

|

Figure 1. Multiprocessing Systems: |

|

This trend has become very apparent in the embedded DSP industry. As DSP applications become more and more demanding, board-level suppliers are responding with PCI and VME system components that squeeze larger numbers of processors into smaller spaces. Packaging technology has played a role here, as DSP chip-level manufacturers developed smaller package sizes that are relatively easy to cool. However, a system of multiple processors cannot be considered truly multiprocessing based solely on the fact that more than one processor is used. The term multiprocessing implies that the processors in the system are able to work together, in an efficient manner, to perform the required calculations. This means that the exchange of data between processors is critical, and an effective multiprocessing DSP must possess a means for achieving this data transfer. The SHARC processor family has answered this challenge with an internal I/O processor (or DMA engine) that allows data communication to occur without impeding the progress of the processing core. As a result, every time a SHARC processor is added to a multiprocessing network, both processing horsepower and data communication bandwidth are increased. This feature of the SHARC family, together with its unique link-port architecture, is one of the most important ingredients in its ability to support multiprocessing system design. The new ADSP-21160 has increased the number of DMA channels over those available in the first generation ADSP-21060 SHARC from 10 to 14. This allows for a separate independent DMA channel for the transmit and receive buffers of the 2 serial ports, the 6 bi-directional link port buffers, and 4 bi-directional external port buffers. With these enhanced DMA capabilities, the ADSP-21160 has the flexibility to support a variety of scalable multiprocessing system architectures. |

| The Link Port Architecture |

|

Multiprocessing system architectures come in two basic flavors: shared memory and distributed memory. The ADSP-21160 SHARC possesses built-in features that allow it to gluelessly support both of these architectures, as well as architectural hybrids. The key lies in the ADSP-21160's unique link-port architecture. In shared memory systems, every processor has access to a global memory block (made up of internal and external memory) with processors exchanging data via a shared bus. This approach is reminiscent of traditional single-processor programming since all of the data is located in a single memory block. However, the shared memory architecture lacks the inherent ability to scale, since the addition of each new device on the bus decreases the average bus bandwidth available to each processor. The SHARC family of processors gets around this issue through the use of dedicated data communication ports known as link ports. Link ports provide high-bandwidth, point-to-point connections between processors for the sole purpose of inter-processor communication. This allows the ADSP-21160 to support a distributed memory architecture in which all inter-processor communication takes place over the links, leaving the full bandwidth of the data bus for servicing external memory and I/O peripherals. Distributed memory architectures are truly scalable, and they allow users to configure very large scale multiprocessing networks using a natural mesh-like architecture. One of the key strengths of the link-port architecture, however, is that system designers are not forced to choose between shared and distributed memory. Architectural hybrids combining these two philosophies are easy to construct, allowing users to glove-fit their system to their application. The ADSP-21160's ability to support these multiple system architectures is another key aspect of system scaling. System designers are provided the freedom to easily tune their system's form and functionality as well as processing performance. |

| A Balanced Approach |

|

It is well known that the most serious problem facing multiprocessing DSP system and chip-level designers is data flow. In order for a DSP to even approach its peak computational performance, it must be fed with a constant stream of data. This means that a multiprocessing system's ability to route data among the various nodes in the system is equally as important as its ability to process the data. Early multiprocessing system architectures suffered from the malady of having high theoretical MFLOPS numbers but very few usable MFLOPS. This came about as a result of attaching rather inefficient communication engines to very high-performance RISC-style processors that were not designed to be used in multiprocessing systems. The result was a sub-linear scaling characteristic in which system performance increased only slightly as processors were added to the system. The SHARC processing family, on the other hand, places its I/O subsystem and processing core on equal footing, creating a balance between processing and data routing efficiency. This balance allows the DSP application to supply the 21160's high-speed SIMD core with a constant stream of data, resulting in a nearly linear scaling over a wide range of system sizes. Of course taking advantage of this balance in an actual application is a software development function as well. Third party board-level and software vendors supply software development tools for the SHARC family of processors to simplify this effort. Today a variety of native and portable programming tools are available including SHARC-specific run-time environments and industry-standard real-time operating systems. These products not only simplify the task of targeting an application at a multiprocessing network, they also help programmers to take full advantage of the SHARC's balanced hardware design and squeeze the maximum performance out of their embedded SHARC systems. |

| COTS and the Multiprocessing DSP |

|

Multiprocessing digital signal processing systems have become common place in a wide variety of military and commercial applications including RADAR, SONAR, industrial control, image processing and telecommunications. As the need for higher speed and more compact systems arises, multiprocessing DSP systems will become even more widespread. One the fastest growing opportunities for the ADSP-21160 processor is the commercial off the shelf (COTS) board-level vendor market. The use of COTS products has become a mandate (over custom board developments) for both military and commercial users. Fueling this trend is a need for lower product development costs and a faster time to market. The SHARC family, with its unique multiprocessing architecture, lends itself very well to the development of modular system components that can be used together to build high-end multiprocessing systems with essentially any performance and functionality characteristics. This flexibility is the key feature required by COTS customers. Potential application areas for the 21160 appear boundless, with opportunities in many different markets. Regardless of the application, however, it is clear that the multiprocessing movement is here to stay in the embedded DSP marketplace. The ADSP-21160 SHARC from Analog Devices has secured a position to lead this processing revolution into the next millennium, truly setting a new standard for multiprocessing digital signal processing. |

A New Standard for Multiproces

- dsp(364922)

- System(38507)

相关推荐

热点推荐

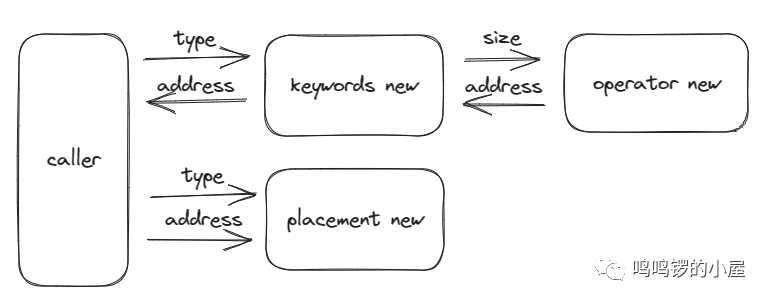

SystemVerilog中的类构造函数new

在systemverilog中,如果一个类没有显式地声明构造函数(new()),那么编译仿真工具会自动提供一个隐式的new()函数。这个new函数会默认地将所有属性变量。

2022-11-16 09:58:24 4246

4246

4246

42464288A技术概述

A new standard in high-speed measurement solutions for ceramic capacitor production tests

2019-09-06 15:01:05

Standard Pad和Standard Plus Pad上支持的S32K344 LPSPI最大总线速率是多少?

Standard Pad 和 Standard Plus Pad 上支持的 S32K344 LPSPI 最大总线速率是多少?

2023-03-29 07:14:30

ATSC Standard:AVC Video Transport Subsystem Characteristics

ATSC Standard:AVC Video Transport Subsystem CharacteristicsIn issuing this standard, the ATSC

2008-10-16 08:36:37

AVS Video Standard

versionof AVS video standard in December 2003 [I],an dexpects to be approved as a national standard in2004.

2008-06-25 09:55:20

Agilent 33220A,Visual C ++简单的正弦波程序?

am new to programming agilent devices thru VC++.Does anyone have the code to Generate a Standard

2019-05-22 08:18:38

DVB资料大全-EIA STANDARD

of theaudio, video and ancillary data processing standard for Advanced Television. The DTV standard

2009-12-18 12:05:50

Direct Mode Coding For Bi-Predictive Pictures in the H.264 Standard

Direct Mode Coding For Bi-Predictive Pictures in the H.264 StandardThe new H.264 (MPEG-4 AVC) video

2008-06-25 09:58:00

H.264 MPEG-4 White Paper

a new generationof internet-based video applications whilst the ITU-T H.263 standard for video

2008-06-25 10:18:21

IEEE 1394 Standard

4IEEE 1394 Standard1394Open Host Controller InterfaceSpecificationRelease 1.1January 6, 2000

2008-06-26 10:09:41

IEEE Standard for Verilog Hardware Description Language 1364-2005

IEEE Standard for Verilog Hardware Description Language 1364-2005IEEE原版 Verilog HDL 2005标准

2013-01-05 18:47:00

Overview of AVS Video Standard

],an dexpects to be approved as a national standard in2004. This version mainly targets at high definitionand

2008-06-04 13:55:04

SCPI命令在E5070A和E5080A之间有所不同

use this: SENS:SWE:TIME 5 Is this new command set going to be the new standard for ENA analyzers

2018-10-08 14:31:39

STM32Cube库和standard peripheral library有什么区别?

STM32Cube库和standard peripheral library有什么区别

2024-05-16 06:52:00

The digital Video Standard according to ITU-R BT. 601/656

The digital Video Standard according to ITU-R BT. 601/656Leveldiagram at the input of an A/D converter for theanalogue component signals Y , CB , CR

2009-06-13 00:00:15

Unified Constant-Frequency Integration Control of Three-Phase Standard Bridge Bo

integrationcontroller for PFC is proposed. For the standard bridge boostrectifier, a unity power factor and low

2011-09-10 23:19:15

【转载消息】Proteus 8.6 - New Features

/whatsnew/#8.6Proteus 8.6 - New FeaturesVersion 8.6 is a significant release in our PCB development

2017-01-22 14:16:01

如何区分3000与3000new

1、2017/1/5默纳克系统常见问题之四如何区分3000与3000new | 默者默纳克系统常见问题之四如何区分3000与3000new默纳克控制系统主要是NICE3000系列, 市面上面主要

2021-09-17 07:03:49

求大神讲解一下Windows Embedded Standard 7

大神开课了,有关Windows Embedded Standard 7你不知道的知识都在这里。

2021-04-27 06:35:41

用TS3A26746E切换standard、OMTP microphone,请问MTK系统是怎样检测MIC的?

您好,我在用TS3A26746E切换standard、OMTP microphone,请问MTK系统是怎样检测MIC的。

2024-11-01 08:23:57

精密组件,半导体和材料测量的新标准

A new standard for precise component, semiconductor and material measurements

2019-11-06 14:21:45

请问C++用new和不用new创建类对象区别是什么?

起初刚学C++时,很不习惯用new,后来看老外的程序,发现几乎都是使用new,想一想区别也不是太大,但是在大一点的项目设计中,有时候不使用new的确会带来很多问题。当然这都是跟new的用法有关

2020-11-05 07:27:40

镃心耗埙新算法 A New Core Loss Model For Iron Powder Material

镃心耗埙新算法 A New Core Loss Model For Iron Powder MaterialThe total core loss of a material can

2009-10-31 08:47:31

h.264 standard pdf

H.264 video compression standard.New possibilities within video surveillance.

Table of contents1.

2008-06-04 14:09:37 22

22

22

22802.11 pdf(IEEE 802.11 Protocol)

technical readers a basic overview of the new 802.11 Standard, in

such a way that they will be able to understand the basic conc

2008-07-12 23:43:25 78

78

78

78ieee 802.16 standard (标准)

802.16TM ConformanceIEEE Standard for Conformance to IEEE 802.16Part 1: Protocol

2008-07-24 00:40:43 4

4

4

4IEEE Std C37.09-1999/Cor 1-200

IEEE Standard Test Procedure for AC High-Voltage Circuit Breakers Rated on a Symmetrical Current

2008-07-24 22:27:15 26

26

26

26Overview of AVS Video Standard

Overview of AVS Video Standard

This paper overviews the AVS video standard interms of basic

2008-08-20 11:48:32 15

15

15

15IEC60730-1 standard

The IEC60730-1 standard describes the requirements of “Automatic ElectricalControls for Household

2008-09-12 10:37:14 103

103

103

103IEEE Std 1076-2002 Standard

1076TM IEEE Standard VHDL Language Reference Manual

IEEE Computer Society Sponsored by the Design

2008-10-21 15:33:38 2

2

2

2IEEE Standard VHDL Language Re

IEEE Standard VHDLLanguage Reference ManualSponsorDesign Automation Standards Committeeof theIEEE

2008-10-21 15:35:02 44

44

44

44IEEE Std 1364-2001 Standard

IEEE Standard Verilog Hardware Description Language SponsorDesign Automation Standards Committee

2008-10-21 15:37:08 24

24

24

24IEEE Standard Verilog Hardware

IEEE Standard Verilog Hardware Description Language

(This introduction is not part of IEEE Std

2008-10-21 15:37:44 0

0

0

0ML7041 pdf datasheet (Audio CO

including CDMA and TDMA applications.The ML7041 sets a new standard for functionality by incorporating all major peripheral handset features, i

2008-10-29 12:30:17 26

26

26

26ATSC-M/H 多功能信号发生器 (ATSC-M/H Mu

Generator, is developed for ATSC-M/H standard which is a new mobile broadcasting standard in U.S.It is the most advan

2009-01-15 11:49:25 14

14

14

14Keysight MSOX6002A双通道混合信号示波器

MSO / MDO示波器, InfiniiVision 6000 X-Series, 2+16 通道, 1 GHz, 20 GSPS, 4 Mpts, 350 ps**New integration

2022-07-30 14:12:39

The new fieldbus standard in A

Fast “Time to Market”Cheaper than own developmentEasy to configureMFP3 technology

2009-04-11 08:53:16 3

3

3

3USB Function IP Core

interconnectbetween computers and peripherals. Everything from a mouse to a camera can beconnected via USB. With the new USB 2.0 specificati

2009-06-14 09:03:23 45

45

45

45D 257-99 (Standard Test Method

Standard Test Methods for DC Resistance or Conductance of Insulating Materials1This standard

2009-08-14 21:35:05 18

18

18

18A New High Gain Low Voltage 1.

A New High Gain Low Voltage 1.45GHz CMOS Mixer:Abstract—A new architecture of CMOS downconversion

2009-09-08 20:41:48 9

9

9

9A New Hybrid Neural System Int

A New Hybrid Neural System Interfacing Neurons and Silicon Hardware for Fast Signal Recognition

2009-09-08 20:42:53 5

5

5

5Research for new method for hi

This paper explores a kind of new method of high-precision non-contactmeasurement of rotate speed

2009-09-09 15:45:39 6

6

6

6Enabling New Infotainment-Equi

Enabling New Infotainment-Equipment Cost Structures With Open-System Architectures:The infotainment

2009-10-06 14:42:27 9

9

9

9A New Three-Phase Power-Factor

A New Three-Phase Power-Factor Correction (PFC) Scheme Using Two Single-Phase PFC Modules:Abstract

2010-03-01 17:42:23 36

36

36

36EPON Ushers In a New Generatio

EPON Ushers In a New Generation of Bandwidth-Intensive Applications白皮书

Based on fiber-optics, EPON

2010-03-24 16:12:59 9

9

9

9What’s New in PADS 9.0

PADS 9.0 introduces exciting new functionality to the PADS flow, including PADSLayout, PADS Router

2010-03-27 08:27:07 0

0

0

0The New Personal International

The New Personal International Language Esata:1. Introduction to Esata2. Esata Alphabet

2010-04-11 08:53:56 44

44

44

44Windows Embedded Standard 7与Wi

Windows Embedded Standard 7与Windows Embedded Standard 2009在组件化、工具和映像创建等方面的对比

本文介绍了Windows Embedded Standard 2009和Windows Embedded Standard 7在组件化、工具

2010-04-15 14:00:00 18

18

18

18VoIP Howto

VoIP Howto

Voice Over IP is a new communication means that let you telephone with Internet

2010-04-23 18:05:00 12

12

12

12A New Generation of Hall Senso

80% of all current measurements within motor control are done with a shunt resistor.

2010-06-01 17:43:03 29

29

29

29New Measurement Requirements f

digitalinformation at higher speeds. This need has put new requirements on transformer manufacturers andpresented new challenges to test equ

2010-06-10 08:19:20 10

10

10

10NEW POLYMERS FOR IMPROVED FLOC

flocculants• Introduce New Family of Flocculants– Description of flocculant chemistry– Laboratory development re

2010-07-01 18:36:45 10

10

10

10A New Approach to Generate Thi

IntroductionOrganothiols on noble metals such as gold have been developed as a model system

2010-08-05 09:18:34 8

8

8

8New Enhanced Agilent Nano Suit

Features and Benefits• New test method development offers easier, more user-friendly protocol

2010-08-13 09:43:00 6

6

6

6MAX1709 4A, Low-Noise, High-Fr

sets a new standard of space savings for high-power, step-up DC-DC conversion. It delivers up to 20W at a fixe

2009-02-08 19:12:27 1450

1450

1450

1450

Windows Embedded Standard简介及在中

1.Windows Embedded Standard简介

看到Windows Embedded Standard,或许有些人会感到疑惑,但如果说起微软的XP Embedded (XPE),相信大多数人就明白了。作为Windows三

2009-03-12 14:53:54 1617

1617

1617

1617A New Approach for Compensatin

Abstract: The MAX1460 is a digital-sensor signal processor (DSSP) implemented in fine-geometry

2009-04-20 16:33:42 1045

1045

1045

1045

MAX4951 New re-drivers support

New re-drivers support PCIe Gen II and SATA/eSATA Gen III data rates

2009-05-29 10:57:07 1116

1116

1116

1116Brand New XP-8000-CE6 Release:

Brand New XP-8000-CE6 Release: More Powerful, More Attractive

2010-01-06 11:37:21 1080

1080

1080

1080MAX15054 New high-side FET dri

MAX15054 New high-side FET driver simplifies the design of buck and buck-boost HB LED drivers

2010-01-28 08:39:02 1730

1730

1730

1730什么是ASCII (American Standard Co

什么是ASCII (American Standard Code for Information Interchange)

英文缩写: ASCII (American Standard Code for Information Interchange)

中文译名:

2010-02-22 09:57:01 860

860

860

860LEDs allow new remote-controll

LEDs allow new remote-controlled lighting applications

One benefit LEDs offer in general lighting

2010-05-14 08:42:09 1339

1339

1339

1339

DS92LV010A Bus LVDS Transceiver Ushers in a New Era of High-Performance Backplane Design

Bus LVDS (BLVDS) is a new family of bus interface circuits invented by National Semiconductor based

2011-05-22 11:45:21 19

19

19

19简单的电池电路扩展以太网供电(PoE)峰值电流

Power over Ethernet (PoE) is a new development thatallows for the delivery of power

2012-02-03 15:53:41 75

75

75

75Cadence Allegro and OrCAD (Including ADW): What’s New in Release 17.0

This document describes the new features and enhancements in Cadence® Allegro® and OrCAD® (Including ADW) products in Release 17.0.

2015-11-30 15:54:20 0

0

0

0TMS320_DSP_Algorithm_Standard_Demonstration_Application

TMS320 DSP Algorithm Standard Demonstration Application。

2016-01-19 14:16:49 6

6

6

6Designing with a New Super Fast

Designing with a New Super Fast Dual Norton Amplifier

2017-03-24 15:48:30 0

0

0

0Topics on Using the LM6181-A New

Topics on Using the LM6181-A New Current Feedback Amplifier

2017-03-23 17:34:50 0

0

0

0TI_Video-ImagingGuide

designed television set or a standard receiver with a set-top box. DTVs rapid growth in popularity

2017-05-21 11:22:54 9

9

9

934980A测试平台技术的研究

solution — typically integrated by a local system integrator — or a standard, off-the-shelf application

2017-09-12 08:50:49 2

2

2

2简单的无线照明控制系统应用

By implementing a lighting control solution using the ZigBee Light Link (ZLL) standard

2017-09-13 15:30:34 14

14

14

14612 2.5SSD demo board (Standard version)

612 2.5SSD demo board (Standard version)

2017-11-23 10:14:35 4

4

4

4placement new详解

placement new是重载operator new的一个标准、全局的版本,它不能被自定义的版本代替(不像普通的operator new和operator delete能够被替换成用户自定义的版本)。

2018-03-02 14:24:56 0

0

0

0PADS Standard Plus工具的功能介绍

PADS Standard Plus提供了灵活的兼容性,强大的系统设计和规则设置功能,是高效和易用的PCB工具。

2019-05-15 06:57:00 5277

5277

5277

5277PADS Standard和PADS Standard Plus的功能概括

探讨 PADS Standard 和 PADS Standard Plus 所包含的功能。PADS Standard 可满足专注于原理图和 PCB 设计的工程师的需求。PADS Standard Plus 则主要提供给要求分析和验证优势的硬件工程师使用。

2019-05-15 06:03:00 10425

10425

10425

10425

New IP提出的背景是什么?什么是New IP?

尽管国外媒体已经发现New IP类似6G,是正常的面向未来十年的IP技术演进研究,但国内外还是有不少不明真相(甚至揣着明白装糊涂)的媒体,将英国金融时报该文翻译后多地发布,误导了不少人。

2020-05-18 15:41:53 3661

3661

3661

3661Windows Media Audio (WMA9) Standard Decoder for Blackfin

Windows Media Audio (WMA9) Standard Decoder for Blackfin

2021-02-01 10:50:13 5

5

5

5new[] 和 delete[]能不配对使用吗

在平时资料中,我们常看到: new和delete,new[]和delete[]一定要配对使用! 也 有人说: 有时候不配对使用也不会出现问题。 也许你也是只知其然,不知其所以然,然而我也有点懵了

2021-11-17 10:24:00 1699

1699

1699

1699UVM中类的例化用new还是create

UVM中类的例化用new和create有什么不同?什么时候可以用new?什么时候该用create?

new是OOP自带属性,create是UVM override属性,可以理解成create比new更进阶~

2023-03-21 11:26:46 2064

2064

2064

2064C++内存管理operator new和placement new

最近在看一些C++资料的过程中,说到在初始化列表中使用关键字new来分配新内存不是异常安全的,应该使用运算符new。

2023-07-22 09:58:35 1431

1431

1431

1431

new和malloc的区别

1. 申请的内存所在位置 new操作符从自由存储区(free store)上为对象动态分配内存空间,而malloc函数从堆上动态分配内存。自由存储区是C++基于new操作符的一个抽象概念,凡是通过

2023-11-11 11:29:10 1144

1144

1144

1144

电子发烧友App

电子发烧友App

评论