Quartus II与ModelSim、Synplify Pro等常用EDA工具的开发流程。ALTERA CPLD FPGA设计高级篇:结合作者多年工作经验,深入地讨论了altera fpga

2020-05-14 14:50:30

Altera FPGA/CPLD设计与Verilog数字系统设计教程从网上找到了一些Altera FPGA/CPLD经典教材,包含夏宇闻老师的Verilog数字系统设计教程(第2版)Altera FPGA/CPLD设计与Verilog数字系统设计教程

2014-02-17 09:22:18

Altera FPGA/CPLD设计(高级篇)》

2012-12-06 15:51:36

《Altera FPGA_CPLD设计 基础篇》是Altera官方指定培训中文教材,说的较为详细,值得一看。

2013-02-25 17:42:17

Altera FPGA_CPLD设计 高级篇

2023-08-05 18:38:20

可编程逻辑器件相关专辑 Altera-FPGA/CPLD设计,从基础篇到高级篇由浅入深帮助大家学习

2018-10-08 15:43:55

`` 本帖最后由 yuxuandl 于 2013-5-3 22:10 编辑

Altera FPGA CPLD设计_基础篇&高级篇两本书,讲解比较精细,适合初学和进阶人士学习参考。ttach]``

2013-05-03 22:05:30

、MAX7000 系列、Mercury、FELX10KE、APEX20KE、APEX20KC、ACEX1K、APEX II和 Stratix 等。 其开发工具 MAX+PLUS II 是较成功

2019-03-04 14:10:13

Max+plusⅡ是Altera公司提供的FPGA/CPLD开发集成环境,Altera是世界上最大可编程逻辑器件的供应商之一。Max+plusⅡ界面友好,使用便捷,被誉为业界最易用易学的EDA软件

2009-10-09 17:14:29

我最近在用MAX II系列下的芯片EPM240T100C5N,由于是新手就选择了MAX+Plus ii 这个软件,请问大家一下,这个软件支持选择MAX II系列的芯片吗?或者如何升级器件选择列表

2013-11-19 21:33:04

想用它来***好用途。问候,沚以上来自于谷歌翻译以下为原文I'm unable to generate an license key for the MAX+PLUS II Baseline

2018-10-24 15:17:11

MAX PLUS II软件的学习1 初步了解大规模可编程器件(FPGA)设计的全

2009-10-24 19:17:08

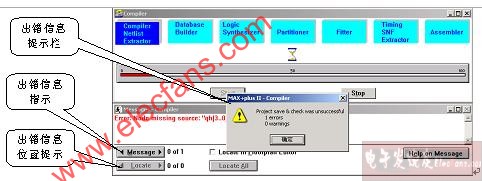

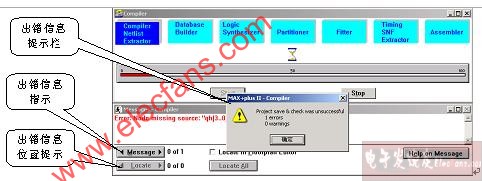

;5、自动错误定位在编译源文件的过程中,若源文件有错误,Max+Plus2软件可以自动指出错误类型和错误所在的位置。6、逻辑综合与适配该软件在编译过程中,通过逻辑综合 (Logic

2009-10-09 17:21:44

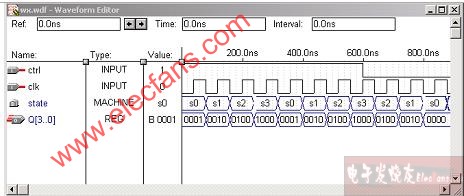

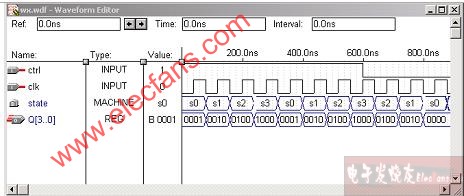

;Max+plusⅡ/Text Editor;Max+plusⅡ/Waveform Editor)3)指定CPLD型号(Assign/Device)4)设置管脚、下载方式和逻辑综合的方式(Assign

2009-10-09 17:28:51

max+plus问题:max+plus是不是不支持vhdl的否则,为设么每次把vhdl转换成图形文件时总会提示library ieee; 哪行错误

2012-08-18 14:19:23

、Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。将以查表法结构方式构成逻辑行为的器件称为FPGA,如Xilinx的SPARTAN系列、Altera的FLEX10K

2019-07-01 07:36:55

EPF10K200S, FLEX 6000, MAX® II, MAX 3000A, MAX 7000B, MAX 7000S, MAX 7000AE MAX+PLUS® II 查看和体验 是 是 RTL查看器和工艺

2012-08-15 12:30:03

USB -CPLD开发板使用攻略一、开发板简介 简介:板载大容量 ALTERA MAXII 系列CPLD 芯片EPM1270,和 USB2.0 高速 CY7C68013A芯片,构成完美的逻辑和数

2012-08-15 14:44:47

`现在我有一个atmel的cpld芯片,用了个如下图所示的下载线一直不能发现设备,如图.不知道哪位大哥告诉一下该怎么玩,另买一个altera的byteblaster吗我只有一个积分。。`

2015-12-18 21:07:50

和相应的开发软件为目标载体进行阐述,本教程阐述了ALTERA主要系列芯片PLD芯片的结构和特点以及相应的开发软件MAX和Plusa和Quartus的使用。” 希望对各位有用。

2014-05-11 20:44:00

各位大侠,小弟CPLD/FPGA新手,遇到烧录不保存问题,详细描述如下:芯片型号:Altera MAX V 5M160ZE64Quartus版本:Quartus II 14.1问题描述:1

2015-07-21 10:40:23

学会CPLD的系统设计技术。本书以ALTERA公司的系列芯片为目标载体,简要分析了可编程逻辑器件的结构和特点,以及相应开发软件的使用方法,同时,还用大量篇幅介绍了初学者最容易掌握的Verilog

2018-03-30 15:07:50

用Altera_Cpld作了一个186(主CPU)控制sdram的控制接口, 发现问题:要使得sdram读写正确, 必须把186(主CPU)的clk送给sdram, 而不能把clk经cpld的延时

2019-09-18 05:02:19

本公司供应ALTERA、XILINX(FPGA、CPLD)芯片,有需求可联系深圳市恒兆赢科技有限公司/销售部:杨绿风phone: 0755-83266848Fax: 0755-83998200QQ

2011-03-02 14:11:22

MAX+ plus Ⅱ简介 MAX + plus Ⅱ是一种与结构无关的全集成化设计环境,使设计者能对Altera 的各种CPLD 系列方便地进行设计输入、快速处理和器件编程

2008-06-24 13:48:14

MAX + plus Ⅱ是一种与结构无关的全集成化设计环境,使设计者能对Altera 的各种CPLD 系列方便地进行设计输入、快速处理和器件编程。MAX+ plus Ⅱ开发系统具有强大的处理

2008-06-16 08:47:47

的专用集成电路(ASIC)的设计。2 Max+PlusⅡ开发工具Max+PlusⅡ开发工具是美国Altera公司自行设计的一种CAE软件工具。它具有全面的逻辑设计能力,设计者可以自由组合文本、图形和波形输入法

2008-10-15 09:00:22

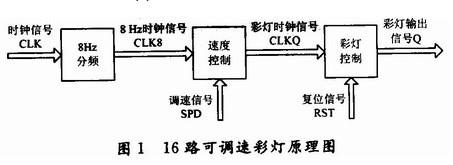

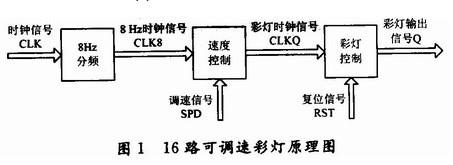

本文介绍应用美国ALTERA公司的MAX+PLUSⅡ平台,使用VHDL硬件描述语言实现的十六路彩灯控制系统。

2021-04-19 07:43:57

如何利用CPLD去实现接口电路?怎样去设计MAX+PLUSⅡ程序?

2021-04-28 06:45:34

,其中包含VHDL语言、CPLD介绍、AHDL语言和Max+plusⅡ软件四部分,教材中有大量的有关VHDL、AHDL语言使用的例题,特别是一步一步学习软件、使用VHDL、AHDL语言的例题可以帮助

2009-10-22 15:44:59

现在altera的CPLD芯片用的最多是哪几款啊

2013-10-16 18:51:55

推荐一款CPLD芯片大概二三十个引脚四十到六十个逻辑宏单元,最好可以在max plus 2下仿真。

2012-11-23 10:15:51

我现在想用gps的秒脉冲做同步钟,控制A/D数据同步采集,用哪个系列的cpld功耗最低?以前用过XILINX的95144和ALTERA MAXII系列的epm570,听说现在都出MAXV了,是不是5M570Z功耗更低?

2019-09-03 14:26:17

` 本帖最后由 sheniquhong 于 2017-7-6 15:41 编辑

开发板正面图Altera Strati***板上竟然还有MAX系列的CPLD芯片NIOS II 6.0的flash rom背面图2006年官方开发板`

2017-07-06 15:41:46

谁有max+plus的软件的急急!!!!!!谢谢

2012-03-09 23:09:19

我们是AGM的长期授权代理商,可以为用户提供最具竞争力的价格与技术支持服务。

PIN to PIN Altera-CPLD:

AG576SL144--->

2021-11-23 10:12:42

Max+Plus II简易用户使用入门指南

nMAX+PLUS II 为实现不同的逻辑功能提供了许多符号,如:图元符

2008-09-11 15:09:05 7

7 Powerful of CLIQUE

What is CLIQUE ?Clique is an option which provided by Altera Max+Plus

2008-09-12 09:56:34 0

0 Third Party EDA Tools Interface with Altera Max+Plus II

What Altera SupportAltera

2008-09-12 09:57:11 0

0 《Altera FPGA/CPLD设计(高级篇)》结合作者多年工作经验,深入地讨论了Altera FPGA/CPLD的设计、优化技巧。在讨论FPGA/CPLD设计指导原则的基础上,介绍了Altera器件的高级应用;引领读者

2009-02-12 09:19:12 4807

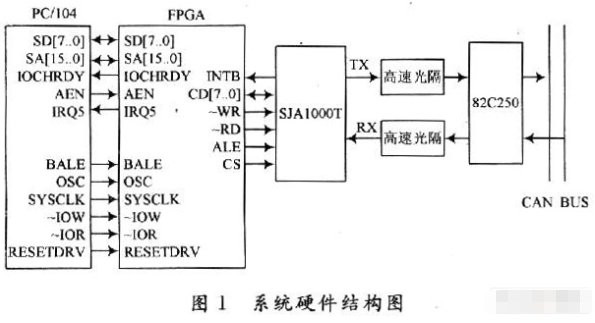

4807 用ALTERA 公司MAX7000 系列CPLD 芯片实现单片机与PC104 ISA 总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL 设计部分。

2009-04-14 17:36:07 29

29 用ALTERA 公司MAX7000 系列CPLD 芯片实现单片机与PC104 ISA 总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL 设计部分。

2009-05-14 13:24:39 16

16 altera fpga/cpld设计 基础篇结合作者多年工作经验,系统地介绍了FPGA/CPLD的基本设计方法。在介绍FPGA/CPLD概念的基础上,介绍了Altera主流FPGA/CPLD的结构与特点,并通过丰富的实例讲解

2009-07-10 17:35:45 58

58 FPGA/VHDL技术是近年来计算机与电子技术领域的又一场革命。本书以AAltera公司的FPGA/CPLD为主详细介绍了FPGA、CPLD为主详细介绍了FPGA的相关知识,MAX+PLUSⅡ开发环境和VHDL语言基础,并

2009-07-11 15:06:42 58

58 本文以MAX+PLUSⅡ软件为开发平台,利用CPLD器件设计了一种新型彩灯控制器。该控制器具有控制路数多、功能可扩展、图案可控制等特点。近年来,出现了一系列生命力强、应用广

2009-08-17 10:50:41 33

33 红绿灯的控制计算变化时间程序源代码:

-- MAX+plus II VHDL Example-- Conditional Signal Assignment-- Copyright

2010-02-08 17:14:30 43

43 EPM1270F256C4N,ALTERA/阿尔特拉,介绍MAX®II系列即时开启非易失性CPLD基于0.18-μ,6层金属闪存工艺,密度从240到2210个逻辑元件(LE)(128至22

2023-10-24 15:38:16

探讨电梯控制技术的发展历史和技术现状,仔细研究CPLD器件的工作原理,开发流程以及VHDL语言的编程方法;采用单片CPLD器件,在MAX+plusⅡ软件环境下,运用VHDL语言设计一个16楼层单

2010-12-27 15:27:35 56

56 摘 要:本文介绍了一个采用PLD,利用MAX+PLUSⅡ和 EWB等开发工具,完成了功率因数精确测量的设计。其核心芯片是Altera公司ACEX 1K系列的EP1K10TC144-3。引言在电力

2006-03-11 12:55:52 4251

4251

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2006-03-13 19:36:44 1072

1072

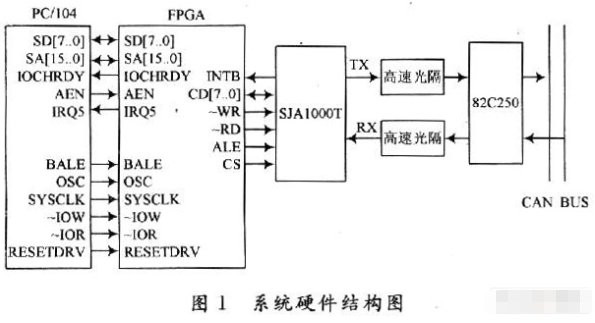

摘要:用ALTERA公司MAX7000系列CPLD芯片实现单片机与PC104 ISA总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL设计部分。CPLD(Complex Programmable Logi

2006-05-26 21:52:11 1159

1159

Altera公司、ZAPiT Games公司及其研究开发合作伙伴Nytric今天宣布选用Altera的MAX® II CPLD来生产其第一款定位于家庭游戏的低价格交互式娱乐产品——Game Wave游戏控制台

2006-06-01 23:23:36 812

812 Altera MAX+plus II 介绍

一、软件功能简介MAX+plusⅡ(Multiple Array and Programming Logic User System)开发工具是美国Altera 公司推出的一种EDA

2008-09-24 10:15:36 8234

8234

实验一、MAX+PLUSⅡ的基本应用一 实验目的1掌握MAX+PLUSⅡ的安装及基本使用。2掌握MAX+PLUSⅡ基本输入法—图形输入工具按钮的使用。二 实验设备

2009-03-13 19:15:01 4653

4653

MAX+PLUSⅡ的基本应用-波形输入练习一 实验目的1掌握MAX+PLUSⅡ的基本使用。2掌握MAX+PLUSⅡ基本输入法—波形输入法的使用。二 实验设备与仪器

2009-03-13 19:16:05 2750

2750

实验三 MAX+PLUSⅡ的设计处理

一 实验目的1掌握MAX+PLUSⅡ的基本使用。2掌握MAX+PLUSⅡ的设计处理过程中的编译和仿真。3 掌

2009-03-13 19:19:02 1358

1358

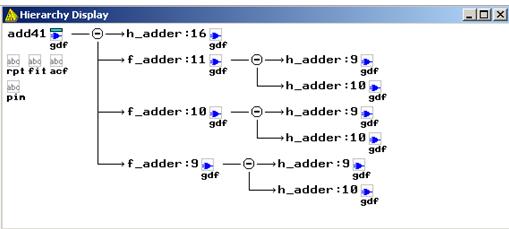

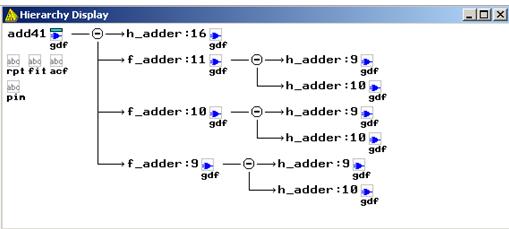

实验四、MAX+PLUSⅡ的层次设计一 实验目的1进一步掌握MAX+PLUSⅡ的基本使用,包括设计的输入、编译和仿真。2掌握MAX+PLUSⅡ的层次化设计方法。二

2009-03-13 19:20:48 2046

2046

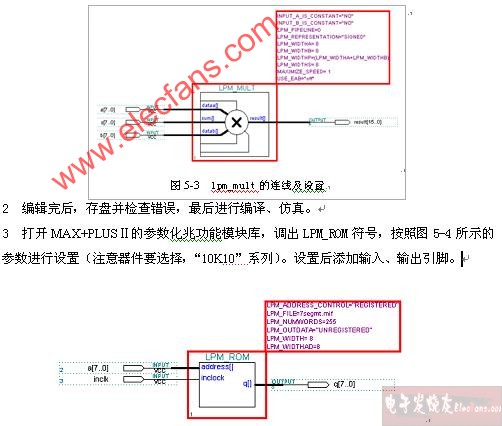

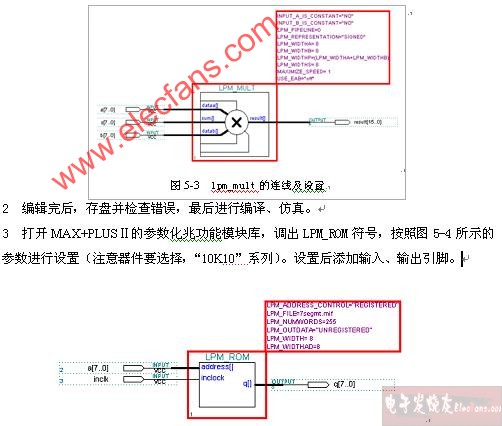

实验五、MAX+PLUSⅡ的参数化兆功能模块库的使用一 实验目的1进一步掌握MAX+PLUSⅡ参数化兆功能模块库的使用。2了解参数化兆功能模块库LP

2009-03-13 19:23:18 2059

2059

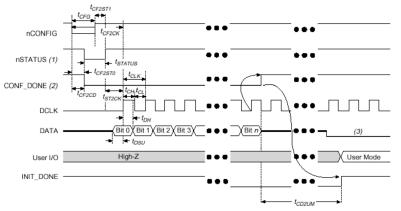

用单片机配置CPLD器件

ALTERA公司的可编程序逻辑器件APEX20K、FLEX10K和FLEX6000虽应用广泛,但由于其内部采用SRAM存储配置数据,每次系统上电时,必须用配置芯片对其进行配置

2009-03-28 16:18:06 1423

1423

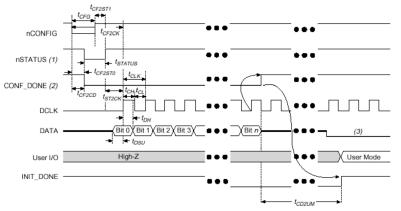

一、 配置方式

ALTERA CPLD器件的配置方式主要分为两大类:主动配置方式和被动方式。主动配置方式由CPLD器件引导配置操作过程,它控制着外部存储器和

2009-06-20 10:58:14 2674

2674 摘 要: 介绍了一种利用工具软件MATLAB强大的数学功能来增强ALTERA公司的可编程逻辑器件设计软件MAX+PLUSII的仿真功能、提高设计品质的方法,有较强的针对性。

2009-06-20 11:45:15 1080

1080

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2009-06-20 12:45:00 884

884

摘要:用ALTERA公司MAX7000系列CPLD芯片实现单片机与PC104 ISA总线接口之间的并行通信,给出系统设计方法及程序源代码。包括通信软件和AHDL设计部分。

关键词:CPLD

2009-06-20 13:34:28 1360

1360

摘 要:介绍了一种利用ALTERA公司的复杂可编程逻辑器件(CPLD)快速卷积法实现数字滤波器的设计 关键词:CPLD 数字滤波器 信号处理

2009-06-20 14:23:56 1317

1317

摘 要:本文介绍了一种利用可编程器件CPLD实现CAN总线与微机之间接口的设计,说明了设计思想和设计方案,并给出了使用MAX+PLUS Ⅱ软件图形输入法的逻辑设计和

2009-06-20 14:56:08 996

996

Altera增强MAX II系列,进一步拓展其CPLD应用

Altera公司宣布,提供工业级温度范围以及功耗更低的MAX IIZ器件,从而进一步增强了MAX II CPLD系列。MAX IIZ CPLD完美的结合了逻辑

2009-11-05 09:53:58 1668

1668 MAX+PLUSⅡ符号库提供了很多基本图元(Primitive, 又称原语)供图形设计文件调用, 这些图元大体上可分为缓冲器、 寄存器、 输入输出端口、 逻辑门图元等几类。其中寄存器和组合

2010-06-07 10:26:59 4372

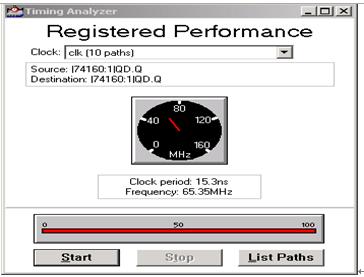

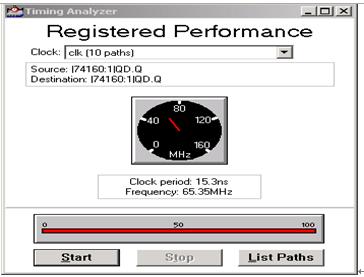

4372 1 引言 Altera的 MAX+PLUSⅡ可编程逻辑开发软件,提供了一种与工作平台、器件结构无关的设计环境,深受广大电子设计人员的喜爱。但设计人员都会遇到Altera器件设计中的时间匹配

2010-07-05 10:31:05 1424

1424

O 引言

MAX+PLUSⅡ开发系统是易学易用的完全集成化的设计开发环境。目前已发行10.0版本。该软

2010-12-23 11:33:45 3751

3751

本文利用Max+ Plus 软件对PCM30/ 32 路系统的发送端时序与帧结构进行了仿真,由仿真结果可以清楚地发现该系统发端时序的规律

2011-03-28 10:55:27 3239

3239

本文介绍了Altera器件和MAX+PLUS II的开发流程,然后将变电所进行抽象,得到了设计对象。将系统定义为命令输入、外部条件输入、开关控制逻辑电路、开关控制时序电路等几个模块

2011-04-15 15:47:13 41

41 本文选用CPLD 是ALTERA 公司的EPM240T100,结合MAX232 接口芯片进行串口通信设计

2011-04-25 11:44:28 13034

13034

什么是.scf?答:SCF文件是MAXPLUSII的仿真文件, 可以在MP2中新建. 用Altera_Cpld作了一个186(主CPU)控制sdram的控制接口, 发现问题:要使得sdram读写正确, 必须把186(主CPU)的clk送给sdram, 而不能

2011-05-25 17:35:22 36

36 Altera提供全面的定制逻辑器件系列产品FPGA、ASIC和CPLD。 学会以下术语有助于你加速实现Altera器件的开发。 自适应逻辑模块(ALM) 协议实现配置(CvP) 嵌入式HardCopy模块......

2012-06-04 14:02:43 20

20 本资料是关于Altera FPGA的选型及开发,内容大纲是:Altera的 FPGA体系结构简介;Altera的 FPGA选型策略;嵌入式逻辑分析工具SignalTAPII的使用;基于CPLD的FPGA配制方法。

2012-08-15 14:48:34 104

104 MAX+PLUS II软件下载入口

2012-09-14 14:27:47 447

447 altera FPGA/CPLD高级篇(VHDL源代码)

2012-11-13 14:40:38 135

135 Altera FPGA_CPLD设计(实例源代码)

2013-09-09 16:09:23 446

446 整个设计采用MAX+ plus II开发平台,VHDL编程实现,基于可编程逻辑器件CPLD设计多波形信号发生器。用VHDL编程实现,其设计过程简单,极易修改,可移植性强。系统以CPLD为核心,采用直接数字合成技术,辅以必要的模拟电路,构成一个波形稳定,精度较高的函数信号发生器。

2016-10-12 16:51:10 15

15 Third Party EDA Tools Interface with Altera Max+Plus II

2022-08-01 11:11:45 5

5 Max+plusⅡ是Altera公司提供的FPGA/CPLD开发集成环境,Altera是世界上最大可编程逻辑器件的供应商之一。Max+plusⅡ界面友好,使用便捷,被誉为业界最易用易学的EDA软件

2022-07-13 10:09:01 0

0 帮助读者学会设计数字系统的硬件描述语言VHDL、并熟悉Altera公司产品和软件Max+PlusⅡ。

2022-07-10 14:34:02 0

0 EDA技术以可编程逻辑器件FPGA和CPLD及其开发系统为硬件平台,以EDA开发软件如Max+PlusⅡ为开发工具,基于逻辑功能模块的层次化设计方法设计数字系统。Max+PlusⅡ设计可采用原理图

2017-09-07 15:37:45 8

8 Max+plusⅡ功能简介 1 、原理图输入(Graphic Editor) MAX+PLUSII软件具有图形输入能力,用户可以方便的使用图形编辑器输入电路图,图中的元器件可以调用元件库中元器件,除

2017-12-05 10:27:33 5

5 VHDL语言 在第一章我们详细介绍了VHDL语言,世界各大半导体公司开发的设计软件都支持该语言,MAX+PLUS II软件也支持该语言,下面介绍VHDL语言是如何在MAX+PLUS II软件中使

2017-12-05 10:37:54 11

11 Max+PlusⅡ是Altera公司提供的FPGA/CPLD开发集成环境,它可独立完成简单VHDL程序的编译。然而,自动电梯控制程序是一个复杂的状态机描述,Max+PlusⅡ无法独立完成该程序的综合编译。

2018-05-27 11:38:00 5161

5161

QuartusⅡ是Altera公司在21世纪初推出的FPGA/CPLD集成开发环境,是Altera公司前一代FPGA/CPLD集成开发环境Max+PlusⅡ的更新换代产品,其界面友好,使用便捷,功能强大,为设计者提供了一种与结构无关的设计环境,使设计者能方便的进行设计输入、快速处理和器件编程。

2019-05-03 07:35:00 7984

7984

用VHDL语言设计交通灯控制系统,并在MAX+PLUS II系统对FPGA/CPLD芯片进行下载,由于生成的是集成化的数字电路,没有传统设计中的接线问题,所以故障率低、可靠性高,而且体积小。体现了EDA技术在数字电路设计中的优越性。

2018-11-05 17:36:05 23

23 本文档的主要内容详细介绍的是FPGA教程之ALTERA的CPLD与FPGA器件的详细资料说明主要内容包括了:一、Altera器件一般介绍,二、MAX 7000 系列器件,三、FLEX10K系列器件,四、边界扫描测试

2019-02-27 17:27:31 17

17 QuartusⅡ是Altera公司在21世纪初推出的FP-GA/CPLD开发环境,是Altera前一代FPGA/CPLD集成开发环境MAx+PlusⅡ的更新换代产品,其功能强大,界面友好,使用便捷

2021-06-08 15:43:08 4678

4678

Altera FPGA CPLD学习笔记(肇庆理士电源技术有限)-Altera FPGA CPLD学习笔记

2021-09-18 10:54:41 85

85 CPLD的MAX系列器件库max-13.0.1.232

2022-12-21 17:26:11 9

9

电子发烧友App

电子发烧友App

评论