摘 要: 本论文提出一种基于TMS320C6701 DSP实现HDTV信源解码器的方案。用C6701实现系统控制、解复用、AC-3音频解码,用STi7000视频解码。与现有的HDTV信源解码方案相比,本方案将核心芯片由三片(系统控制+解复用、视频解码和音频解码)减少到两片,有利于系统集成,代表了HDTV信源解码器的发展方向之一。

引言

数字高清晰度电视(HDTV)是继黑白电视和彩色电视之后的新一代电视,HDTV接收机或机顶盒具有广阔市场和巨大经济效益,已经成为国际高科技领域研究开发的热点之一。

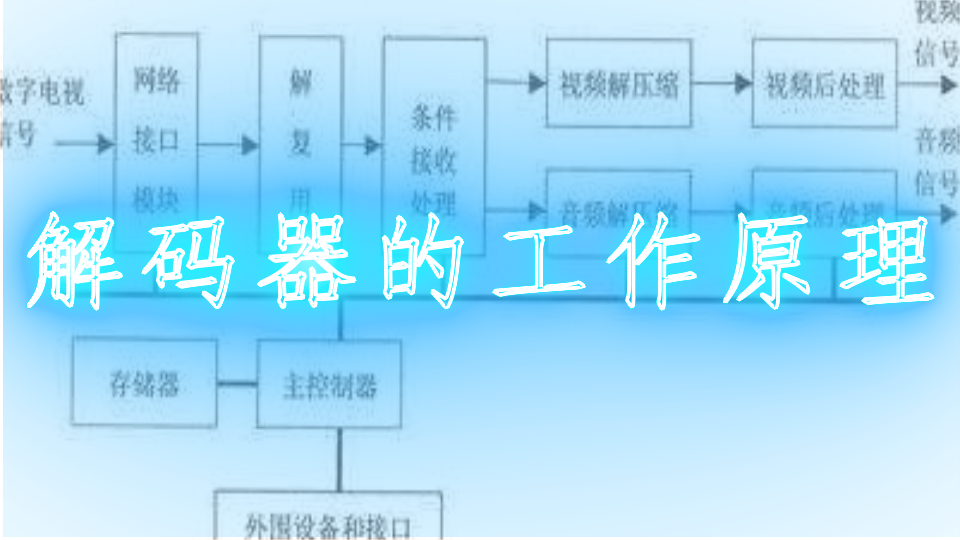

HDTV接收系统由信道解码、信源解码、显示终端组成。目前,多数HDTV信源解码方案均由三片或三片以上的核心芯片组成,分别用于系统控制+解复用、视频解码、音频解码。为了提高系统的集成度,信源解码方案正向着两片方案过渡,最终可能实现单片解码方案。本文提出一种两片解码方案:用TI的TMS320C6701完成系统控制、解复用、音频解码;用STi7000完成视频解码。

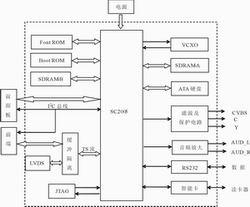

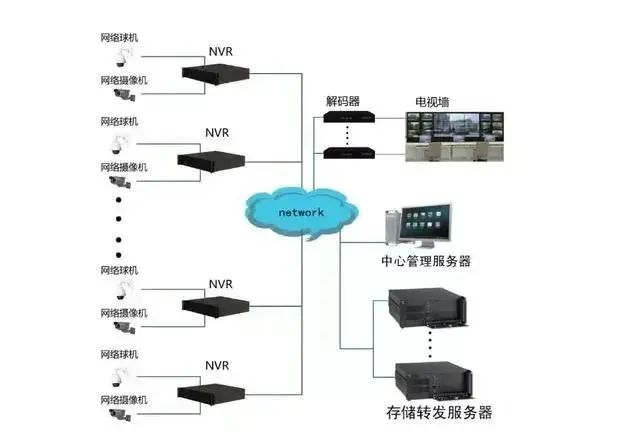

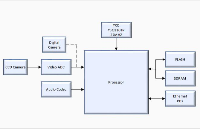

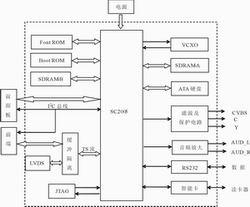

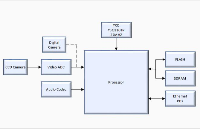

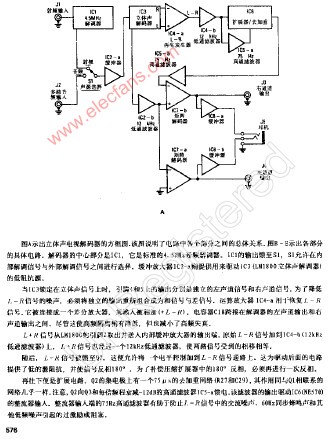

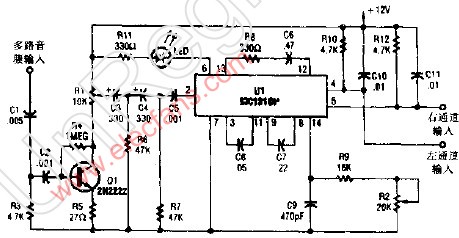

图1 信源解码器硬件框图

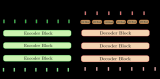

图2 信源解码器软件结构框图

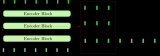

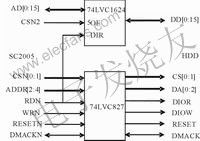

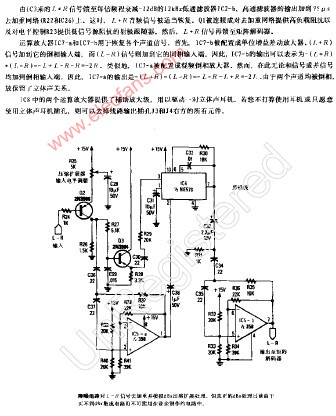

图3 软件解码数据流图

硬件设计

本信源解码方案的硬件设计如图1所示。

系统的核心为TMS320C6701 DSP,采用EPROM固化系统程序。C6701配接SDRAM用来存储数据和工作程序。FIFO1用来输入TS。视频解码器STi7000映射到C6701存储空间。STi7000配有SDRAM用来存储视频PES、各种图像(解码、参考和显示帧图像)及OSD数据。视频后处理部分由THS8134 DAC、CPLD及运放组成。系统本地时钟和PWM产生器由FPGA实现,它与VCXO、RC低通滤波器一起在C6701解复用软件配合下完成27MHz时钟恢复。音频解码由C6701软件完成。音频输出部分由FIFO2、一个 74LS157和三个D/A芯片组成。音频输出所用时钟和控制信号也由FPGA实现。

系统控制、解复用和音频解码

C6701是TI的高性能浮点DSP,时钟为167MHz,具有1336MIPS能力。C6701的Memory Map选为Map0。在其存储器的 CE0 空间中放置了1M*32位的SDRAM。在CE1空间放置了1M*16位EPROM。本系统使用ROM boot process,因此C6701的BOOTMODE[4:0] 引脚置为“10010”。C6701的程序超过64K字节,因此从0地址开始执行的是一个Loader,它把EPROM中其他程序继续传送到SDRAM中。传送完成后,CPU开始从Loader以下的地址开始执行程序。CE2空间用来放置异步器件,此时它的大小为4Mbytes。它被GAL内部的译码器等分为四个部分。前两个部分放置STi7000;第三部分放置FIFO1;第四部分放置实现本地时钟和PWM的FPGA。CE3空间仅放置FIFO2。

C6701 PLL模式被选为 *4 , 即输入引脚CLKMODE[1:0] = 11b。41.75MHz由5V晶体振荡器产生,经过LVT125做电平变换后输入给C6701。C6701的SDCLK输出加给零延迟时钟缓冲器CY2308后分两路分别提供给SDRAM。C6701所用的3.3V(VCC3)和1.9V(VCC1.9)由PT6921产生。本系统有一个 14脚插座, 它可与XDS510 emulator(硬件仿真器)连接起来实现仿真。C6701的HPI和串口1不被使用,相应引脚与跳线连接,以便系统功能扩展时使用。

本系统输入为并行TS,输入接口由TS数据(TSData[7:0]),DVALID,BCLK and ERROR组成。当TS数据输入达到2KB时,FIFO的/HF信号有效,它作为一个中断信号加给C6701 INT6脚。接到此中断后,C6701运行有关中断子程序,DMA将2KB TS数据取出传输到C6701片内的SRAM中。该FIFO映射到C6701 EMIF CE2空间。

27MHz系统时钟恢复由FPGA(EPF10K20)中的计数器/PWM模块、外部低通滤波器和VCXO在C6701相应软件的控制下完成。VCXO输出的时钟信号输入给FPGA中的一个42位计数器产生本地时钟LMCR。当C6701按一定算法求得PCR与本地时钟的差值后,将此差值输出给FPGA的PWM模块,该模块将此差值转换为PWM信号后输出给低通滤波器,取出直流后控制VCXO输出频率。经一定时间的调整后,得到与发射方同步的27MHz。VCXO输出的27MHz时钟也提供给视频解码器使用。

视频解码

视频解码由ST公司的STi7000在C6701的相应软件控制下实现。STi7000完成如下功能:a)接收C6701传来的视频PES并进行句法分析,取出ES存入SDRAM,取出DTS、PTS存入相应寄存器。b)找到ES中各层的开始码并提取头部信息,存入相应寄存器中,发中断给C6701。C6701读取这些头部信息,并据此控制解码流水线工作。c)STi7000的核心是硬件SLICE层以下解码流水线。它从SDRAM中读出ES,进行解压缩(VLD-反扫描-IDCT-运动补偿)得到重构图像,并根据其类型(I、B或P帧)存入SDRAM相应区内。在流水线开始每一帧图像解码前,C6701要根据该帧类型等参数向STi7000发解码命令。解码流水线另一个重要功能是实现隐错。d)视频格式转换:图像输出前,可进行各种格式变换(水平分辨率上下变换;垂直行数上下变换;隔行(I)和逐行(P)相互变换;3:2电影下拉模式和幅型比(4:3或16:9)变换(FULL、ZOOM、LETTERBOX和SIDEBAR)。e)实现OSD功能。

STi7000约有110个寄存器,分为配置、控制、存储器存取、解码指令、显示、OSD、时钟/锁相环、D1接口、PES等9类。 C6701对STi7000各寄存器的存取通过STi7000的8位微控制器接口进行。该接口映射入C6701 EMIF CE2空间最低1MB内。其8位数据线接到LVT16245一边;8位地址线接LVT16244输出边;片选(notA_cs)接GAL相应的输出,读写(A_RnotW)接LVT16244输出/B_AWE上。中断请求信号(notA_IRQ)接C6701 INT4脚。C6701通过STi7000的8位并行数据接口向STi7000写入视频压缩数据。该接口与上述8位微处理器接口共用8位数据线。压缩数据请求信号接C6701 INT5脚。压缩数据选通输入notA_STRB则由GAL提供。

STi7000需要128Mbit的SDRAM存储器,由两片4*512K*32-Bit的100MHz SDRAM芯片组成。STi7000要求SDRAM具有如下特点:全页Burst长度;连续Wrap;3周期CAS Latency。SDRAM和STi7000实现“glueless(无胶合)”连接。

本系统采用TI的THS8134实现视频输出D/A变换。本系统只实现HD输出方式。STi7000的24Bit Y、Cb、Cr数字视频信号和PIXCLK直接输出给THS8134,产生模拟Y、Pb、Pr分量信号。STi7000的PIXCLK、HSYNC和VSYNC信号加给一个CPLD(EPM7128)。该CPLD控制THS8134按照相应的标准(1080I格式对应SMPTE274M;720P格式对应SMPTE296M;480P格式对应SMPTE293M;480I格式对应SMPTE170M)分别在Y、Pb、Pr分量上叠加三电平(1080I和720P)或两电平(480P)复合同步信号,然后经运算放大器放大后输出。这四种格式由C6701 TOUT0和TOUT1输出的Displaymode0和1选择。

当音频开始输出时,C6701先将4KB数据写入FIFO2中。FIFO2映射入C6701 EMIF CE3空间。FIFO2的满标志/FF信号有效,它触发FPGA内相应模块开始工作,将音频主时钟12.2880MHz时钟分频产生LRCLK(左右时钟信号,频率48KHz)和SCLK(串行时钟,频率为3.072MHz)。SCLK信号作为FIFO2的读信号,而LRCLK则作为74LS157的输入选择信号。当LRCLK为高电平时,左(左环、中央声道)数据输出给三个DAC芯片;当LRCLK为低电平时,右(右环、LFE)数据输出给三个DAC芯片。MCLK、LRCLK和SCLK同时输入给三个DAC芯片。由三个DAC输出的5.1声道经放大后分别输出。当FIFO2中已输出2KB数据时,其/HF无效,此信号接至C6701 INT7输入脚,触发该中断。C6701执行相应的中断子程序,再向FIFO2输出2KB数据,如此循环,保证音频信号持续输出。

软件设计

系统的软件结构如图2所示。

在C6701内部有64Kbytes的数据SRAM和64Kbytes的Cache/Program SRAM。程序SRAM经初始化用作Cache。64K字节的片内数据RAM被组织成两个块。它们的地址分别为8000 0000h到8000 7FFFh和8000 8000h到8000 FFFFh。当CPU的Side A和Side B或者DMA控制器同时使用不同块时,不会引起冲突。因此,同时访问的数据位于不同块时,不需考虑它们的地址。整个片内数据RAM分为五个部分:TS_Buffer(4K字节)用来缓冲输入的TS;V_PES_Buffer(16K字节)用来存放视频PES; A_PES_Buffer(8K字节) 用来存放音频PES/ES; A_Buffer(32K字节) 用来存放解压缩后的音频数据;剩余的部分用于缓存中间计。

算数据。每一部分Buffer又分成两个块,以乒乓方式使用。即一块由CPU使用时,另一块可以同时进行存贮或由DMA使用。

软件整个系统解码数据流图如图3所示。首先FIFO1接收到的TS数据到其存储量的一半(2KB),发出中断(INTa)激活DMA3。DMA3把FIFO1里一半的数据倒到C6701的片内存储器TS_Buffer中,并在传输完成时发出中断(INTb),INTb的中断服务程序发出信号semPES激活解复用任务。解复用任务从片内存储器中取出TS数据进行相应处理,然后把分离出的音视频PES数据送回片内存储器,当A_PES_Buffer填充一半时,通过信号量semAudio激活音频处理任务。音频处理任务从A_PES_Buffer中取出音频PES数据,解码后存到A_Buffer。当A_Buffer中的数据积累到一定数量时,激活DMA2。DMA2把解码后的4KB音频数据输出给FIFO2,FIFO2的/FF信号(满标志)启动音

频数据由FIFO2的读出。音频输出FIFO2半空时会发出中断INTc,激活DMA2。DMA2把A_Buffer中的数据再传送2KB到FIFO2去,如此继续下去。视频PES数据由DMA0从V_PES_Buffer不断地倒到片外SDRAM中,当接到STi7000请求时,激活DMA1,把SDRAM中缓存的的视频PES数据输出给STi7000,进行解码,然后,经视频后处理后输出给显示器。

解复用的功能包括:PSI分析,时钟恢复以及对传输包拆包并传给相应的buffer(缓存器)。

视频解码的功能是对视频PES进行解压缩,恢复出视频流。在系统中,Video Driver的中断的优先级被设为最高。视频解码系统主要是通过中断来触发其它过程的进行,中断是视频解码主线,操纵着整个视频解码的过程。

音频解码的功能是对音频PES进行AC-3解压缩,恢复出音频流。音频解码从音频PES包解码开始,在6701片内的数据存储区中开辟A_PES_Buffer(由两块各4KB对称的存储区组成),解复用得到的音频PES数据以乒乓方式存储到这两个区域。经过拆包PES数据得到的ES数据直接覆盖PES数据所处区域。然后开始音频解码的核心计算,将解码输出的PCM数据格式化后存储到片内数据存储区中开辟的两块(各16K)PCM缓冲区中,利用DMA2将其中的数据输出给片外的FIFO。

结语

本论文提出了一种基于通用DSP C6701的HDTV信源解码器两片解决方案。随着技术的进步,将来可能会提出HDTV信源解码器单片解决方案。即在单个功能强大的芯片的基础上,很多工作可以由软件控制实现。本论文提出的HDTV信源解码器解决方案对于下一代HDTV信源解码器的研制具有重要的参考价值。

引言

数字高清晰度电视(HDTV)是继黑白电视和彩色电视之后的新一代电视,HDTV接收机或机顶盒具有广阔市场和巨大经济效益,已经成为国际高科技领域研究开发的热点之一。

HDTV接收系统由信道解码、信源解码、显示终端组成。目前,多数HDTV信源解码方案均由三片或三片以上的核心芯片组成,分别用于系统控制+解复用、视频解码、音频解码。为了提高系统的集成度,信源解码方案正向着两片方案过渡,最终可能实现单片解码方案。本文提出一种两片解码方案:用TI的TMS320C6701完成系统控制、解复用、音频解码;用STi7000完成视频解码。

图1 信源解码器硬件框图

图2 信源解码器软件结构框图

图3 软件解码数据流图

硬件设计

本信源解码方案的硬件设计如图1所示。

系统的核心为TMS320C6701 DSP,采用EPROM固化系统程序。C6701配接SDRAM用来存储数据和工作程序。FIFO1用来输入TS。视频解码器STi7000映射到C6701存储空间。STi7000配有SDRAM用来存储视频PES、各种图像(解码、参考和显示帧图像)及OSD数据。视频后处理部分由THS8134 DAC、CPLD及运放组成。系统本地时钟和PWM产生器由FPGA实现,它与VCXO、RC低通滤波器一起在C6701解复用软件配合下完成27MHz时钟恢复。音频解码由C6701软件完成。音频输出部分由FIFO2、一个 74LS157和三个D/A芯片组成。音频输出所用时钟和控制信号也由FPGA实现。

系统控制、解复用和音频解码

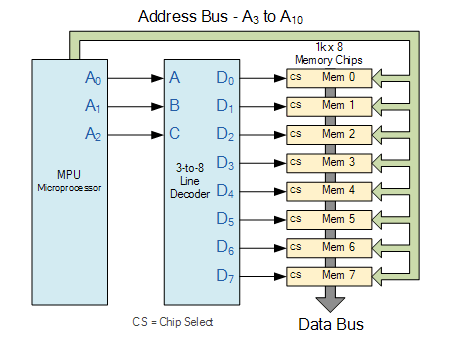

C6701是TI的高性能浮点DSP,时钟为167MHz,具有1336MIPS能力。C6701的Memory Map选为Map0。在其存储器的 CE0 空间中放置了1M*32位的SDRAM。在CE1空间放置了1M*16位EPROM。本系统使用ROM boot process,因此C6701的BOOTMODE[4:0] 引脚置为“10010”。C6701的程序超过64K字节,因此从0地址开始执行的是一个Loader,它把EPROM中其他程序继续传送到SDRAM中。传送完成后,CPU开始从Loader以下的地址开始执行程序。CE2空间用来放置异步器件,此时它的大小为4Mbytes。它被GAL内部的译码器等分为四个部分。前两个部分放置STi7000;第三部分放置FIFO1;第四部分放置实现本地时钟和PWM的FPGA。CE3空间仅放置FIFO2。

C6701 PLL模式被选为 *4 , 即输入引脚CLKMODE[1:0] = 11b。41.75MHz由5V晶体振荡器产生,经过LVT125做电平变换后输入给C6701。C6701的SDCLK输出加给零延迟时钟缓冲器CY2308后分两路分别提供给SDRAM。C6701所用的3.3V(VCC3)和1.9V(VCC1.9)由PT6921产生。本系统有一个 14脚插座, 它可与XDS510 emulator(硬件仿真器)连接起来实现仿真。C6701的HPI和串口1不被使用,相应引脚与跳线连接,以便系统功能扩展时使用。

本系统输入为并行TS,输入接口由TS数据(TSData[7:0]),DVALID,BCLK and ERROR组成。当TS数据输入达到2KB时,FIFO的/HF信号有效,它作为一个中断信号加给C6701 INT6脚。接到此中断后,C6701运行有关中断子程序,DMA将2KB TS数据取出传输到C6701片内的SRAM中。该FIFO映射到C6701 EMIF CE2空间。

27MHz系统时钟恢复由FPGA(EPF10K20)中的计数器/PWM模块、外部低通滤波器和VCXO在C6701相应软件的控制下完成。VCXO输出的时钟信号输入给FPGA中的一个42位计数器产生本地时钟LMCR。当C6701按一定算法求得PCR与本地时钟的差值后,将此差值输出给FPGA的PWM模块,该模块将此差值转换为PWM信号后输出给低通滤波器,取出直流后控制VCXO输出频率。经一定时间的调整后,得到与发射方同步的27MHz。VCXO输出的27MHz时钟也提供给视频解码器使用。

视频解码

视频解码由ST公司的STi7000在C6701的相应软件控制下实现。STi7000完成如下功能:a)接收C6701传来的视频PES并进行句法分析,取出ES存入SDRAM,取出DTS、PTS存入相应寄存器。b)找到ES中各层的开始码并提取头部信息,存入相应寄存器中,发中断给C6701。C6701读取这些头部信息,并据此控制解码流水线工作。c)STi7000的核心是硬件SLICE层以下解码流水线。它从SDRAM中读出ES,进行解压缩(VLD-反扫描-IDCT-运动补偿)得到重构图像,并根据其类型(I、B或P帧)存入SDRAM相应区内。在流水线开始每一帧图像解码前,C6701要根据该帧类型等参数向STi7000发解码命令。解码流水线另一个重要功能是实现隐错。d)视频格式转换:图像输出前,可进行各种格式变换(水平分辨率上下变换;垂直行数上下变换;隔行(I)和逐行(P)相互变换;3:2电影下拉模式和幅型比(4:3或16:9)变换(FULL、ZOOM、LETTERBOX和SIDEBAR)。e)实现OSD功能。

STi7000约有110个寄存器,分为配置、控制、存储器存取、解码指令、显示、OSD、时钟/锁相环、D1接口、PES等9类。 C6701对STi7000各寄存器的存取通过STi7000的8位微控制器接口进行。该接口映射入C6701 EMIF CE2空间最低1MB内。其8位数据线接到LVT16245一边;8位地址线接LVT16244输出边;片选(notA_cs)接GAL相应的输出,读写(A_RnotW)接LVT16244输出/B_AWE上。中断请求信号(notA_IRQ)接C6701 INT4脚。C6701通过STi7000的8位并行数据接口向STi7000写入视频压缩数据。该接口与上述8位微处理器接口共用8位数据线。压缩数据请求信号接C6701 INT5脚。压缩数据选通输入notA_STRB则由GAL提供。

STi7000需要128Mbit的SDRAM存储器,由两片4*512K*32-Bit的100MHz SDRAM芯片组成。STi7000要求SDRAM具有如下特点:全页Burst长度;连续Wrap;3周期CAS Latency。SDRAM和STi7000实现“glueless(无胶合)”连接。

本系统采用TI的THS8134实现视频输出D/A变换。本系统只实现HD输出方式。STi7000的24Bit Y、Cb、Cr数字视频信号和PIXCLK直接输出给THS8134,产生模拟Y、Pb、Pr分量信号。STi7000的PIXCLK、HSYNC和VSYNC信号加给一个CPLD(EPM7128)。该CPLD控制THS8134按照相应的标准(1080I格式对应SMPTE274M;720P格式对应SMPTE296M;480P格式对应SMPTE293M;480I格式对应SMPTE170M)分别在Y、Pb、Pr分量上叠加三电平(1080I和720P)或两电平(480P)复合同步信号,然后经运算放大器放大后输出。这四种格式由C6701 TOUT0和TOUT1输出的Displaymode0和1选择。

当音频开始输出时,C6701先将4KB数据写入FIFO2中。FIFO2映射入C6701 EMIF CE3空间。FIFO2的满标志/FF信号有效,它触发FPGA内相应模块开始工作,将音频主时钟12.2880MHz时钟分频产生LRCLK(左右时钟信号,频率48KHz)和SCLK(串行时钟,频率为3.072MHz)。SCLK信号作为FIFO2的读信号,而LRCLK则作为74LS157的输入选择信号。当LRCLK为高电平时,左(左环、中央声道)数据输出给三个DAC芯片;当LRCLK为低电平时,右(右环、LFE)数据输出给三个DAC芯片。MCLK、LRCLK和SCLK同时输入给三个DAC芯片。由三个DAC输出的5.1声道经放大后分别输出。当FIFO2中已输出2KB数据时,其/HF无效,此信号接至C6701 INT7输入脚,触发该中断。C6701执行相应的中断子程序,再向FIFO2输出2KB数据,如此循环,保证音频信号持续输出。

软件设计

系统的软件结构如图2所示。

在C6701内部有64Kbytes的数据SRAM和64Kbytes的Cache/Program SRAM。程序SRAM经初始化用作Cache。64K字节的片内数据RAM被组织成两个块。它们的地址分别为8000 0000h到8000 7FFFh和8000 8000h到8000 FFFFh。当CPU的Side A和Side B或者DMA控制器同时使用不同块时,不会引起冲突。因此,同时访问的数据位于不同块时,不需考虑它们的地址。整个片内数据RAM分为五个部分:TS_Buffer(4K字节)用来缓冲输入的TS;V_PES_Buffer(16K字节)用来存放视频PES; A_PES_Buffer(8K字节) 用来存放音频PES/ES; A_Buffer(32K字节) 用来存放解压缩后的音频数据;剩余的部分用于缓存中间计。

算数据。每一部分Buffer又分成两个块,以乒乓方式使用。即一块由CPU使用时,另一块可以同时进行存贮或由DMA使用。

软件整个系统解码数据流图如图3所示。首先FIFO1接收到的TS数据到其存储量的一半(2KB),发出中断(INTa)激活DMA3。DMA3把FIFO1里一半的数据倒到C6701的片内存储器TS_Buffer中,并在传输完成时发出中断(INTb),INTb的中断服务程序发出信号semPES激活解复用任务。解复用任务从片内存储器中取出TS数据进行相应处理,然后把分离出的音视频PES数据送回片内存储器,当A_PES_Buffer填充一半时,通过信号量semAudio激活音频处理任务。音频处理任务从A_PES_Buffer中取出音频PES数据,解码后存到A_Buffer。当A_Buffer中的数据积累到一定数量时,激活DMA2。DMA2把解码后的4KB音频数据输出给FIFO2,FIFO2的/FF信号(满标志)启动音

频数据由FIFO2的读出。音频输出FIFO2半空时会发出中断INTc,激活DMA2。DMA2把A_Buffer中的数据再传送2KB到FIFO2去,如此继续下去。视频PES数据由DMA0从V_PES_Buffer不断地倒到片外SDRAM中,当接到STi7000请求时,激活DMA1,把SDRAM中缓存的的视频PES数据输出给STi7000,进行解码,然后,经视频后处理后输出给显示器。

解复用的功能包括:PSI分析,时钟恢复以及对传输包拆包并传给相应的buffer(缓存器)。

视频解码的功能是对视频PES进行解压缩,恢复出视频流。在系统中,Video Driver的中断的优先级被设为最高。视频解码系统主要是通过中断来触发其它过程的进行,中断是视频解码主线,操纵着整个视频解码的过程。

音频解码的功能是对音频PES进行AC-3解压缩,恢复出音频流。音频解码从音频PES包解码开始,在6701片内的数据存储区中开辟A_PES_Buffer(由两块各4KB对称的存储区组成),解复用得到的音频PES数据以乒乓方式存储到这两个区域。经过拆包PES数据得到的ES数据直接覆盖PES数据所处区域。然后开始音频解码的核心计算,将解码输出的PCM数据格式化后存储到片内数据存储区中开辟的两块(各16K)PCM缓冲区中,利用DMA2将其中的数据输出给片外的FIFO。

结语

本论文提出了一种基于通用DSP C6701的HDTV信源解码器两片解决方案。随着技术的进步,将来可能会提出HDTV信源解码器单片解决方案。即在单个功能强大的芯片的基础上,很多工作可以由软件控制实现。本论文提出的HDTV信源解码器解决方案对于下一代HDTV信源解码器的研制具有重要的参考价值。

- HDTV(52996)

- 源解码器(5352)

相关推荐

热点推荐

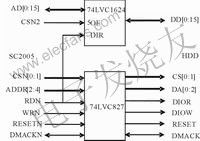

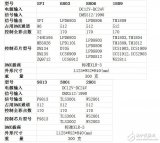

采用SC2005做主芯片的机顶盒信源解码器的设计与实现

机顶盒大体可以分成两个功能部分:信道解调解码部分和信源解码部分。信道部分即前端,负责对数字电视信号进行解调接收和信道解码。由于前端的不同,机顶盒可分为数字卫星机顶盒、数字地面机顶盒和数字有线机顶盒三种。

2018-11-23 08:13:00 8664

8664

8664

8664

HDTV的一体机与分体机的区别

HDTV的一体机与分体机的区别 HDTV数字高清电视机,可以划分为一体机和分体机。一体机就是电视显示器内置机顶盒(信源解码、信道解码、条件接收)完整功能,一体机直接标识为HDTV

2009-05-24 18:18:39

解码器常见故障及解决方法

一、为什么解码器码转灯不闪? 现象:软件设置(灯不闪,主要是码转换器未进行工作,先从软件设置着手解决这个问题) 解决方案:1、软件中的解码器设置(解码器协议、com口、波特率、校验位、数据位

2020-12-11 14:12:09

AMBA解码器产品手册

解码器执行三个功能:

·它为每个总线从机生成从机选择信号(DSELx),表示需要传输到该从机。

·当未选择从机时,它在仅地址传输期间产生从机响应信号(BWAIT、BLAST和BERROR)。

·它可

2023-08-22 06:26:05

EVAL-ADV7401EBZ评估板使用ADV7401 10位,多格式SDTV / HDTV视频解码器

EVAL-ADV7401EBZ,评估板,使用ADV7401 10位,集成,多格式SDTV / HDTV视频解码器和RGB图形数字转换器

2020-06-08 14:29:06

EVAL-ADV7401EB评估板,使用ADV7401多格式SDTV / HDTV视频解码器和RGB图形数字转换器

EVAL-ADV7401EB,评估板,使用ADV7401 10位,集成,多格式SDTV / HDTV视频解码器和RGB图形数字转换器

2020-06-15 16:18:50

EVAL-ADV7403EBZ评估板使用ADV7403 10位,多格式SDTV / HDTV视频解码器

EVAL-ADV7403EBZ,评估板,使用ADV7403 10位,集成,多格式SDTV / HDTV视频解码器和RGB图形数字转换器

2020-06-08 15:59:32

EVAL-ADV7403EB使用ADV7403 10位,集成,多格式SDTV / HDTV视频解码器和RGB图形数字转换器

EVAL-ADV7403EB,评估板,使用ADV7403 10位,集成,多格式SDTV / HDTV视频解码器和RGB图形数字转换器

2020-06-15 06:48:29

具有外部穿孔的Viterbi解码器如何解码呢?

根据维特比解码器数据表,硬编码不能进行擦除(外部穿孔)(即仅对软编码有效)。如果我有硬输入,我将如何解码呢?我已经在解码器之前解析了我的数据。我现在需要知道的是,如果我有一个硬输入,我将如何使我

2019-03-14 10:19:54

怎么理解真正的编码器和解码器?

在进入关于编码器和解码器的现实之前,让我们对复用进行简要的思考。通常我们会在需要将一些输入信号一次一个地加载到一个单独负载的应用程序中。选择输入信号中的一个输入信号的过程称为多路复用。这种操作

2020-09-01 17:48:10

模拟列车DCC解码器的资料分享

描述模拟列车 DCC 解码器该解码器包括所有主要功能,前进,后退和运动方向的灯光。所有这些参数都可以在程序中更改,在线编程是一个悬而未决的任务。将在其中添加一个电容器,以保持电力免受轨道中小电流损失的影响。PCB

2022-08-29 06:19:42

编解码器的工作原理是什么?

编解码器是用于对数字媒体文件(如歌曲或视频)进行压缩或解压缩的软件。Windows Media Player 和其他程序使用编解码器来播放并创建数字媒体文件。

2020-04-06 09:00:42

请问如何控制解码器解码的速度呢

请问如何控制解码解码的速度,我发现在解码过程中添加延时会导致解码器错误线程A 往mpp解码器送数据 调用函数decode_put_packet(ffmpeg 拉流)线程B 解码数据 调用函数

2022-09-15 16:05:48

这个很特别 音频解码器

`淘来一块蓝牙板,看屁股应该是音频解码器,前面两个咪咪,一个指示灯一个像信号接收器。应该是树立着使用的东西,和市面上买的解码器设计不一样。接了12v电源,手机能连接上蓝牙,但是接功放没声音。板子上有很多外接插口。如果需要接调音电位器,哪个才是啊?`

2020-03-09 09:16:22

CMOS集成模拟开关的变通应用:脉宽解码器

摘要š用CMOS集成模拟开关变通设计的脉宽解码器不同于目前用于控制中的其它解码器Œ它是一种多通道的串行脉宽解码器" 在与£ ¯³ 模拟开关变通设计的脉宽

2008-09-02 11:25:55 52

52

52

52基于嵌入式Linux的HDTV码流发生器

该文介绍的HDTV 播放系统是在μClinux-Coldfire 操作系统下, 以Coldfire5307 为主控制器控制硬盘进行HDTV 码流读写的。该系统作为解码器的前端, 可以实现HDTV 码流适时播放的功能。该文

2009-05-15 15:40:10 12

12

12

12基于DTMF的解码器设计

本文介绍了DTMF 解码芯片MT8870 的功能和特点,给出了在解码器中与89C51 单片机的接口电路,说明了解码器的工作原理抗干扰措施。关键词:单片机抗干扰 DTMF 解码监控在一

2009-08-19 08:20:53 71

71

71

71基于DTMF的解码器设计

本文介绍了DTMF 解码芯片MT8870 的功能和特点,给出了在解码器中与89C51 单片机的接口电路,说明了解码器的工作原理抗干扰措施。关键词:单片机抗干扰 DTMF 解码监控在一

2009-08-21 09:42:59 34

34

34

34迭代结构的信源信道联合解码及其简化算法

迭代结构的信源信道联合解码及其简化算法:信源信道联合解码算法中的迭代信道解码需要进行比特似然值和概率值转换,以及联乘、累加运算,增加了信道解码的计算复杂度,该文

2009-10-29 13:09:54 12

12

12

12高清数字电视的信源编解码技术

高清数字电视的信源编解码技术

因要显示1920×1080i HDTV高清节目图像,其数字化后的码率在传输中高达995Mbit/s,这比现行模拟电视的传

2009-05-05 09:18:56 1804

1804

1804

1804通过改善视频解码器和编解码器接口降低DVR系统成本

通过改善视频解码器和编解码器接口降低DVR系统成本

在过去几年中,视频监控录像设备的性能得到了极大提升。借助新的硅器件产品,监控 DVR 设计人员可以创建全帧

2010-01-04 11:26:35 1030

1030

1030

1030

基于SC2005的DVB-C机顶盒信源解码器

在机顶盒的研发过程中,信源解码器的研制是整个开发工作的基础和核心。随着机卡分离政策的出台,信源解码器的通用性和复杂性,使其在机顶盒终端的开发过程中变得更

2010-09-11 17:39:13 2617

2617

2617

2617

有效的golomb解码器设计

本文设计了一种有效的适合硬件实现的golomb 解码器 ,并且完成了解码器电路的硬件实现。本设计采用有限状态机与计数器相结合的解码结构,并且对有限状态机的实现进行了优化

2011-06-29 18:05:44 29

29

29

29基于DSP的AVS解码器优化

编码效率高、专利费用低、授权模式简单等优势。AVS解码器的结构复杂、运算量较大,要在嵌入式平台上实现实时解码具有较大难度。在对解码器性能优化的过程中可以依据使用平台对其进行汇编指令集的优化或者针对解码器的关键算法模块进行改良,以上方法对解码器性能的提高均有一

2017-10-30 10:40:15 0

0

0

0基于FPGA的CAVLC解码器设计

为了提高H.264解码器中基于上下文的自适应变长CAVLC解码器的查表速度,本文给出了一种基于FPCJA的CAVLC解码工程解决方案。首先在同一码表中根据码字前缀o的个数对码表进行分组,减小查表的遍历深度。分组后再采用根据后缀计算查表,减少条件判断的次数,以提高查表速度。

2017-11-16 16:55:57 11

11

11

11dmx512解码器怎么接线?dmx512解码器接线图

dmx512解码器,是一款数码影音解码器。这款DMX512解码器,把DMX512/1990标准数码控制信号转换成PWM控制信号,使不具备解码功能的普通LED灯具灯饰接受DMX512主控台的控制。目前已经广泛的运用到了生活当中,下面来看看它的一些知识。

2017-12-06 17:02:43 92181

92181

92181

92181

什么是视频解码器_有什么用

视频解码器是指一个能够对数字视频进行压缩或者解压缩的程序或者设备。 专业级视频解码器IRD2600是一种可根据用户特殊应用而“量身定做的” MPEG-2/DVB标准的综合接收解码器,IRD-2600/H提供各种专业或选定的视频、音频接口。

2018-03-22 15:23:23 31425

31425

31425

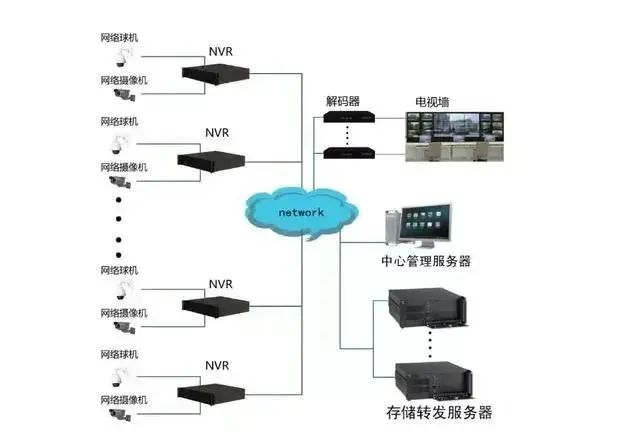

31425高清解码器的作用

高清解码器(xunwei)的主要作用在于接收前端高清编码图像或网络摄像头信号并解码,然后通过自身的各种视频输出接口,如HDMI、DVI、SDI、VGA、BNC输出显示到显示设备上。编码器和解码器

2018-12-10 15:47:43 14448

14448

14448

14448

监控解码器作用

如今是科技快速发展的时代,监控技术也日趋完善,视频解码器是监控系统中比较核心的部分,以下为大家介绍一下监控系统视频解码器的作用,可供参考。

2018-12-10 16:32:08 27606

27606

27606

27606解码器的工作原理

解码器就如同一台笔记本一样,通过解码器上的数据线,与汽车相关的接口对接,从而对汽车各系统进行全方位的身体检测。而且,解码器可以在接收到车主中控钥匙发出的信号之后,将中控钥匙芯片的密码计算出来,从而复制出一把新的钥匙,顶替旧钥匙,让旧钥匙失灵。

2018-12-10 16:35:54 29466

29466

29466

29466

视频编解码器是什么,编解码器技术原理作用

一、什么是视频编解码器 视频编解码器,是指一个能够对数字视频进行压缩或者解压缩的程序或者设备。压缩和可能改变视频内容格式的过程,将模拟源更改为数字源。音频和视频都需要可定制的压缩方法。在压缩方面

2019-06-24 19:02:12 14919

14919

14919

14919为什么编解码器需要解码器模型

通常来说,视频解码器声明支持某个配置文件和级别。配置文件可以指定有关比特深度和色度二次采样的视频格式,以及解码器需要支持的以解码比特流的一组编码工具。

2020-08-10 16:50:16 5435

5435

5435

5435

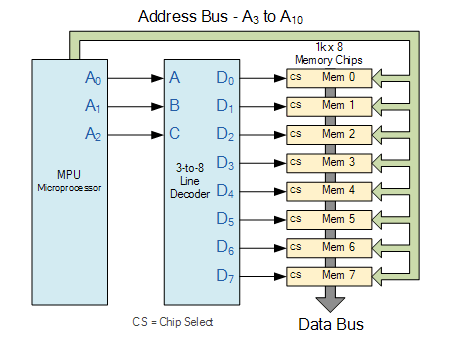

二进制解码器到底是什么

二进制解码器是由单独的逻辑门构成的另一种组合逻辑电路,与编码器完全相反。名称“解码器”是指将编码信息从一种格式转换或解码为另一种格式,因此二进制解码器使用2 n个输出将“ n”个二进制输入信号转换为等效代码。

2021-01-03 17:42:00 7000

7000

7000

7000

适用于PIC和AVR器件的JSON解码器

本文档介绍了 JSON 子集解码器的使用和实现,该解码器面向 PIC®和 AVR®单片机等嵌入式器件。 解码器将 JSON 对象的字符串格式转换为 C 数据结构表示形式,这样编程器便可以访问键值对。使用 JSON 对象可以轻松互连应用程序。

2021-03-30 14:03:28 6

6

6

6ADV7401:10位集成多格式SDTV/HDTV视频解码器和RGB图形数字化器产品手册

ADV7401:10位集成多格式SDTV/HDTV视频解码器和RGB图形数字化器产品手册

2021-04-22 10:15:12 8

8

8

8ADV7802:12位,SDTV/HDTV 3D COM滤波器,视频解码器,和图形Digitizer数据Sheet

ADV7802:12位,SDTV/HDTV 3D COM滤波器,视频解码器,和图形Digitizer数据Sheet

2021-04-24 19:10:08 8

8

8

8ADV7181D:10位、10通道、多格式SDTV/HDTV视频解码器和RGB图形数字化器产品手册

ADV7181D:10位、10通道、多格式SDTV/HDTV视频解码器和RGB图形数字化器产品手册

2021-05-27 18:58:09 4

4

4

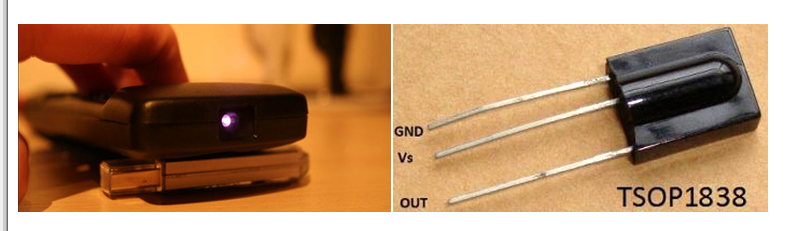

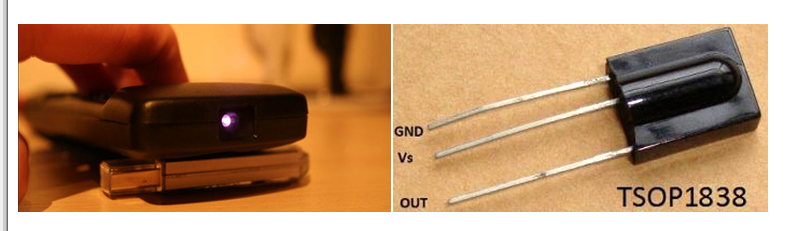

4构建Arduino IR远程解码器的教程

在本教程中,我们将使用 TSOP1838 IR 接收器来构建使用 Arduino 的 IR 远程解码器。每个按钮的十六进制代码都将记录到 Microsoft Excel 表中。这个简单的红外遥控解码器可用于红外遥控机器人、家庭自动化和其他红外控制项目等项目。

2022-08-10 16:52:09 2100

2100

2100

2100

解码器该怎么选?

当一个监控项目中是有多台录像机的时候,每台录像机是可以接显示器来显示图像,但是!它只能显示自己添加的摄像机图像!

* **解码器** **是可以把任意一台录像机的图像的任意一个摄像机放到任意的一块屏来显示的** !这就是解码器的作用!

2023-05-06 11:07:28 5510

5510

5510

5510什么叫解码器?

解码器就是在供电侧的一个电阻元件或电容元件,在安定器的12V侧,串在回路中就行了,目的是防止行车电脑报警,不同的车有不同的解码器,主要是应对车灯功率不足及对行车电脑干扰所加的。解码器就是个小方盒,一般材质为塑料的,有插头,一插就行。

2023-05-06 11:08:26 6901

6901

6901

6901什么是视频解码器?

从定义上来说,视频编解码器,是指一个能够对数字视频进行压缩或者解压缩的程序或者设备。

这么说你可能有些模糊,总的来说,监控系统视频解码器的作用就是把偌大的视频信息进行压缩,然后在有线或无线

2023-05-06 11:10:52 6658

6658

6658

6658

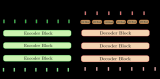

基于transformer的编码器-解码器模型的工作原理

与基于 RNN 的编码器-解码器模型类似,基于 transformer 的编码器-解码器模型由一个编码器和一个解码器组成,且其编码器和解码器均由 残差注意力模块 (residual attention blocks) 堆叠而成。

2023-06-11 14:17:34 3127

3127

3127

3127

基于 RNN 的解码器架构如何建模

Vaswani 等人在其名作 Attention is all you need 中首创了 基于 transformer 的编码器-解码器模型,如今已成为自然语言处理 (natural

2023-06-12 17:08:11 1630

1630

1630

1630

基于 Transformers 的编码器-解码器模型

基于 transformer 的编码器-解码器模型是 表征学习 和 模型架构 这两个领域多年研究成果的结晶。本文简要介绍了神经编码器-解码器模型的历史,更多背景知识,建议读者阅读由

2023-06-16 16:53:21 1688

1688

1688

1688

神经编码器-解码器模型的历史

基于 transformer 的编码器-解码器模型是 表征学习 和 模型架构 这两个领域多年研究成果的结晶。本文简要介绍了神经编码器-解码器模型的历史,更多背景知识,建议读者阅读由

2023-06-20 15:42:00 1659

1659

1659

1659

视频编码器与解码器的应用方案

视频解码器和视频编码器在数字通讯、音视频压缩领域有着广泛的应用。视频编码器作为视频源的发送端,若接收端如果是 PC 机或显示设备就需要通过解码器进行解码播放。

2023-08-14 14:38:42 2006

2006

2006

2006

HiFi音响有必要配解码器吗 hifi解码器起什么作用

HiFi解码器在音频系统中起到以下几个重要作用:

1. 解码数字音频信号:HiFi解码器可以将数字音频信号(如Dolby Digital、DTS、FLAC、ALAC等格式)解码成模拟

2023-08-23 15:56:31 18951

18951

18951

18951光栅解码器损坏的表现有哪些

光栅解码器是一种用于将光信号转换为电信号的设备,广泛应用于光学存储、光学测量、光学通信等领域。当光栅解码器损坏时,可能会出现多种异常表现。以下是一些可能的表现,以及相应的分析: 信号失真 : 原因

2024-09-23 17:57:17 1864

1864

1864

18649740解码器配什么光栅

关于9740解码器配什么光栅的问题,由于直接针对特定型号(如9740解码器)与光栅配套信息的资料可能较为有限,且这种信息可能因厂商、产品系列及具体应用场景的不同而有所差异,因此无法给出一个绝对确定

2024-09-23 18:01:29 1419

1419

1419

1419全景声解码器

全景声解码器是一款将音频技术推向极致的产品。它不仅提供高质量的音频解码,还让用户体验到一种前所未有的声音空间。无论您是想要享受音乐、观看电影,还是沉浸于游戏世界,全景声解码器都能为您打开一个新的音频维度,让每一次聆听都成为一次精彩的旅程。

2024-09-24 10:40:33 1444

1444

1444

1444

遥控器解码器怎么使用

遥控器解码器是一种用于解码和复制遥控器信号的设备,它可以帮助用户在遥控器丢失或损坏的情况下,重新获得对设备的控制。 遥控器解码器使用指南 1. 了解遥控器解码器 遥控器解码器是一种电子设备,它能

2024-09-30 14:23:01 3984

3984

3984

3984控制器解码器的使用方法

控制器解码器是一种用于解析和执行控制信号的设备,广泛应用于工业自动化、机器人技术、航空航天等领域。它通常与传感器、执行器等设备配合使用,以实现对机械或系统的精确控制。 1. 理解控制器解码器

2024-09-30 14:24:42 2584

2584

2584

2584解码器和控制器区别是什么

解码器和控制器在数字电子电路中扮演着不同的角色,它们之间的主要区别体现在功能和应用场景上。 一、功能区别 解码器 : 主要功能 :解码器通常用于将编码后的数据或信号转换成相应的输出信号。在数

2024-09-30 14:27:07 2292

2292

2292

2292无线网解码器怎么连接

无线网解码器的连接方式可能因设备型号、品牌以及应用场景的不同而有所差异。以下提供的是一种较为通用的连接步骤,但请注意,在实际操作中应参考具体设备的说明书或官方指导进行操作。 一、设备准备 无线网

2024-10-15 16:31:13 2124

2124

2124

2124 电子发烧友App

电子发烧友App

评论