作者:lee 在实现多级CIC滤波器前我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理。CIC滤波器在通信信号处理中有着重要的应用。 这篇文章来介绍梳状滤波器以及积分梳状滤波器,为up

2020-11-21 09:57:00 5220

5220

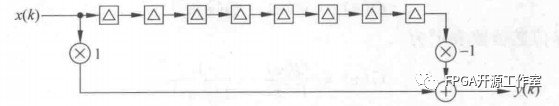

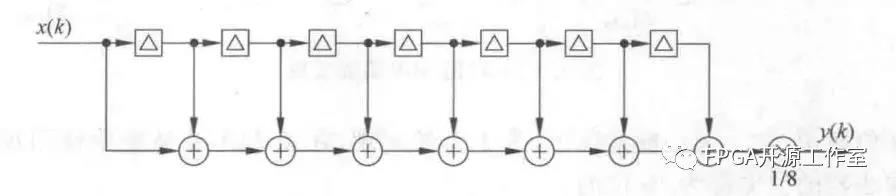

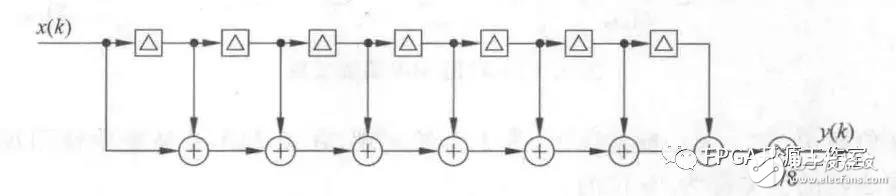

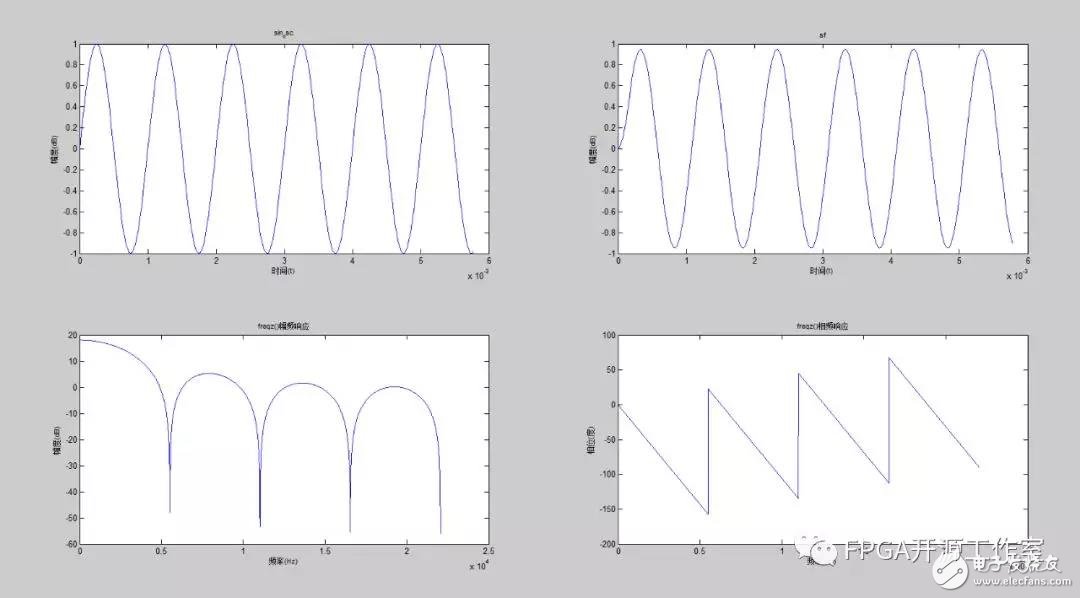

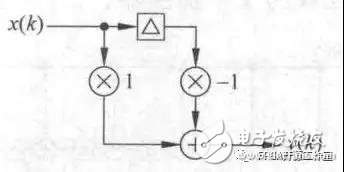

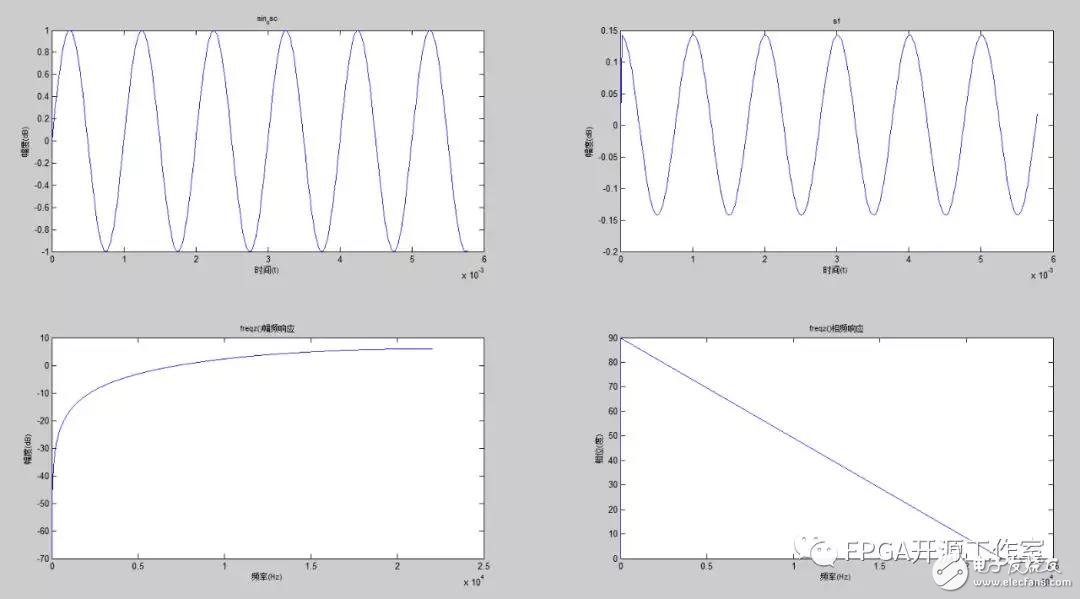

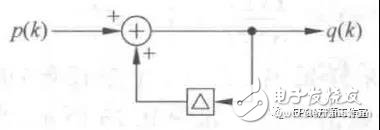

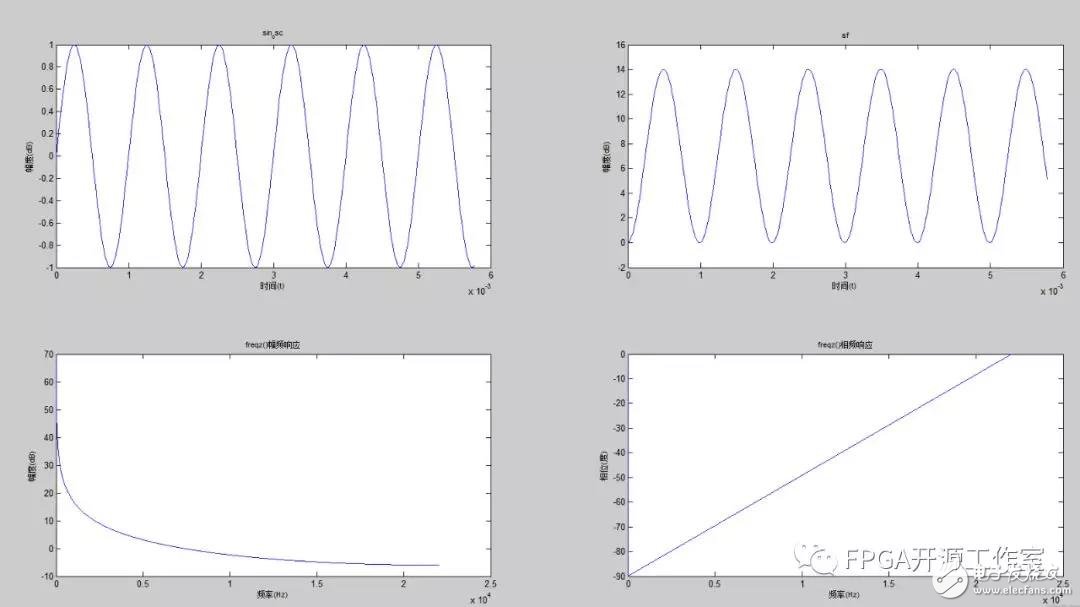

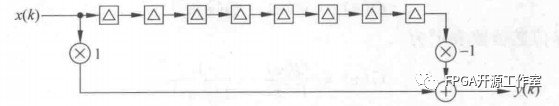

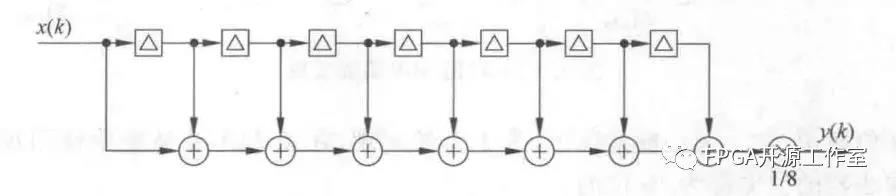

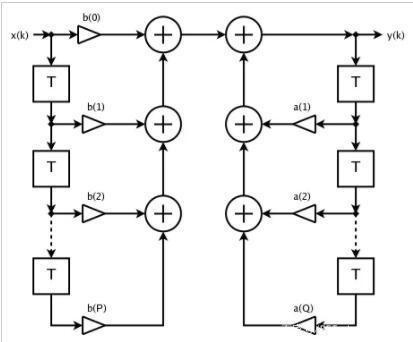

在实现多级CIC滤波器前我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理。CIC滤波器在通信信号处理中有着重要的应用。 1、滑动平均滤波器 图1 8权值滑动平均滤波器结构 滑动平均滤波器

2020-12-03 11:55:06 5078

5078

作者: OpenSLee 1 概述 在数字信号处理中,CIC滤波器是FIR滤波器中最优的一种,其使用了积分,梳状滤波器级联的方式。 CIC滤波器由一对或多对积分-梳状滤波器组成,在抽取CIC中,输入

2020-12-05 10:21:00 2654

2654 在本文中,我们将简要介绍不同类型的滤波器,然后学习如何实现移动平均滤波器并使用CIC架构对其进行优化。

2023-10-02 15:38:00 943

943

整数倍内插是先在已知抽样序列的相邻两个抽样点之间等间隔地插入(I-1)个零值点,然后进行低通滤波器,即可求得I倍内插的结果。

2020-11-20 09:55:22 6196

6196 文章主要讲CIC理论基础,下个文章讲FPGA实现。级联积分梳状滤波器又称CIC。这是多速率信号处理中一种结构简单的滤波器,只需要加法器和寄存器即可实现,可以灵活的设置抽取因子和插值因子,并且CIC是一

2021-08-17 08:27:40

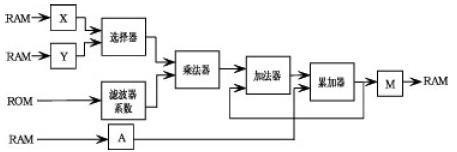

fpga实现滤波器fpga实现滤波器在利用FPGA实现数字信号处理方面,分布式算法发挥着关键作用,与传统的乘加结构相比,具有并行处理的高效性特点。本文研究了一种16阶FIR滤波器的FPGA设计方法

2012-08-12 11:50:16

。本文研究了一种16阶FIR滤波器的FPGA设计方法,采用Verilog HDI语言描述设计文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平台上进行了实验仿真及时序分析,并探讨了实际工程中硬件资源利用率及运算速度等问题。

2012-08-11 18:27:41

最近在做一个FPGA的课程设计,遇到一个比较烦人的问题,希望大神们可以指点迷律。一个16阶的FIR滤波器,采用分布式算法实现的,采样率1M,fc=100K,频率到了30K以上时就会出现那些尖刺,很

2018-02-25 19:25:50

对CIC抽取滤波器的结构进行分解,得出一个能实现任意抽取因子的改进的CIC抽取滤波器的实现结构。最后的仿真表明:该设计方法使得CIC抽取滤波器性能得到改善,实现结构高效,在实际工程中有很大的应用价值

2010-06-02 10:07:03

系数分别为N1,N2,…,Ns的较小、较简单的级联滤波器。抽取系数满足以下等式:在考虑各种滤波器的特性基础上,抽取系统采取多级抽取组分组级联的方式。为了有效利用FPGA资源,采用16倍CIC滤波器

2009-10-23 10:26:53

PRD1211,5 Vin,200 Vout,2 mA参考设计。本设计使用带四倍电荷泵的升压转换器。它采用创新的4级电荷泵,将升压级的输出电压提高4倍。可以使用许多不满额定输出电压的器件。此外,级联FET(Q1)用于提高ADP1613的电压能力

2019-07-17 08:11:56

现在接收的455k左右的收音机信号,经过乘法后,要经过CIC滤波器和FIR滤波器,不知道该怎么设置参数,求解救啊,调了很久一只没出来!!!!

2013-08-17 11:45:35

hamming窗,通带截止频率为3.2KHz.由于采样率与通带截止频率相差太大,无法直接设计出满足要求的FIR滤波器。于是就采用了积分梳状滤波器CIC后接FIR滤波器,CIC是为了抽取已达到降低FIR采样频率

2013-05-26 19:57:13

抽取滤波器的硬件实现6.5.3 多相插值滤波器的基本理论6.5.4 多相插值滤波器的硬件实现6.6 CIC滤波器6.6.1 CIC滤波器的基本理论6.6.2 CIC滤波器的比特增长问题6.6.3

2012-04-24 09:33:23

低通滤波器,用来限制信号的频带,然后再进行抽取,这样的话我们来算一下低通滤波器的截止频率就是1/2倍的经抽取后的采样速率,即fc = 1/2 * (F1/M) ,M是抽取倍数。而1/2*F1对应的数域频率

2018-11-15 00:27:19

滤波器的阶数与内插/抽取的倍数相同时,其结构更利于FPGA实现。比如抽取时,只需要将D个数据组成一组,相加作为一个输出即可(即同时完成了滤波与抽取)。结合下面的实例理解(设CIC滤波器阶数与抽取倍数都为5

2020-09-28 09:36:54

高通滤波器;采用方案2,利用无源LC滤波器技术来实现四阶椭圆低通滤波器。 2 系统总体设计方案及实现方框图本系统以单片机及FPGA为控制核心,由可控增益放大模块、程控滤波模块和幅频特性测试模块构成

2019-09-29 14:08:52

基于FPGA的四阶IIR数字滤波器怎么样?

2021-04-29 06:21:49

设计一般采用CIC、HB、FIR级联的形式组成。同时,由于CIC滤波器的通带性能实在太差,所以中间还要加上一级PFIR滤波器以平滑滤波器的通带性能。

2019-09-20 06:13:11

本帖最后由 eehome 于 2013-1-5 09:50 编辑

基于FPGA的FIR滤波器设计与实现 文章研究基于FPGA、采用分布式算法实现FIR滤波器的原理和方法,用

2012-08-11 15:32:34

基于FPGA的fir滤波器实现

2017-08-28 19:57:36

本帖最后由 eehome 于 2013-1-5 09:50 编辑

基于fpga的fir滤波器的实现

2012-08-17 16:42:33

成长,CIC低通滤波器得到了广泛的应用。长期以来,CIC梳状滤波器一般是在通用DSP处理器上实现的,由于DSP处理器的顺序执行特性的限制,其速度很难满足一些高速抽取与插值系统的需要。FPGA具有优良的全硬件并行执行的特性,研究CIC梳状滤波器的设计及其FPGA实现具有重要的现实意义。

2019-09-23 07:22:30

滤波器是任何信号处理系统的关键组成部分,随着现代应用的日趋复杂,滤波器设计的复杂程度也日益提高。采用 FPGA 设计和实现的高性能滤波器的能力是模拟方法所望尘莫及的。另外,采用FPGA

2019-09-18 08:28:47

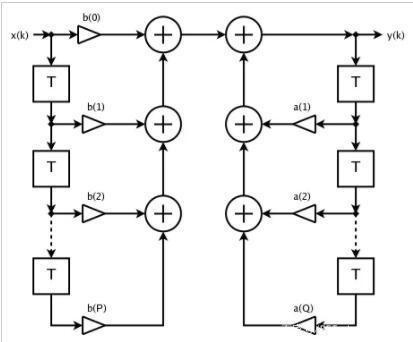

本文介绍了一种采用级联结构在FPGA上实现IIR数字滤波器的方法。

2021-04-15 06:16:32

本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2021-04-29 06:50:18

本文将介绍线路调制的FPGA实现,包括:线路调制单元数字化实现的总体设计,CIC和FIR滤波器的FPGA实现以及载波发生器单元的设计。

2021-04-29 06:41:28

滤波器在FPGA中的实现用FPGA来实现滤波器的设计优点用FPGA来设计滤波器,不但设计简单,而且成本小,可靠性好。且无需像传统的设计芯片一样进行测试。主要优点:设计简洁。若设计有误,则只需

2021-07-30 07:03:10

如何用中档FPGA实现多相滤波器?

2021-04-29 06:30:57

原先的fs就对应6pi,信号带宽也就变成了2pi。 而抽取滤波器则刚好相反,对于3倍的插值滤波器,信号带宽在数字频率上,缩小了1/3。也就是原来0pi的区间缩小到0pi/3,因此信号的截止频率

2020-12-24 16:03:16

ad9777芯片手册的内插问题,对ad9777的寄存器进行配置,可以实现数据的四倍内插嘛?

2023-12-01 06:03:09

并行流水结构FIR的原理是什么基于并行流水线结构的可重配FIR滤波器的FPGA实现

2021-04-29 06:30:54

目前FIR滤波器的硬件实现的方式有哪几种?怎么在FPGA上实现FIR滤波器的设计?

2021-05-07 06:03:13

)接收多通道数字数据 - 有16个数据通道通过SPI串行接口进入FPGA。数字数据被过采样(10kHz采样率)。每个样本16位。(2)将多通道数据抽取/下采样4倍(可能使用CIC滤波器,或CIC

2019-04-17 09:17:26

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。

2021-05-07 06:02:47

为什么要设计一种理想滤波器呢?CIC抽取滤波器是由哪些部分组成的?怎样去设计一种CIC抽取滤波器并对其进行MATLAB仿真呢?

2021-11-19 07:29:44

256KHZ,输出1bit数字信号,现需要降采样,抽取因子128,要求最终输出24bit,拟用三级结构,第一级为5阶的抽取率为32的cic滤波器,第二级为抽取率为2的cic补偿滤波器,第三极为半带滤波器

2012-02-26 22:00:16

256KHZ,输出1bit数字信号,现需要降采样,抽取因子128,要求最终输出24bit,拟用三级结构,第一级为5阶的抽取率为32的cic滤波器,第二级为抽取率为2的cic补偿滤波器,第三极为半带滤波器,滤波器的截止频率为1K。硬件实现,望各位大侠指点。wbpotato@163.com qq:446497438.

2012-02-26 15:52:55

分布式的滤波器算法是什么?一种基于FPGA分布式算法的滤波器设计实现

2021-04-29 07:13:23

用FPGA来实现滤波器的设计优点有哪些?

2021-11-05 07:59:53

(FIR,HBF,CIC)进行了简要介绍,对其实际性能进行了对比分析。最后,采用Matlab与FPGA硬件平台相结合的设计方法对性能最合适的FIR滤波器进行硬件实现、联合仿真、测试与验证,该设计方法

2010-04-22 11:30:26

设计采用ADP1613升压转换器和四倍电荷泵。它采用创新的4级电荷泵,将升压级的输出电压提高4倍。可以使用许多不满额定输出电压的器件。此外,级联FET(Q1)用于提高ADP1613的电压能力。使我们能够使用非常便宜的集成FET升压控制器

2019-07-16 06:35:37

谁有cic插值滤波器的代码,能分享下吗,实在不会

2017-04-18 20:01:06

硬件上实现了。四、FIR半带滤波器的FPGA设计这次我们直接调用FIR滤波器的IP核来设计,非常的方便,我们只需要做一下顶层的理化,考虑一下有限字长的影响,就可以将工作交给IP去做,而且效率比我们自己写

2015-08-29 15:33:49

适合应用在多速率信号处理的前端,作为抗混叠滤波器来用,或者是作为后端的抗混叠插值滤波器。七、多级 Hogenauer CIC抽取滤波器的FPGA实现 Hogenauer CIC抽取滤波器是一种特殊

2015-08-29 15:25:38

起见,我们自己定义滤波器的通阻带,采样频率以及通阻带衰减,尽量让滤波器阶数小一点,方便我们后边的FPGA实现,毕竟这只是个例子,简单一点比较好,如果真的当做工程设计来做,那就具体情况具体分析了 滤波器

2015-08-29 15:37:11

讨论了软件无线电接收机中数字下变频处理技术中的CIC抽取滤波器结构原理,分析了CIC滤波器级联ISOP滤波器进行抽取滤波的设计技术。验证了ISOP滤波器对CIC滤波器带内衰减补偿的有

2009-05-26 20:44:21 21

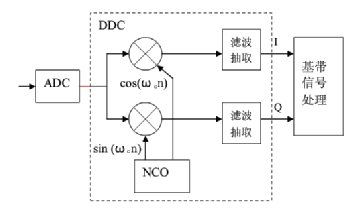

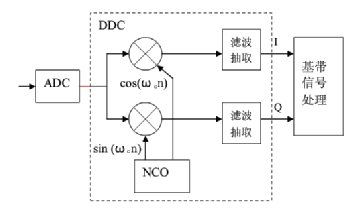

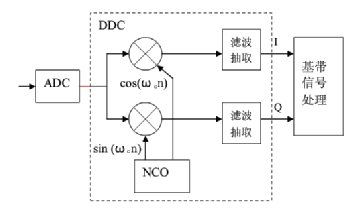

21 探讨了DDC中抽取滤波系统的设计方法和基于DSP Builder的具体实现方案,采用CIC滤波器、HB滤波器、FIR滤波器三级级联的方式来降低采样率,并进行了模型仿真,结果表明设计是可行的

2009-09-17 11:35:08 23

23 插值和抽取滤波器被广泛应用于现代通信系统中,然而基于传统DSP 或者FPGA 的滤波器,具有数据率低和占用资源多的缺点。为了克服这些缺点,本文针对一种多核DSP 处理器, 提出

2009-11-27 15:26:57 9

9 在软件无线电的下变频模块中,级联梳状积分滤波器有着重要的应用,其主要作用是信号的抽取与低通滤波。文中总结了级联梳状积分抽取滤波器的理论要点,并介绍了采用FPGA

2010-01-06 15:16:45 31

31 数字滤波器在FPGA中的实现

2010-02-09 10:21:27 76

76 设计一个由现场可编程门阵列(FPGA)控制的滤波器。该滤波器主要由3个模块组成:前置放大、滤波电路、FPGA显示与控制电路等利用FPGA作为放大器及程控滤波器电路中继电器组的控制模

2010-07-17 18:00:09 45

45 在研究了低轨卫星DS-CDMA系统数字上变频器的内插技术之后,提出了以成型滤波器、半带滤波器和CIC滤波器等多级内插级联的结构来实现抽样率的变换.在具体实现上采用了基于多相结

2010-10-15 09:51:18 15

15 IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此

2008-01-16 09:45:39 2276

2276

摘要: 针对在FPGA中实现FIR滤波器的关键--乘法运算的高效实现进行了研究,给了了将乘法化为查表的DA算法,并采用这一算法设计了FIR滤波器。通过FPGA仿零点验证

2009-06-20 14:09:36 677

677

摘 要:为了降低地震数据采集系统的成本和功耗,采用数字信号处理器(DSP)实现-△模数转换器中的数字抽取滤波器算法。通过采取查表法、倒序循环遍历法以及模拟循环寻址法等优化方法,以较低工作频率实现了四通道四级抽取滤波运算,达到了系统设计的要求。

2011-02-25 16:00:23 68

68 CIC滤波器是一种结构简单、规整,占用存储量小的滤波器,不需要乘法器,非常适用于高速采样和插值比很大的场合。本文介绍了一般CIC滤波器的结构,展示了组成CIC滤波器的2个基本单元,以及它们各自的数学本质与Z变换下的意义。介绍了内插器和抽取器这2种CIC滤

2011-03-15 12:21:50 68

68 为补偿传统CIC滤波器的通带衰减,提出一种改进型的CIC抽取滤波器,即在SCIC滤波器之后级联一个二阶多项式内插滤波器。基于硬件实现的要求,给出改进型CIC滤波器的FPGA高效实现原理图。仿真结果表明改进的CIC滤波器具有更好的通阻带特性。

2011-03-15 14:06:35 52

52 本文主要论述了用于音频系统ADC的过采样抽取滤波器的设计 系统论述了滤波器的多级实现

2011-04-19 10:21:56 94

94 为了解决高速抽取滤波器系统中传统CIC滤波器旁瓣抑制不够的问题,通过对级联COSINE抽取滤波器和传统CIC抽取滤波器的原理推导进行对比,分析出级联COSINE滤波器在幅频特性上同CIC滤波

2011-05-03 18:11:53 31

31 基于多速率信号处理原理,设计了用于下变频的CIC抽取滤波器,由于CIC滤波器结构只用到加法器和延迟器,没有乘法器,很适合用FPGA来实现,所以本文分析了CIC滤波器的原理,性能及影

2011-08-26 15:12:11 160

160 CIC滤波器是常用于多速率采样抽取或内插过程中的高效滤波器,具有结构简单,易于工程实现的特点。以提高采样速率为例,首先介绍了内插理论和CtC滤波器原理,重点给出了CIC滤波器

2011-09-20 15:12:49 73

73 为了较好地解决软件无线电技术应用中任意采样率转换的问题,本文引入了时变CIC滤波器。其对传统的先内插后抽取的多级CIC结构的中间状态进行等效变换,避免了在较高频率下处理信

2011-09-20 15:26:46 57

57 为了产生调制信号的码元速率能在大范围内实时可变,采用插值滤波技术 多级积分梳状滤波器。在分析多级滤波器的结构和特性的基础上,阐述了一种利用剪除理论实现多级滤波器的高效

2011-12-26 18:33:08 25

25 本文首先对CIC、HB、FIR滤波器的原理及设计作了简单的说明,最后用Matlab结合System generator对本文所设计的DDC滤波器作了一个仿真。

2012-08-06 15:34:48 10298

10298

文中基于多速率数字信号处理原理,设计了用于数字下变频技术的CIC抽取滤波器。通过分析CIC滤波器的原理及性能参数,利用MATLAB设计了符合系统要求的CIC滤波器,并通过FPGA实现了CI

2013-04-15 19:29:28 71

71 条件,设计并实现了基于FPGA的菱形滤波窗口及其功能仿真,并对两种滤波窗口的硬件结构进行FPGA资源消耗的对比,说明文中设计的菱形滤波器对消除地层噪声干扰有很强的实用性。

2015-12-31 09:20:25 8

8 matlab与24倍插值CIC滤波器设计,有兴趣的同学可以下载学习

2016-04-27 15:51:58 56

56 4阶24倍抽取CIC滤波器设计,有兴趣的同学可以下载学习

2016-04-27 15:51:58 26

26 基于FPGA的FIR滤波器设计与实现,下来看看

2016-05-10 11:49:02 38

38 研究了一种采用FPGA实现32阶FIR滤波器硬件电路方案;讨论了窗函数的选择、滤波器的结构以及系数量化问题;研究了FIR滤波器的FPGA实现,各模块的设计以及如何优化硬件资源,提高运行

2017-11-10 16:41:57 15

15 ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上实现了一种下采样率为64的抽取滤波器。Modelsim仿真结果表明,该抽取滤波器设计是有效的,达到了设计指标。

2017-11-17 09:01:55 5303

5303 前端的调制器利用过采样的方法将量化噪声搬移到高频段,后端的数字抽取滤波器必须再将高频噪声滤除,所以数字抽取滤波器的性能在整个Σ-∆ ADC中起着非常重要的作用。我们选用了一种抽取滤波器Sinck数字滤波器,它可以有效的滤除高频噪声满足设计的需要,并且这种滤波器的算法中不需要乘法。

2018-07-18 18:31:00 3664

3664

(降2倍)和半带滤波器(降2倍)组成。为了实现高频工作,CIC滤波器采用两级结构,第一级采用多相分解技术,使大部分结构工作在较低时钟频率下,极大地降低了CIC的功耗,第二级采用传统结构。CIC补偿滤波器使信号通带平坦,半带滤波器满足了阻带的衰减要求。

2018-02-21 12:08:00 1815

1815

文介绍了FIR抽取滤波器的工作原理,重点阐述了用XC2V1000实现FIR抽取滤波器的方法,并给出了仿真波形和设计特点。

2018-04-19 11:34:00 1846

1846

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2018-04-28 11:50:00 1072

1072

通带纹波和阻带衰减等要求,数字抽取滤波器一般采用CIC滤波器、CIC补偿滤波器、半带滤波器三级级联方式构成[1]。本文在此结构的基础上,对CIC滤波器部分进行优化,通过级联结构和多相分解技术,最终有效地降低了CIC滤波器的功耗,提升了滤波器的运算速度。

2018-06-29 14:32:00 11289

11289

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2020-09-25 10:44:00 3

3 针对Σ△ADC输出端存在的高频噪声问题,设计了一种 Sinc数字抽取滤波器,实现了Σ-△调制器输出信号的高频滤波。分析了Sinc滤波器的结构原理,基于 Spartan6FPGA进行滤波器的设计与实现

2020-08-26 17:12:00 14

14 WCDMA中规定了小区搜索的时隙同步过程采用匹配滤波器的方法实现,本论文主要研究匹配滤波器原理及FPGA实现结构。

2021-01-26 16:22:43 12

12 基于FPGA的_ADC数字抽取滤波器Sinc_3设计(现代电源技术基础杨飞)-该文档为基于FPGA的_ADC数字抽取滤波器Sinc_3设计总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-09-16 13:58:04 20

20 积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC 滤波器结构简单,没有乘法器,只有加法器、积分器和寄存器

2023-03-27 11:40:23 886

886

加法器、积分器和寄存器,适合于工作在高采样率条件下,而且CIC滤波器是一种基于零点相消的FIR滤波器,已经被证明是在高速抽取或插值系统中非常有效的单元。 我们首先产生一个采样率Fs=0.78125Mhz,频率Fout=0.078125Mhz的样本信号,对其进行16倍插值。这就涉及到直接频率合成器DDS的知识。

2023-04-12 10:26:25 597

597 积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。

2023-06-01 11:05:41 1166

1166

电子发烧友App

电子发烧友App

评论