电子发烧友网站提供《在Spartan 6 FPGA上从头开始实现全加器.zip》资料免费下载

2023-06-15 10:13:28 0

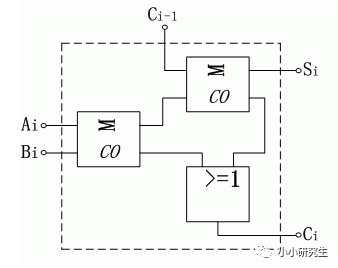

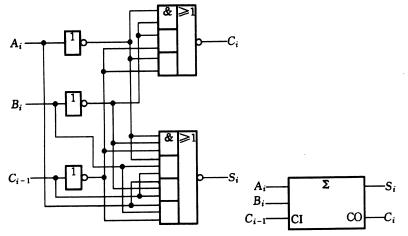

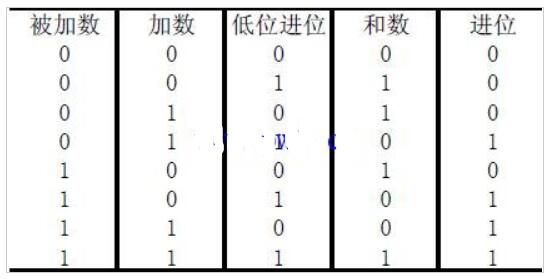

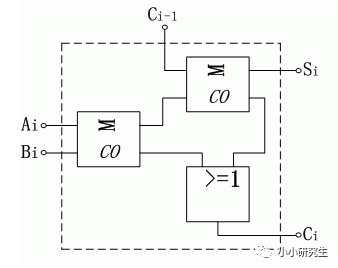

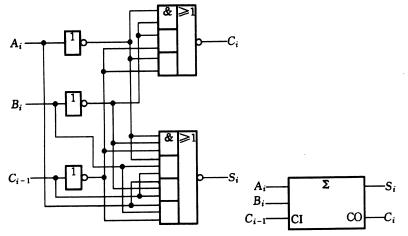

0 首先半加器是A+B构成了{C,S}。由于全加器多了一个低位的进位,就是将{C,S}再加上Ci-1。

2023-05-22 15:26:35 583

583

在上一节半加器中,介绍了全加器可看作两个半加器和一个或门组成。

2023-05-14 15:07:47 837

837

注册表解锁方法1 编辑一个注册表解锁项,加进注册表。 方法:新建记事本,输入"REGEDIT4 [HKEY_CURRENT_USER

2008-06-03 17:49:32

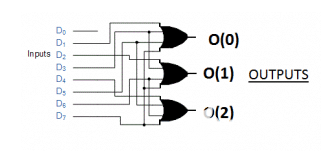

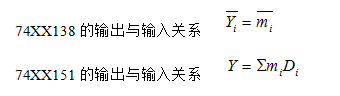

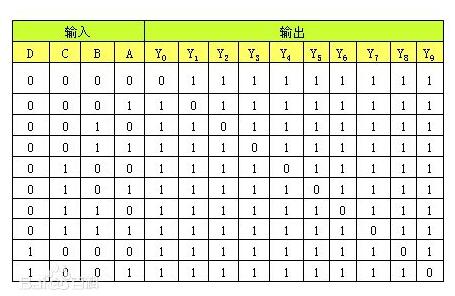

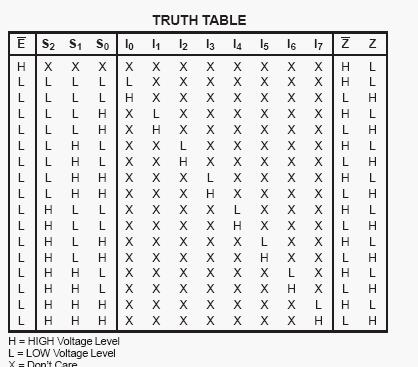

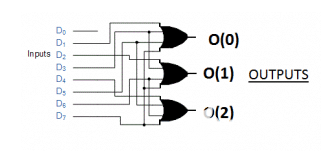

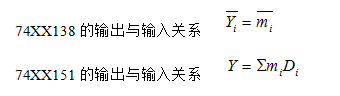

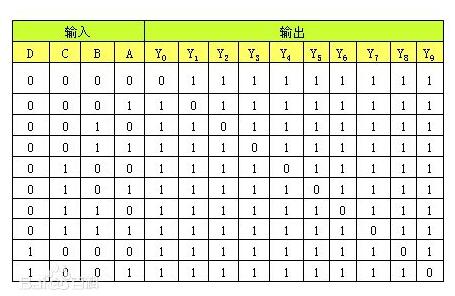

编码器和解码器是组合逻辑电路,在其中,主要借助布尔代数实现组合逻辑。今天就大家了解一下编码器和解码器电路,分别从定义,工作原理,应用,真值表几个方面讲述一下。

2022-11-03 09:22:57 3470

3470

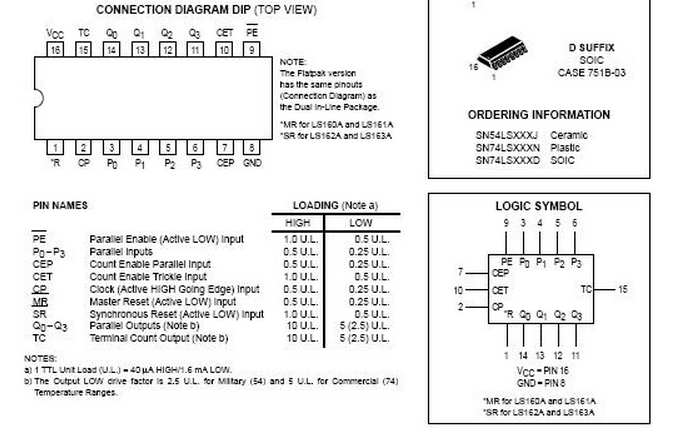

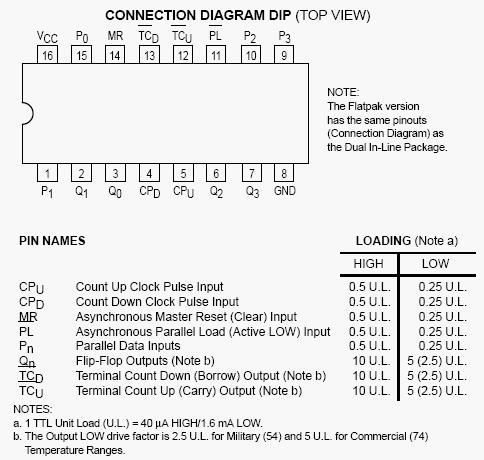

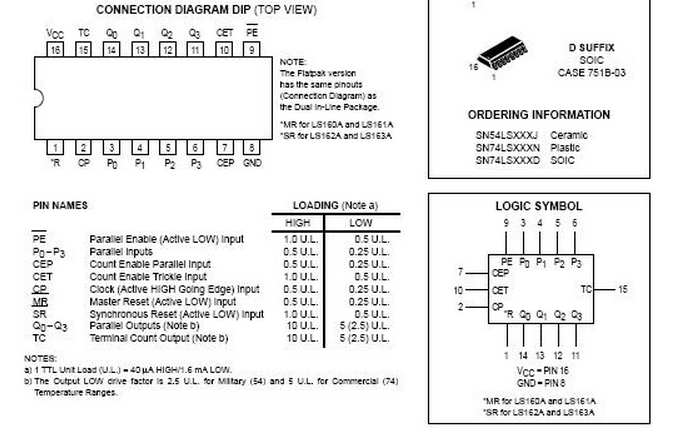

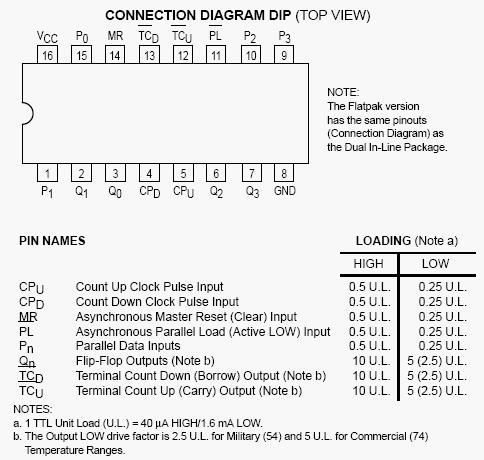

74ls160引脚图管脚图及功能真值表,74ls160引脚图管脚图74LS160的功能真值表-综合电路图 74ls160引脚图管脚图 74LS160的功能真值表

2022-05-25 16:39:14 102427

102427

Verilog数字系统设计四复杂组合逻辑实验2文章目录Verilog数字系统设计四前言一、什么是8位全加器和8为带超前进位的全加器?二、编程1.要求:2.门级原语实现8位全加器:3.门级原语实现带

2021-12-05 19:06:10 4

4 多思计算机组成原理网络虚拟实验系统计算机组成原理实验一全加器实验

2021-10-22 10:36:12 11

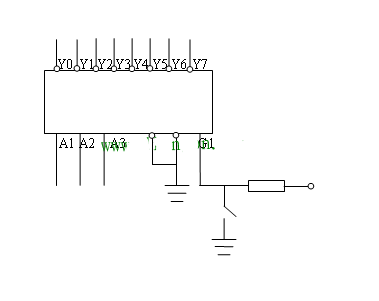

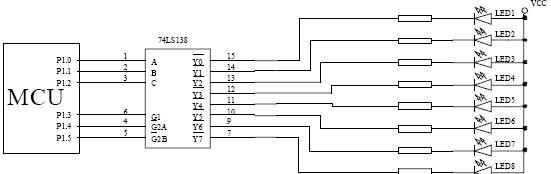

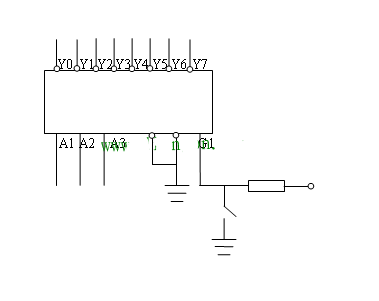

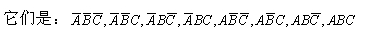

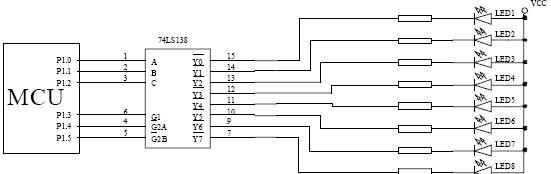

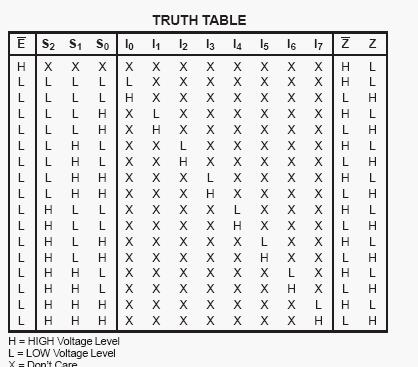

11 38译码器也就是三线八线译码器,那么38译码器真值表以及功能与原理是什么呢,下面小编就为大家来带38译码器真值表以及功能与原理。 三线八线译码器的三线是指三位二进制数字,其会组成000到111共八个

2021-07-08 15:55:54 97073

97073

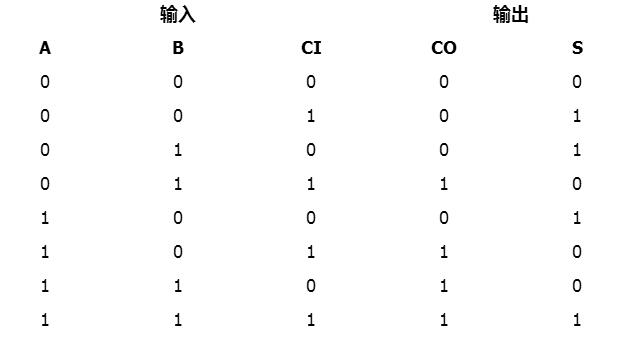

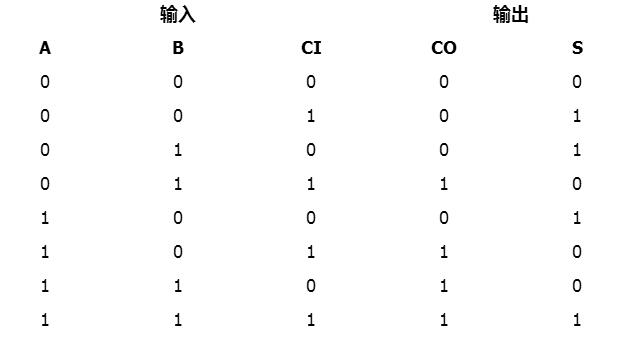

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,多个一位全加器进行级联可以得到多位。全加器是形成三位算术和的组合电路,它由三个输入和两个输出组成。

2021-06-29 09:14:46 53586

53586

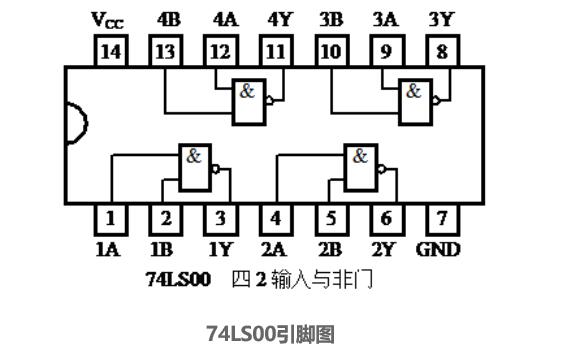

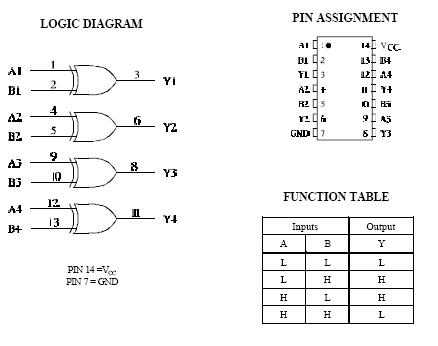

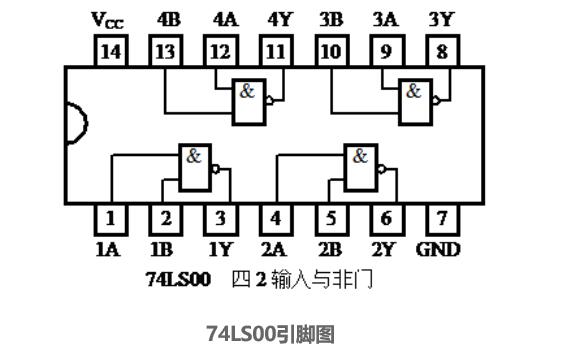

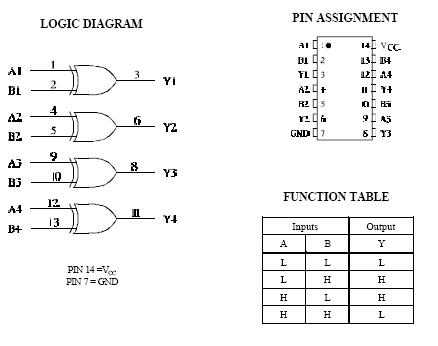

本文主要介绍74ls00引脚图及功能、真值表和特性参数。

2021-06-16 16:02:03 150922

150922

全加器的输入端有三个,分别为A、B、C(低位的进位);两个输出S(和);C(运算产生的进位)。

2020-04-23 09:59:42 96058

96058

本文主要介绍了全加器逻辑表达式及全加器的逻辑功能。

2020-04-23 09:51:14 105979

105979

全加器是数字信号处理器微处理器中的重要单元,它不仅能完成加法,还能参与减法、乘法、除法等运算,所以,。提高全加器性能具有重要意义。本文分析了两种普通全加器,运用布尔代数对全加器和的数、进位函数进行

2019-07-03 17:11:16 38

38 本文档的主要内容详细介绍的是VHDL语言设计的全加器源代码和工程文件免费下载。

2019-06-03 08:00:00 4

4 全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。

2018-07-25 16:03:28 73111

73111 半加器、全加器是组合电路中的基本元器件,也是CPU中处理加法运算的核心,理解、掌握并熟练应用是硬件课程的最基本要求。

2018-07-25 14:39:45 130197

130197

加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器。

2018-07-25 11:15:53 65775

65775

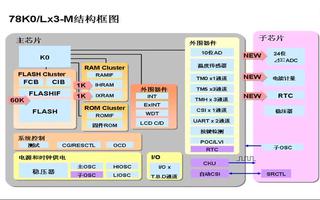

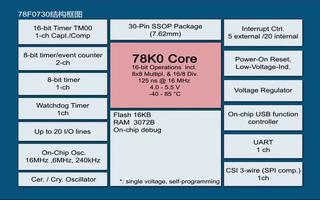

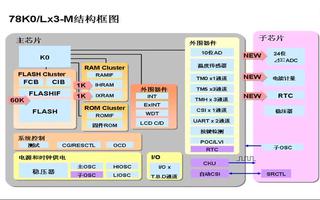

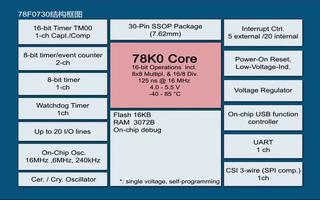

国网电能表解决方案

2018-07-23 00:34:00 4323

4323

插座表解决方案

2018-07-23 00:13:00 2610

2610

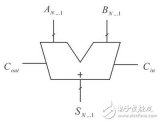

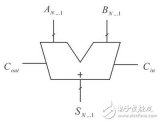

N位全加器将{AN,……,A1}、{BN,……,B1}和进位输入Cin作为输入,计算得到和{SN,……,S1}以及最高位的进位输出Cout(见图1)。每一位得到的和与进位输出都直接受其上一位的影响,其进位输出也会影响下一位。最终,整个全加器的和与输出都受进位输入Cin的影响。

2018-06-08 10:24:00 3995

3995

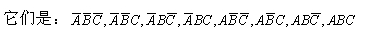

本文主要介绍了用74ls151实现全加器设计电路。根据全加器的定义可知:输入为:A,B,Ci其中A,B为被加数和加数,Ci为低位进位数。输出为:S,Co,其中S为本位和数,Co为高位进位数。其逻辑关系为:S=A⊕B⊕Ci;Co=AB+(A⊕B)Ci。

2018-05-07 09:52:22 106645

106645

本文主要介绍了逻辑真值表怎么列出的_真值表是怎么画出来的。一个逻辑函数的卡诺图就是将此函数的最小项表达式中的各最小项相应地填入一个特定的方格图内,此方格图称为卡诺图。由A、B、C三个逻辑变量构成

2018-04-09 11:45:02 218331

218331

与门真值表和与非门真值表的区别,与门真值表:有0出0,全1出1。与非门真值表:有0出1,全1出0。

2018-01-30 15:37:07 113692

113692

表征逻辑事件输入和输出之间全部可能状态的表格。列出命题公式真假值的表。通常以1表示真,0 表示假。命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。

2018-01-30 15:16:13 62364

62364

Avago Technologies智能仪表解决方案

2016-06-02 15:59:14 5

5 智能仪表解决方案 ,电力工业上要用到的PDF

2016-01-06 15:38:45 1

1 实验五 全加器、译码器及数码显示电路 一、实验目的 1、掌握全加器逻辑功能,熟悉集成加法器功能及其使用方法。 2、掌握用七段译码器和七段数码管显示十进制数的方法。 3、掌握

2012-07-16 23:01:22 37

37 本文旨在通过对恩智浦半导体智能电表解决方案的介绍,使大家对非接触式预付费智能表系统有一个整体的认识。本文还对一些常见问题做出了回答

2011-05-26 10:16:23 11015

11015

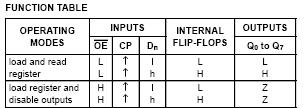

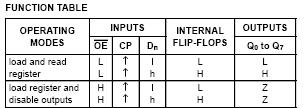

本文是74ls175的真值表及74ls175功能描述

2011-03-20 17:00:52 24846

24846

本资料有74ls138真值表_74ls138功能表。

2011-03-20 14:25:55 69

69 基于单电子晶体管的I-V特性和传输晶体管的设计思想,用多栅单电子晶体管作为传输晶体管,设计了一个由5个SET构成的全加器,相对于静态互补逻辑设计的全加器,本文设计的全加器在器

2010-07-30 16:54:22 18

18 什么是一位全加器,其原理是什么

加器是能够计算低位进位的二进制加法电路

一位全加器由2个半加

2010-03-08 17:13:33 72422

72422 全加器,全加器是什么意思

full-adder 用门电路实现两个二进数相加并求出和的组合线路,称为一个全加器。

2010-03-08 17:04:58 78218

78218 真值表,真值表是什么意思

把变量的各种可能取值与想对应的函数值,用表格的形式一一列举出来,这种表格就叫做真值表。设一个变量均有0、1两

2010-03-08 11:03:15 26920

26920 全加器

全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。 根据全加器的功能,可列出它的真值表:

2009-04-07 10:34:54 8256

8256

74hc574功能真值表及引脚管脚图

2009-04-01 15:13:52 19357

19357

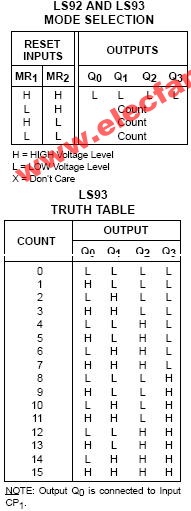

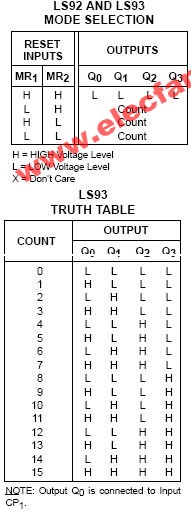

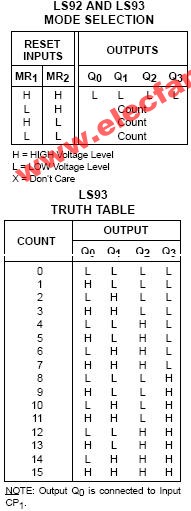

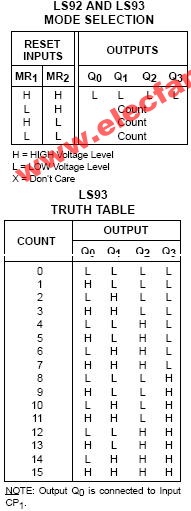

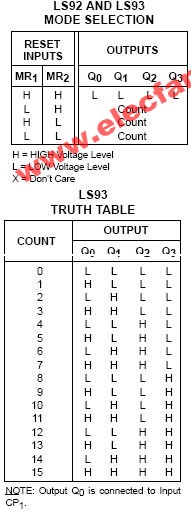

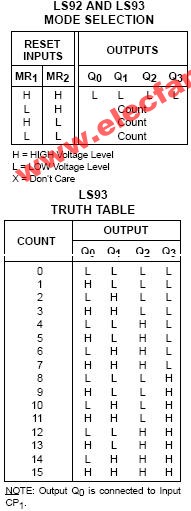

74ls93引脚图管脚图及功能真值表

74LS93 TRUTH TABLE

2008-12-01 15:42:17 1951

1951

74ls93引脚图管脚图及功能真值表

74LS93 TRUTH TABLE

2008-12-01 15:41:17 1924

1924

74ls93引脚图管脚图及功能真值表

74LS93 TRUTH TABLE

2008-12-01 15:40:48 20695

20695

74HC138真值表和管脚图

五. 实验步骤1.

2008-09-22 11:15:03 45105

45105

74ls14引脚图及管脚功能真值表

2008-06-08 08:55:15 35049

35049 74ls11引脚图

74ls11功能真值表:

2008-06-08 08:48:26 44703

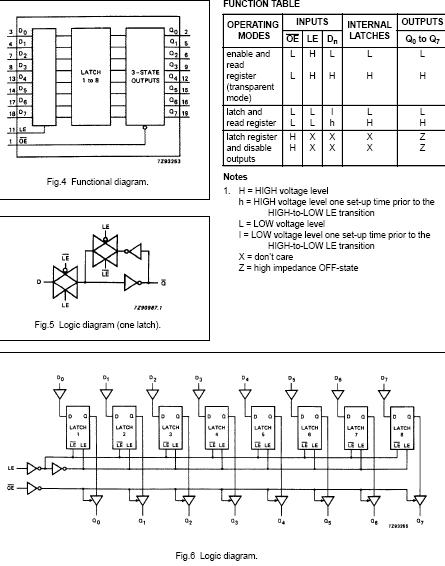

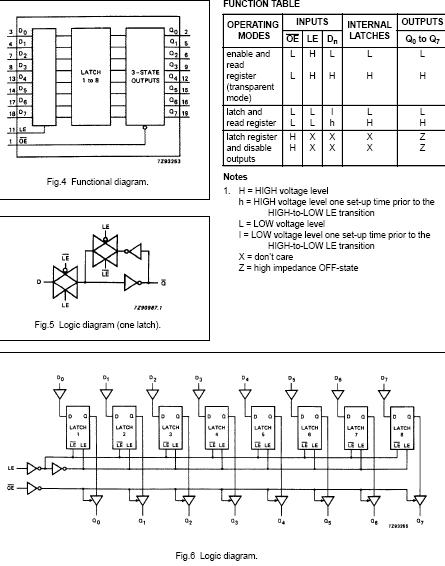

44703 74hc373引脚图

74hc373真值表和74HC373逻辑功能图

2008-04-07 23:52:18 23700

23700

CC4008中文资料:型由具有段间快速超前进位的4个全加器段组成。

2008-04-07 22:27:03 32

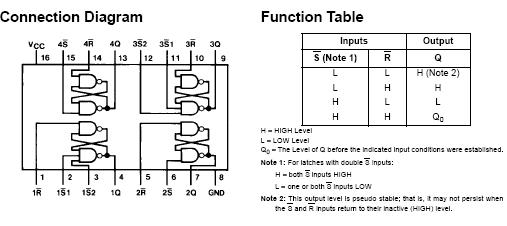

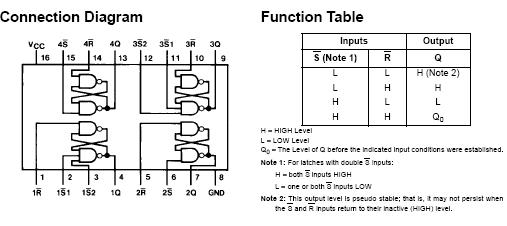

32 74ls279的引脚图及功能真值表

2008-03-06 14:11:05 90164

90164

7406的引脚功能及真值表

2008-02-28 17:35:37 19431

19431

74ls86管脚图和引脚图及真值表如下:

2007-12-17 23:00:21 52324

52324

74ls192真值表

只看真值表也不大方便,下面在提供一下其功能管脚图

2007-11-29 22:40:16 17788

17788

74ls151管脚图

真值表:

2007-11-29 22:29:41 87781

87781

D触发器真值表分析:

1. D 触发器真值表

Dn

2007-09-11 23:15:20 17600

17600

电子发烧友App

电子发烧友App

评论