全加器的定义

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

全加器逻辑图原理

两个多位二进制数相加时,除了最低位以外,其他每一位相加时都需要考虑低位的进位,即将加数、被加数和低位的进位3个数相加,这种加法运算称为全加运算,实现全加运算的电路叫做全加器。

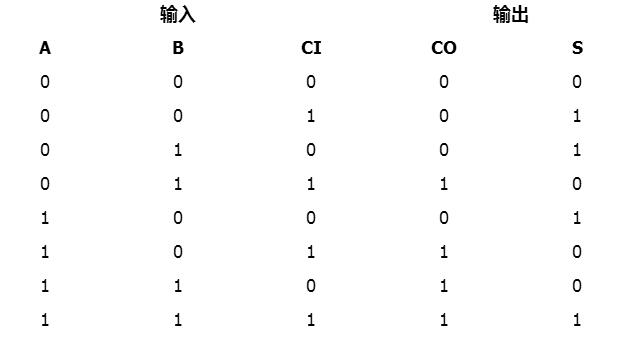

全加器的真值表如表1所示。A、B、CI分别为加数、被加数和低位的进位,S为本位和输出,CO为向相邻高位的进位输出。

表1 全加器真值表

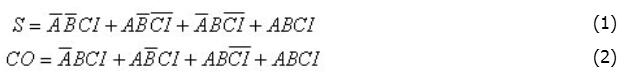

根据真值表写出输出逻辑函数式:

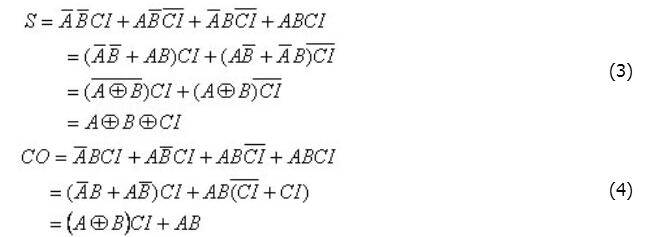

将函数式进行化简和转换

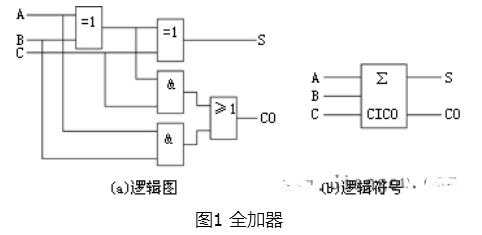

画出全加器的逻辑图,如图1所示。

全加器的输入端有几个

全加器的输入端有三个,分别为A、B、C(低位的进位);两个输出S(和);C(运算产生的进位)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

全加器

+关注

关注

10文章

62浏览量

29038

发布评论请先 登录

相关推荐

热点推荐

Verilog实现使用Booth编码和Wallace树的定点补码乘法器原理

莱士树中,对于16位乘法,其每位至少包含6个全加器。对于32位乘法,全加器个数则为14。这样子做可以保证对于首位,其有6/14个空闲的进位要求,这至少可满足n-2个末尾加法操作,剩下的两个一个用在C和S的加法器进位

发表于 10-23 08:01

数字电路—14、加法器

能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

能对两个1位二进制数进行相加并考虑低位来的位,即相当于3个1位二进制数相加,求得和及进位的逻辑电路称为全加器。

发表于 03-26 11:15

电源输入端浪涌电流的测试

在开关电源的测试过程中,输入端的浪涌电流是一项至关重要的检测指标。作为电能进入电源装置的首个关口,它直接关系到电源设计电路能否稳定运行。这一指标的重要性堪比示波器的带宽指标,对于确保电源产品的性能

ads1232没有输入端加信号,输出端有信号,有零点几MV的信号,怎么回事?

ads1232没有输入端加信号,输出端有信号,有零点几MV的信号,怎么回事?在显示屏上能看到

发表于 02-08 07:11

ADS1241输入负的信号,则会影响所有输入端,怎么解决?

在使用ADS1241时,使用的是8路模拟单端输入,如果输入全是正信号,使用正常,如果其中一端输入负的信号,则会影响所有

发表于 01-01 06:52

hdmi是什么电平?hdmi信号里有几对差分还有几个单端的,差分的信号是不是cml电平?

出来的cml信号在还原成hdmi信号,接到显示器上。现在有几个问题:

1,hdmi是什么电平?第一次接触,hdmi信号里有几对差分还有几个单端的,差分的信号是不是cml电平?

2,如果

发表于 12-24 06:34

差分输入和和单端输入在本质上到底有什么区别?

和和单端输入在本质 上到底有什么区别? 因为,ADC采集的信号说到底是AINP - AINN,不管单端还是差分,采集的信号都是这两个pad的差值。

2:将单

发表于 12-23 07:31

ADS1191模块输入端IN1P和ININ干扰信号特大是怎么回事?

最近在参考ads1x9xevm评估板,采用ADS1191设计便携式ECG,发现IN1P和INI两个输入端的有很强的50hz干扰信号,所以采集的数据看不到心电信息。后来通过配置MUX1测试几个

发表于 12-23 06:09

想用ADS5263做一个波形采集器,有几个疑问求解答

想用ADS5263做一个波形采集器,有几个疑问:

1.手册上介绍的模拟信号都是AC耦合,请问如何设计电路能做到直流耦合?

2.单端时钟输入和差分时钟

发表于 12-20 08:26

ADS8361输入不接的时候,输出端的时序竟然有波形出来,是哪里的问题?

我现在在使用这款ADS8361采集芯片,请问,当输入不接的时候,输出端的时序竟然有波形出来,有6万多,我感觉是不是芯片有问题?当没有

发表于 12-20 08:06

请问ADS9110输入可以采用单端输入?

是否可作为单端输入,还是必须得为全差分输入。

此外,有个疑问,一旦FPGA启动程序,通过ADS9110的数字接口读取采样值,在AIN前端的测到直流电平越1.8V,非VCM的值。

初次

发表于 12-18 07:00

ADS1248有8个输入引脚,手册说有7路单端输入指的的是哪7个腿?

如题,应该如何设置,有没有相关说明的文档?1248有8个输入引脚,手册说有7路单端输入指的的是哪7个腿?

发表于 12-09 07:56

全加器的定义_全加器的输入端有几个

全加器的定义_全加器的输入端有几个

评论