我们的实习生通过在自行车建设中回馈社区而拥有良好的业力。

了解UltraScale如何支持下一代Ultra系统。

了解在Xilinx工作的感受。员工提供有关我们的文化,工作环境和产生影响的机会的观点。

观看此视频,以优化和成熟的硬件参考设计的形式了解Xilinx电源传输策略的优势

为什么Zynq

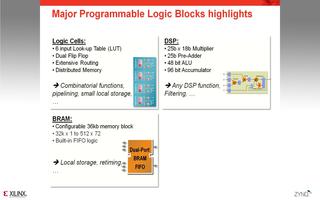

Zynq可编程逻辑亮点

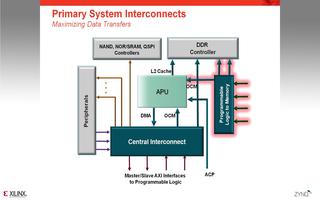

Zynq处理系统亮点

观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

演示运行x8 Gen3 PCI Express Link的Xilinx Kintex-7 FPGA ....

从Xilinx预览新的Kintex-7开发套件。

了解如何描述Spartan-6 FPGA中可用的基本片和I / O资源。

首次演示新型Xilinx 7系列GTH收发器,通过背板以13.1 Gb / s的速度运行。

被称之为“堆叠硅片互联技术”的3D封装方法采用无源芯片中介层、微凸块和硅通孔 (TSV)技术,实现了....

Xilinx合作伙伴和客户展示了他们如何使用Zynq仿真平台。

我们的实习生有真正的责任,并有机会通过跨职能和与同行互动来获得经验。

他们学得很快,受到挑战并且很....

观看世界上第一个可扩展处理平台--Zynq-7000 EPP的演示。

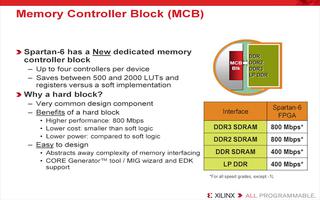

Spartan-6内存资源

系统监控工具演示

法兰克福的Xilinx开发者论坛将数百名开发人员和合作伙伴连接起来,以便进行学习和分享。

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

Xilinx高级副总裁Victor Peng讨论了业界首个All Programmable ASIC....

亚马逊的Gadi Hutt在硅谷举办的第一届年度Xilinx开发者论坛上发表了主题演讲。

Xilinx的Dave Tokic与Topic Embedded Systems的创始人兼首席执行官....

UltraFast嵌入式方法检查表介绍,解释清单的功能以及如何使用它。

ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS ....

DAVE嵌入式系统在嵌入式世界2015中展示了Matrix多重HLS IP和DAVE Bora套件

iVeia使用嵌入式世界2015中的iVeia视觉套件演示了Canny边缘检测HLS IP

了解新Vivado Lab Edition的功能和优点,并熟悉其安装和典型使用流程。

通过详细了解错误路径,最小/最大延迟和案例分析约束,了解不同类型的异常约束。

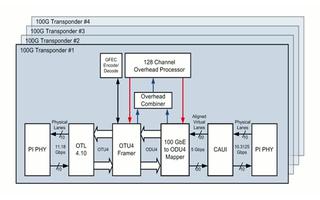

了解在VC730 OTN测试开发平台上运行的Xilinx 4x100G转发器参考设计。

(简明版....