【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用

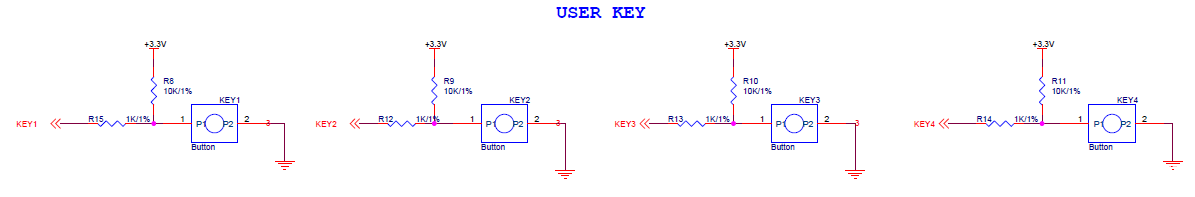

使用zynq最大的疑问就是如何把PS和PL结合起来使用,在其他的SOC芯片中一般都会有GPIO,本实....

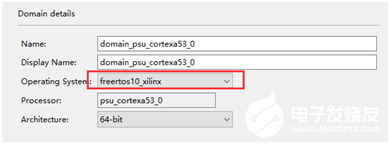

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十一章FreeRTOS实验

如何搭建Free RTOS实时操作系统运行环境,这里不深入探讨Free RTOS的具体使用。本实验以....

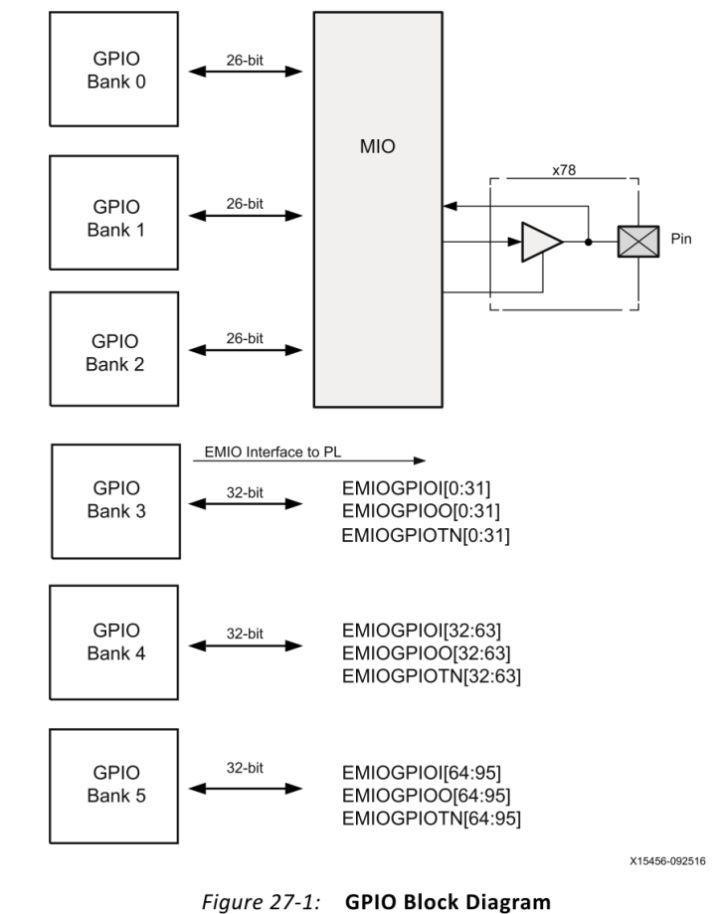

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十八章PS端EMIO的使用

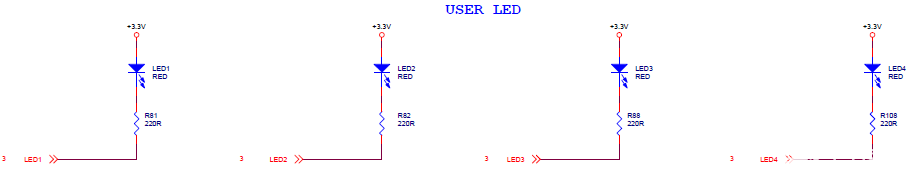

如果想用PS点亮PL的LED灯,该如何做呢?一是可以通过EMIO控制PL端LED灯,二是通过AXI ....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL读写PS端DDR数据

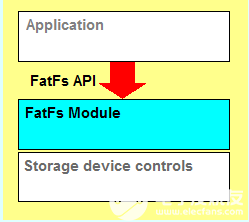

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十七章System Monitor

本章介绍system monitors的使用,用于监测芯片的电压、温度值等,也可以通过PL端的ADC....

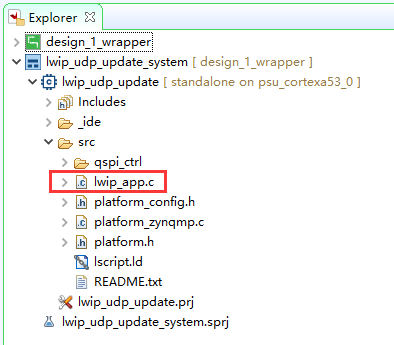

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十六章PS端网络远程更新QSPI

在实际工作中,会遇到产品升级问题,如果按照程序烧录的方式,可能需要打开产品的外壳,这无疑。本章介绍一....

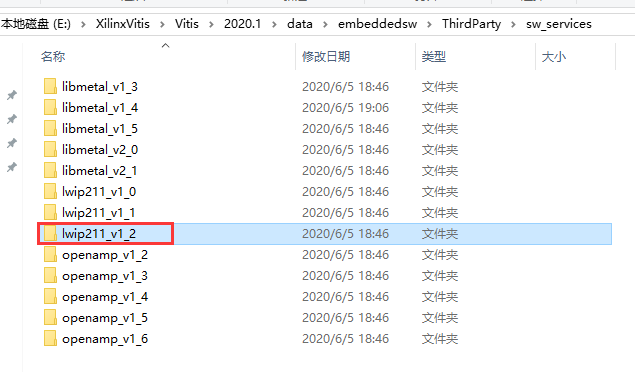

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十五章PS端以太网使用之lwip

开发板有两路千兆以太网,通过RGMII接口连接,本实验演示如何使用Vitis自带的LWIP模板进行P....

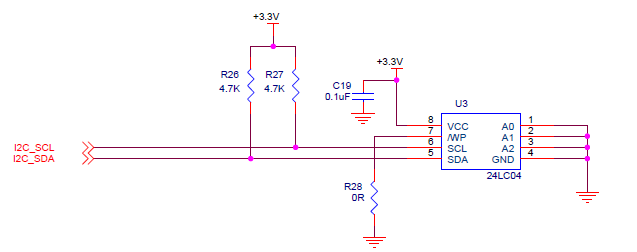

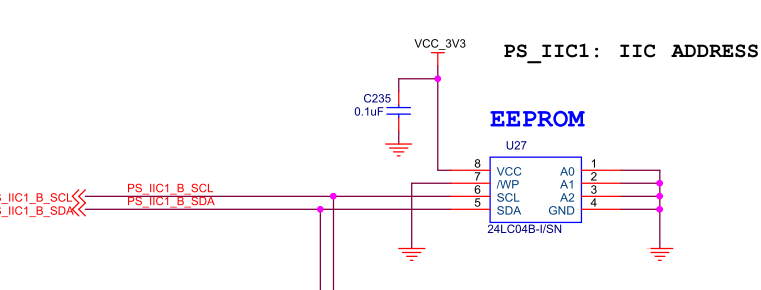

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十二章PS端I2C的使用

ReadBuffer清0,WriteBuffer赋FF写16个字节到EEPROM读EEPROM的16....

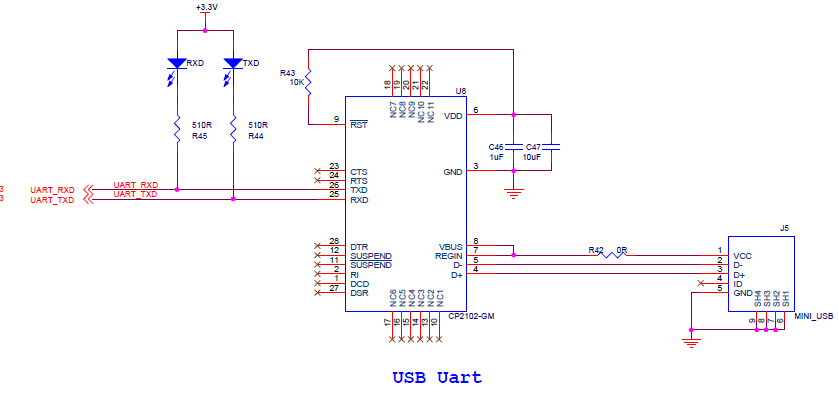

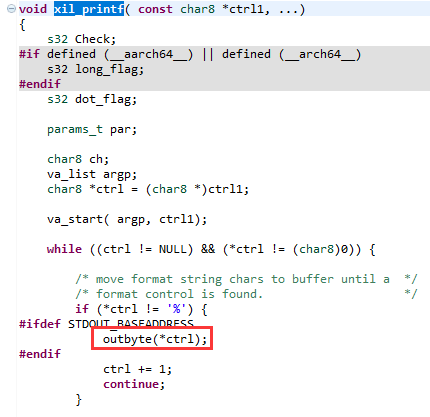

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART读写控制

除了打印信息之外,如果我们想用UART进行数据传输呢?本章便来介绍PS端UART的读写控制,实验中,....

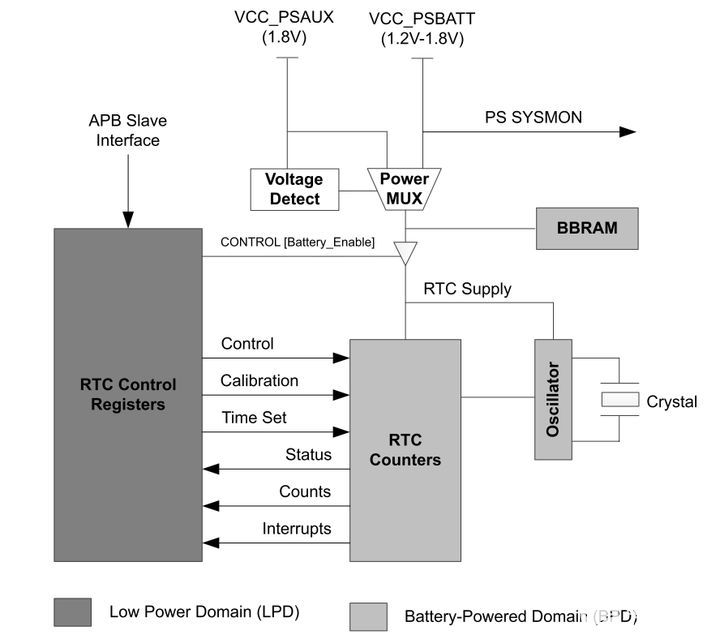

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十章PS端RTC中断实验

实验中通过简单的修改Vitis的例程,就完成了RTC,中断的应用,看似简单的操作,但蕴含了丰富的知识....

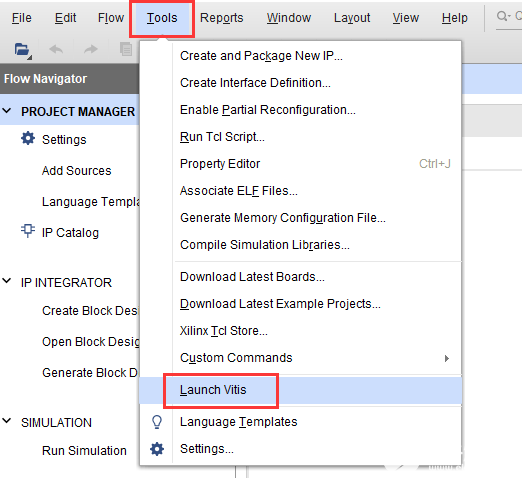

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十九章 Hello World(下)

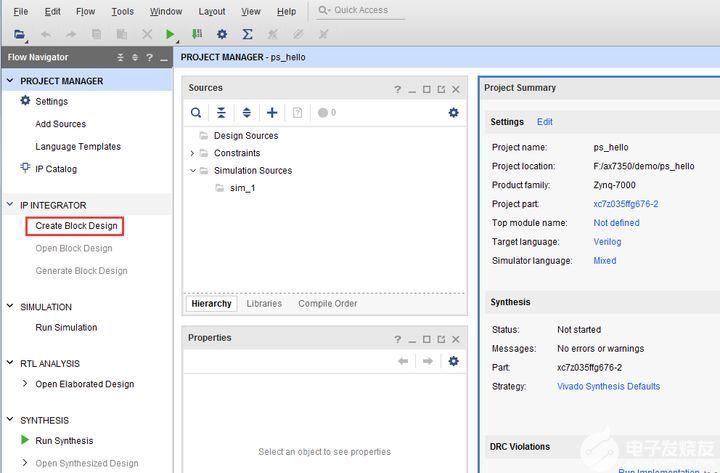

本章从FPGA工程师和软件工程师两者角度出发,介绍了ZYNQ开发的经典流程,FPGA工程师的主要工作....

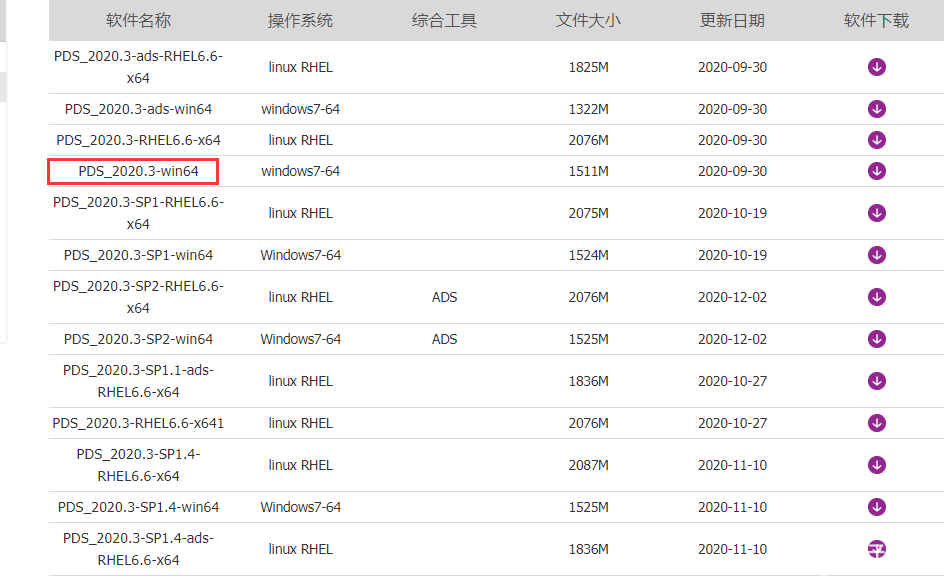

【紫光同创国产FPGA教程 第一章】Pango Design Suite 2020.3安装

ango Design Suite是深圳市紫光同创电子有限公司的FPGA开发软件,截止到目前,软件的....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章 Hello World(上)

我们从原理图中可以看到ZYNQ芯片分为PL和PS,PS端的IO分配相对是固定的,不能任意分配,而且不....

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章Vitis准备工程及注意事项

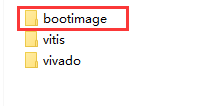

所有的工程目录下都有个bootimage文件夹,存放了对应的BOOT.bin文件,可将此文件拷贝到V....

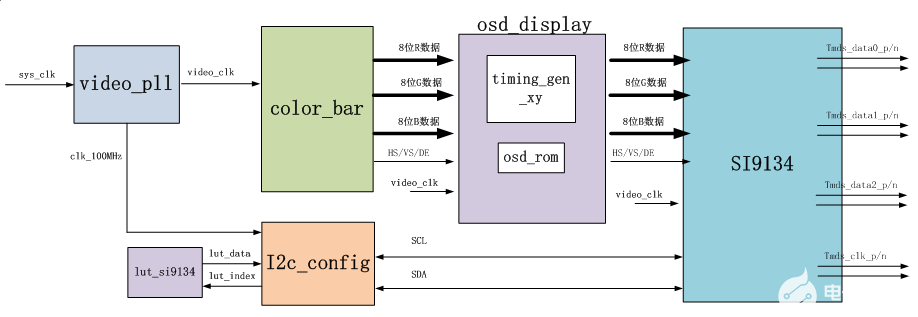

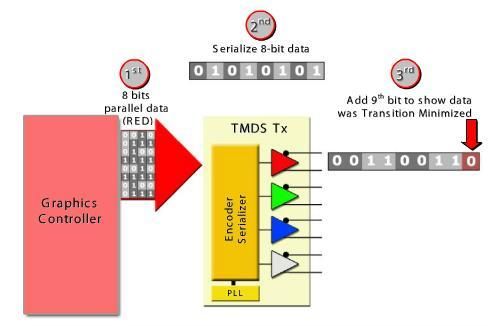

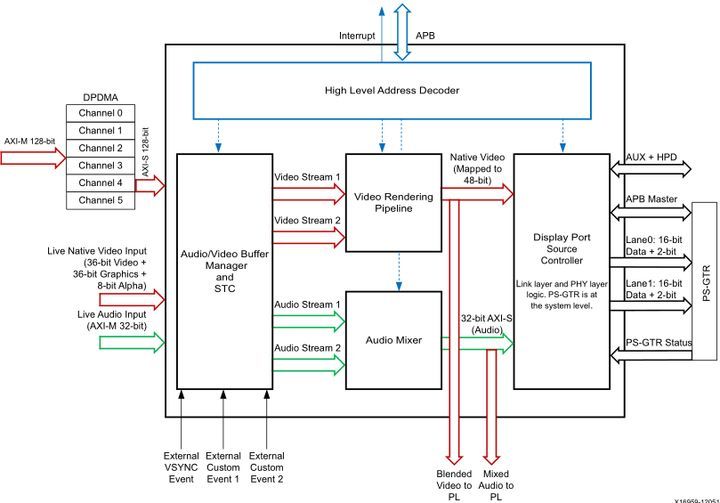

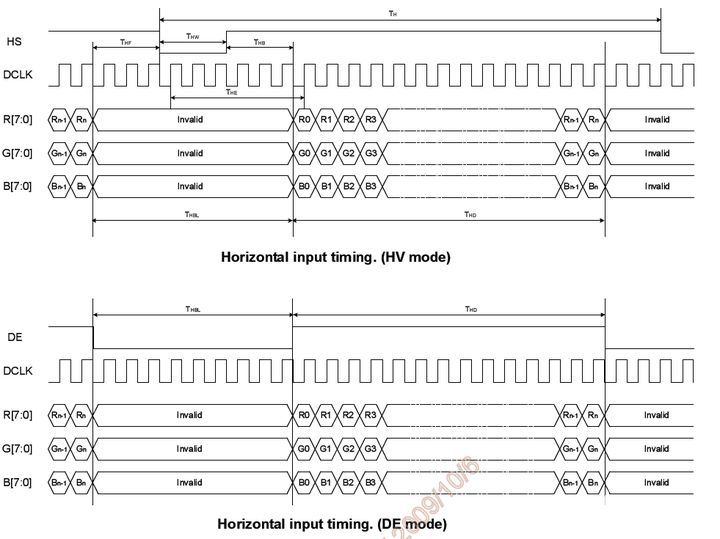

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十五章HDMI字符显示实验

在HDMI输出实验中讲解了HDMI显示原理和显示方式,本实验介绍如何使用FPGA实现字符显示,通过这....