自赛灵思推出Zynq-7000 All Programmable SoC之后已经催生出众多产品。Zynq SoC现在已经成为全球众多最具创新性的最新产品的核心,如:汽车、医疗与安全监控产品、以及使工厂变得更安全、更环保和更高效的先进电机控制系统。另外,Zynq SoC也在新一代有线和无线通信基础设施设备以及众多新兴物联网应用中赢得一席之地。

Zynq SoC在单芯片上完美集成了双核ARM Cortex-A9 MPCore 处理器、可编程逻辑和关键外设,这不仅让客户亲自体验到了所带来的无与伦比的多功能性,而且越来越的客户将该器件的用途从作为单个插口的首选处理器扩展到成为整个产品系列的首选平台。通过实施充分发挥Zynq SoC和软硬重用优势的平台战略,客户能够快速打造其产品的众多衍生品或变体。因此最终能够提高设计生产力和盈利性。

现在让我们看一下平台电子产品巨头公司采取哪些措施来提高其盈利能力;Zynq SoC为何远优于ASIC、单独的ASSP甚至是ASSP+FPGA双芯片平台实现方案;以及您如何顺利利用Zynq SoC迅速提高自己公司的盈利能力。

在许多人眼中“平台”已成为营销方面的陈词滥调。但是,电子行业诸如苹果、英特尔和思科等众多公司已经通过有效实施平台业务战略一举成为高盈利电子产品领导者。在实施平台战略过程中,公司需要大量前期投入用于创建和编制专为其电子产品平台初始版本设计的模块。他们然后把这些设计模块转变成IP模块,经过重新利用快速、轻松将这些模块扩展为衍生产品系列、模型以及新一代产品,从而能够更快、更轻松地以更低设计成本和更少资源推出衍生产品。

获得盈利能力所面临的挑战

研究公司国际商业战略(IRS)在其2013年报告《系统IC业务成功要素》中总结到:采用从28nm到20nm、16nm和10nm不断提高的工艺节点技术生产ASIC或ASSP器件,成本会不断增加,那些生产其自有芯片的公司需要更加努力才能实现传统的最终产品收入目标:即收入超过其最初研发投入的10倍。许多公司竭尽全力通过在各个节点打造多种衍生产品来实现10倍目标。

“衍生设计成本会达到初始设计成本的20%,也就是说,如果某项新产品系列的决策需要非常高的开发成本,则可以用低得多的成本实现衍生设计。为了最大化收入和利润,公司所具有的优势是在一个技术节点实现多种[衍生]设计,”该报告指出。“在一个技术节点仅实现一两个设计会造成极高的前期成本而且要获得良好财务回报还会带来高风险。”

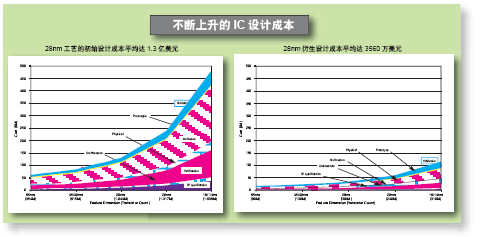

图1 – IC的初始开发成本随引入各种新的芯片工艺技术而提高。相比之下,在相同节点开发后续衍生产品的成本要低得多,因此实现10倍于设计成本的最终产品收入目标要容易得多。平台设计让公司能够快速开发衍生设计并提高盈利性。

“能够降低新产品实现成本的新设计概念有望给半导体行业结构带来巨大变化,”该报告随后指出。“但是,在新的设计方法出现之前,由于特征尺寸降低,半导体公司需要根据半导体行业不断变化的财务指标调整其商业模式。”[资料来源:国际商业战略公司(IBS)(2013/2014年)]

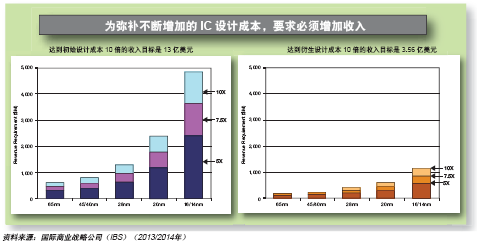

IBS在研究中指出28nm ASIC或ASSP的设计成本(首批或初始产品)高达2.3亿美元(图1)。而衍生设计成本要低得多:仅有3,560万美元。因此,为了同时实现两类器件的10倍收入目标,复杂器件需要13亿美元投资,而衍生产品只需3.56亿美元 [资料来源:国际商业战略公司(IBS)(2013/2014)]。

IBS研究表明,公司需要650个工程年度才能设计出复杂的28nm ASIC。相比而言,28nm衍生ASIC设计的开发时间只需169个工程年度,前者是后者的3.8倍。

假设ASIC团队的新设计开发符合摩尔定律并且开发周期为2年,则需要用325名工程师花费两年时间完成复杂的28nm ASIC。但是,只需要85名工程师就能够在两年内完成28nm ASIC的衍生品开发。

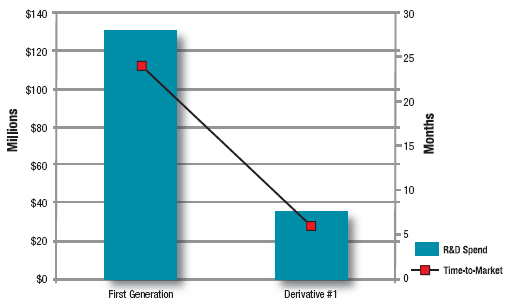

而如果公司也用全部325名工程师开发衍生设计,则他们只需6个月就能完成任务(图2)。

图2 – 衍生设计可以减少上市时间、开发时间和成本,同时使更易于达到盈利能力目标。

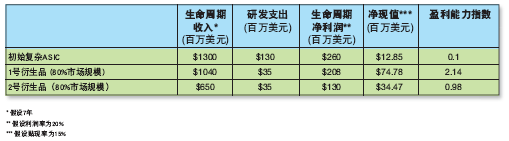

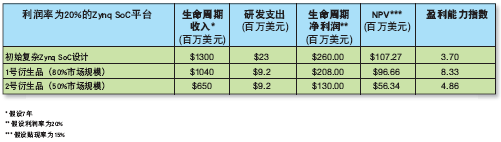

另外,如表1所示,如果假定初始的复杂设计采用325名工程师达到13亿美元的10倍收入回报目标,则目标市场只需达到初始ASIC市场收入规模80%(10.4亿美元)的衍生设计只需85名工程师在两年内就能够开发出净现值(NPV)远远超过初始ASIC设计NPV的产品。(NPV 定义是现金流入与流出现值差额。此概念在资本预算中用于分析某项投资或某个项目的盈利能力。)

表1 – 开发衍生设计具有可观的净现值(NPV)和更加出色的盈利性指数。

此外,衍生设计比初始ASIC具有更高得多的“盈利能力指数”(PI)(NPV除以研发支出)。即使衍生产品仅达到初始设计市场规模的一半(6.5亿美元),其也具有优于初始ASIC的NPV,而PI基本相同。

平台:实现盈利衍生品的最佳战略

面对不断增加的研发成本、日渐激烈的竞争以及消费者对更好产品日益苛刻的需求,越来越多的半导体公司和电子产品系统公司开始转向寻求平台战略来快速创建衍生产品并最大限度提高盈利性。平台战略能够进一步降低产品开发时间、加速上市进程并节省工程时间成本,同时能够提高各种衍生产品或新一代产品的盈利性。

正如IBS研究所显示,企业通过开发衍生设计“优化收入和利润”。而采用平台方法在相同节点开发多种衍生产品(也就是说,衍生产品的衍生产品)使企业能够进一步优化收入与利润,因为各个后续设计都能受益于在之前设计中学到的经验教训、重新利用以及对客户需求更准确的了解。

处理选择是平台成功的关键

企业在实施平台战略时做出的两项最重要的业务决策实际上是关键技术决策:众多处理系统中哪一个会成为产品平台的核心?该处理系统的哪种芯片实施方案最适合提高盈利性?

在平台战略中,处理系统必须满足或者超过应用软件和系统需求。它必须具备可扩展性并且易于扩展;必须具有不断增长的大型成熟生态系统;而且必须允许设计人员和工程师利用之前的设计成果。最后,它必须来自具有发展规划且成熟稳定的供应商,而且该供应商并未持有偏离其发展规划或者不断推出无尽勘误的不良记录。虽然有一些候选产品符合上述某些要求,但是能够满足或超过全部上述要求的系统是ARM微处理器架构。

ARM已经成为PC之外一切设备的事实标准嵌入式架构。如今采用高级嵌入式处理技术的绝大部分电子系统——从手机、汽车到医疗设备——都采用ARM处理器内核。尤其是ARM的Cortex-A9处理器架构成为许多种片上系统(SoC)的核心。其不仅已用于专门针对前言智能手机、平板电脑等高量产增值产品开发的ASIC设计中,而且还用于众多ASSP设计,该设计主要针对那些希望进军由于缺乏功能差异化而主要展开价格竞争的中小规模成熟市场的公司而开发。

为了增强产品差异化,许多企业基于ARM处理系统创建了将FPGA与现成ASSP融为一体的产品平台。他们可以在这种配置中实现硬件与软件细分,从而创造更广泛的特性组合或者灵活、可升级、性能更高的终端产品——其可帮助他们战胜那些提供仿效式仅可软件编程的ASSP实施方案的竞争对手。在这些ASSP中添加赛灵思FPGA已经帮助众多企业的产品在市场中脱颖而出。

理想平台解决方案:ZYNQ SoC

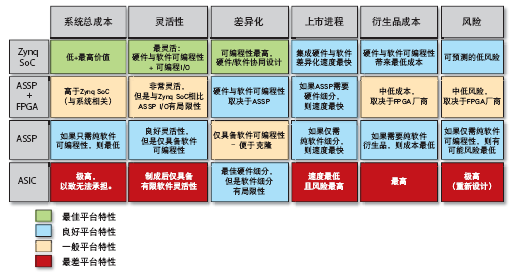

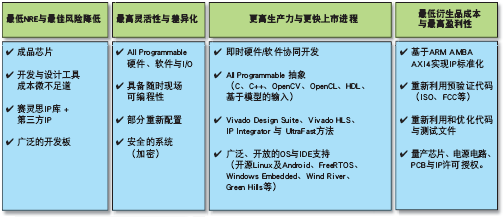

借助Zynq-7000 All Programmable SoC,赛灵思正在实施适合绝大部分嵌入式应用的高稳健性ARM Cortex- A9平台解决方案。如表2所示,作为一种芯片平台,Zynq SoC具备超过ASIC、ASSP以及ASSP+FPGA组合的众多优势。与ARM处理系统的其他硬件实施方案相比,Zynq SoC不仅在NRE、灵活性、差异化、生产力/上市进程等方面具有最佳特性组合,而且还具有最低衍生品成本和最低整体风险(表3)。

表2 - Zynq-7000 All Programmable SoC可为寻求实施平台战略的客户提供理想的特性组合。

表3 – 低NRE费用、灵活性等要素使Zynq SoC成为平台战略的理想选择。

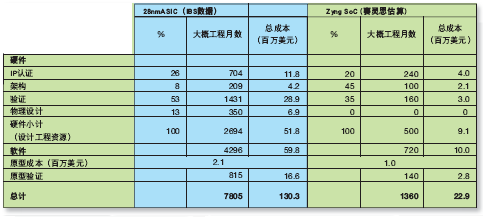

另外,Zynq-SoC与其他平台实施方案相比具有巨大的成本优势。让我们来看一下具体数据。

赛灵思 All Programmable SoC产品营销与管理总监Barrie Mullins表示,设计28nmASIC的平均成本是1.3亿美元,而ASIC设计项目的10倍收入目标则为13亿美元。他指出,但是,基于Zynq SoC的典型设计项目本质上其整体设计成本比ASIC实施方案低得多而且上市进程也比其快。其原因是Zynq SoC能够提供预设计、特征化、业经测试与验证的成品SoC,其可以带来软件、硬件、I/O性能以及差异化灵活性。此外,Zynq SoC还受益于低成本且高度集成的赛灵思硬件与软件设计工具,而ASIC工具流程不但复杂,而且具有严重的互操作性及兼容性问题,同时还需要支付高达数百万的许可费用。设计人员采用赛灵思推荐的UltraFast方法时赛灵思的设计流程会尤为优化。Mullins补充到,由于赛灵思生态系统IP已经完成设计和预验证并且赛灵思工具可以生成中间件,因此IP认证成本较低。

Mullins指出,因此典型Zynq SoC项目需要2300万美元。由此实现设计项目的标准10倍收入目标需要生命周期收入达到2.3亿美元——此10倍目标比实现ASIC实施方案所需达到的13亿美元10倍目标更易于实现,而且也更可行(表4)。

表4 – Zynq SoC项目成本远低于同等ASIC项目。

采用的上述方法分析IBS数据时,如果我们假设在Zynq SoC 中实现的初始复杂设计能够完全占领同样的13亿美元目标市场,则利用57名工程师只需要2300万美元就能够在两年内完成产品。

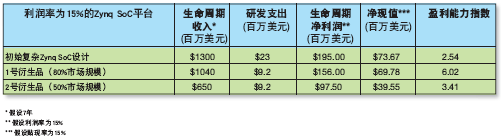

如果假设初始Zynq SoC设计具有与初始ASIC设计相同的20%利润率,则初始Zynq SoC设计的NPV为1.0727亿美元,而PI为3.7,其明显优于初始ASIC的1285万美元NPV和仅有0.1的PI。利润率同样为20%的Zynq SoC的NPV与PI更加可观(表5)。

表5 – NPV与盈利能力指数表明Zynq SoC远远优于ASIC平台。

对比利润率同样为20%的Zynq SoC平台衍生品和能够获得初始设计市场80%的ASIC平台衍生品发现:Zynq SoC平台的NPV达到9,666万美元,PI为8.33;而ASIC衍生品的NPV为7,478万美元,PI仅为2.14。同样,能够获得初始Zynq SoC设计目标市场50%的衍生品的NPV可达到5,634万美元,PI为4.86,远优于ASIC平台衍生品。

即使让ASIC平台利润率保持20%不变,而把其结果与利润率较低的 –比如说15% - Zynq SoC对比(Zynq SoC单位成本可能更高),Zynq SoC仍然是优异得多的盈利能力最大化方案。利润率为15%的初始Zynq SoC设计的NPV达到7367万美元,PI为2.45。这比初始ASIC的1,285万美元NPV和低至0.1的PI相比也是巨大改进,尽管ASIC利润率设定为20%。

对于目标市场是初始Zynq SoC目标市场的80%(10.4亿美元)的Zynq SoC平台设计,其需要23名工程师用两年时间开发出基于Zynq SoC的衍生产品。最后产品的NPV能够达到6978万美元,PI达到6.02。其稍低于ASIC衍生品7478万美元的NPV。但是,利润率为15%的Zynq SoC 衍生品的PI远优于ASIC衍生品仅有2.14的PI,尽管ASIC的利润率更高(20%)。

此外,目标市场是初始Zynq SoC设计目标市场的50%的Zynq SoC衍生设计可以实现3955万美元的NPV并且IP可达到3.41。其不但优于ASIC衍生品仅为0.98的PI,而且也优于初始Zynq SoC的PI。

值得注意的是,尽管利润率随给定市场的需求量变化,但是数据表明Zynq SoC即使对于大规模应用也是理想的平台选择。即使把利润率更高(20%)的ASIC平台与利润率更低(15%)的Zynq SoC平台对比, Zynq SoC在财务和技术方面也是出色得多的平台解决方案。对于小规模应用,毫无疑问Zynq SoC平台更是最大化盈利能力的最佳平台选择。

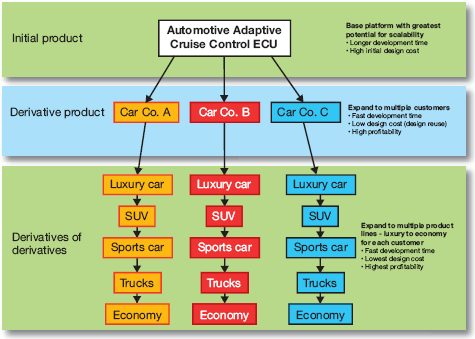

图3 – 通过采用Zynq SoC平台为多家汽车制造商和各个制造商的多个产品系列与型号提供服务,赛灵思客户已经最优化其初始设计投资,从而提高了盈利能力。

ZYNQ SOC确保平台成功

目前,众多应用领域的众多客户通过把Zynq SoC用作其平台战略的核心以显著提高其规模经济。专为汽车行业生产高级电子控制单元(ECU)的全球知名制造商就是一个很好的例子。该客户正在把Zynq SoC用作平台解决方案进行标准化。

借助Zynq SoC,同时充分发挥紧密集成的软硬件IP的重利用优势,该公司已经打造出了高度灵活的ECU平台,其能够根据多家汽车制造商的特殊需求及其不同产品系列、型号/配置与零配件包完成快速定制(图3)。利用Zynq SoC作为中心平台,该公司实现了规模经济最大化,降低了预算,同时向日益增多的客户交付更多产品,最终能够更快地向客户提供定制ECU。

Zynq-7000 All Programmable SoC是针对大多数嵌入式应用实施平台战略的最佳器件。凭借ARM处理与FPGA逻辑之间无与伦比的高集成度以及I/O可编程性,Zynq SoC使企业各级能够协调其开发工作,同时以比竞争对手更快的速度向市场推出高度差异化的产品系列。Zynq SoC平台使这些客户能够迅速提高其盈利能力。

---> END <---

-

利润率

+关注

关注

0文章

3浏览量

6282 -

生产

+关注

关注

0文章

123浏览量

14360 -

成本

+关注

关注

0文章

32浏览量

18433

发布评论请先 登录

赛灵思(Xilinx)将展示Zynq-7000 All Programmable SoC工业自动化解决方案

赛灵思Zynq-7000 All Programmable SoC获年度最具潜力新技术奖提名

赛灵思7系列采用FPGA电源模块

赛灵思Zynq-7000可扩展处理平台让编程流程更简单

赛灵思Zynq-7000 All Programmable SoC实现1GHz处理能力

赛灵思推出多款全新All Programmable解决方案

赛灵思All Programmable器件:ADAS及后续升级的事实标准平台

赛灵思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序教程

比亚迪采用基于赛灵思 Zynq SoC L0/L1 前置摄像头的ADAS 方案

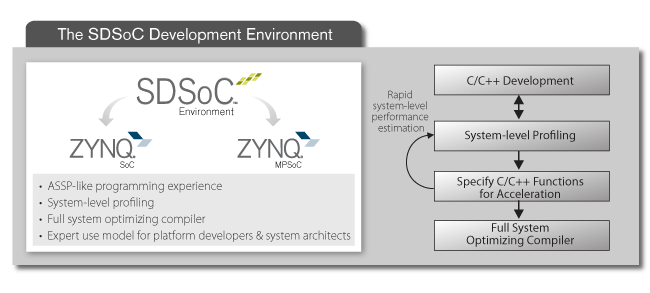

赛灵思将Zynq SoC用户扩展至广大的系统和软件工程师社群

Zynq SoC 给赛灵思带来的收益

Zynq SoC 给赛灵思带来的收益

评论