UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART用于主机与辅助设备通信,如汽车音响与外接AP之间的通信,与PC机通信包括与监控调试器和其它器件,如EEPROM通信。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639148 -

寄存器

+关注

关注

31文章

5619浏览量

130409 -

uart

+关注

关注

22文章

1319浏览量

106968

发布评论请先 登录

相关推荐

热点推荐

FPGA的IP软核使用技巧

,可以尝试对IP软核进行优化。例如,可以调整参数配置、优化布局布线、修改代码等。

在调试过程中,可以利用FPGA开发工具提供的调试功能,如逻辑分析仪、波形查看

发表于 05-27 16:13

FPGA实战演练逻辑篇42:寄存器电路的设计方式

寄存器电路的设计方式本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 上一章节中也已经基本介绍

发表于 06-26 11:53

FPGA实战演练逻辑篇55:VGA驱动接口时序设计之2源同步接口

VGA驱动接口时序设计之2源同步接口本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 好,有了

发表于 07-29 11:19

UART寄存器介绍与中断操作详解

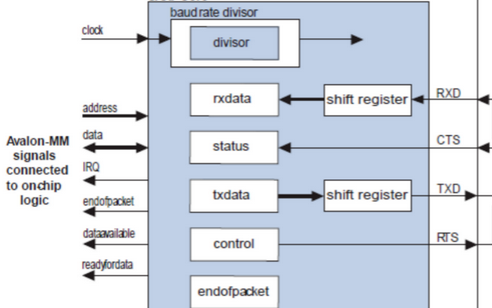

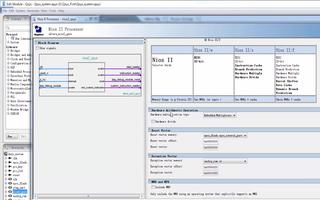

简介 UART核提供了一个Avalon存储器映射(Avalon-MM)的接口,这个接口使得Avalon-MM的主要周边设备(例如Nios II处理器)通过读和写数据、控制

FPGA之软核演练篇:UART的寄存器描述、配置选项与应用实例

FPGA之软核演练篇:UART的寄存器描述、配置选项与应用实例

评论