集成电路制造需要某种隔离工艺将单个器件隔离开来。因为半导体集成电路是在同一块半导体硅片上,通过平面工艺技术制造许多元件和器件(如电阻、电容、二极管、三极管等),并按需要将它们连接在一起,形成具有一定功能的电路。这些元件和器件所处的电位不同,相互之间必须绝缘隔离,否则半导体本身的电导将这些元件相互连通,就不可能在一个单晶片上制作集成电路。为此,必须设法使它们在电性能方面隔离开来,这就是隔离工艺所要达到的目的。衡量隔离工艺模块的指标有:密度、工艺复杂度、成品率、平坦化程度和寄生效应。在这些指标间存在着折中。常用的器件隔离方法有PN结隔离、LOCOS隔离、沟槽隔离[1]。

PN结隔离

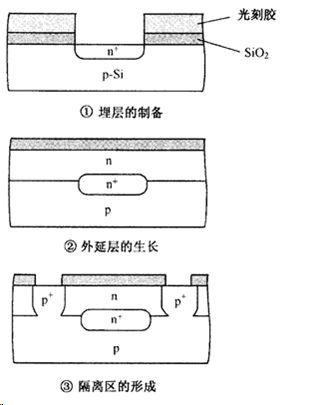

pn结隔离是集成电路生产中比较常用的方法,特别是在一些无特殊要求的小规模集成电路中。它是利用pn结反向偏置时呈高电阻性,来达到各元件互相绝缘隔离的目的。实现隔离有多种方法,但用得最多的还是一次外延、二次扩散pn结隔离工艺,简称标准pn结隔离或pn结隔离[2]。

为了实现pn结隔离,衬底材料必须选用p型单晶,以便和n型外延层之间形成pn结。这一pn结击穿电压的大小主要取决于衬底电阻率的高低。从提高击穿电压和减小隔离结寄生电容考虑,衬底的电阻率高一点好。但选得过高,在长时间的隔离扩散中,会增加外延层向衬底的推移,使隔离时间加长。同时高阻的单晶较贵,因此电阻率不能取得太高,在一般电路中为8到13欧姆厘米。为了得到平坦均匀的扩散结面,还应选用<111>晶向的硅单晶。厚度一般为300到350微米,应选用位错密度较低(一般应小于3000个/平方厘米),有害杂质少的硅单晶片[1]。

图1 PN结隔离工艺

LOCOS隔离

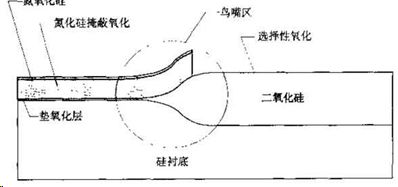

传统的硅局部氧化(Local Oxidation of Sillicon, LOCOS)隔离技术是利用光刻刻蚀技术在硅基板上的氮化硅上开出氧化窗口,利用氮化硅的掩模作用在大约1000摄氏度的高温下对没有氮化硅覆盖的场区进行氧化。氧化后氧化层表面将高出硅基板表面,高度大约是氧化膜厚度的55%,形成一定程度的不平坦表面,给后续工艺带来不利影响。再者,氧化生长时,横向的氧化生长将向器件的有源区延伸,形成所谓的“鸟嘴”现象。“鸟嘴”的出现,不但占据了一定的有源区面积,而且在极小尺寸下,使得漏电流问题越来越突出,极大地影响到器件的性能[3]。

沟槽隔离

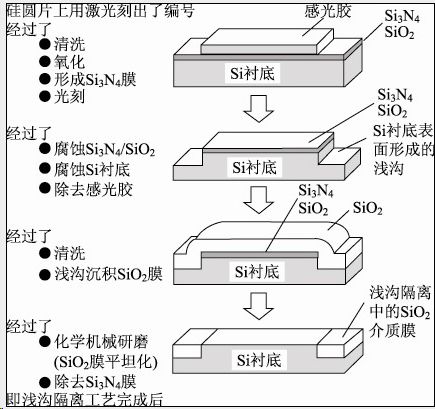

沟槽(Shallow Trench Isolation, STI)隔离技术起源于80年代,由于它的高成本和工艺的不成熟性,直到最近一两年才被人们所接受。该工艺是一种完全平坦的、完全无“鸟嘴”现象的新型隔离技术。其工艺流程如图所示,隔离技术完全回避了高温工艺;严格保证器件有源区的面积;硅基板表面与隔离介质表面完全在同一平面上;改善了最小隔离间隔和结电容。同时,低温工艺也可以潜在地增加产量,降低成本。这些优点使得STI隔离成为深亚微米时代器件不可或缺的隔离技术。STI隔离主要适应极小尺寸器件对极小特征尺寸、器件可靠性的要求。在极小尺寸下,要求场区和有源区的面积非常小;同时,对器件的漏电流也极为敏感。STI隔离工艺主要有以下各关键工艺:氧化和氮化硅生长、沟壑光刻刻蚀、HDP High Density Plasma,高密度等离子体)二氧化硅生长、二氧化硅CMP Chemical Mechanical Planarization)、氮化硅去除等工艺步骤[3]。

图3沟槽隔离工艺步骤

-

集成电路

+关注

关注

5464文章

12685浏览量

375694 -

半导体

+关注

关注

339文章

31236浏览量

266490

原文标题:集成电路的器件隔离(Device Isolation)

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

中国集成电路大全 接口集成电路

集成电路的检测常识

双极型集成电路的特点有哪些?

什么是集成电路

薄膜集成电路--薄膜电阻

电子元器件与集成电路测量

10.1.1 栅极全环绕器件∈《集成电路产业全书》

集成电路的器件隔离 Device Isolation

集成电路的器件隔离 Device Isolation

评论