NVMe,可以说是是全闪存阵列的下一个进程,它可让闪存释放更高的性能。使用NVMe,全闪存阵列可以提供数十万甚至数百万的IOPS,实现微秒级的响应。

但NVMe及其“搭档”——NVMe over Fabrics(NVMe-oF)都是较新的技术且相对不成熟,NVMe性能改进取决于所选的全闪存阵列架构。传统的全闪存阵列通过提供NVMe只能带来将近20%的性能提升,但新兴的全闪存阵列提供商的一些NVMe产品预计可提供的性能可以达到当前技术所能提供的10倍或更多倍。

20%的性能提升虽不高,但风险低

在2018年底,支持NVMe的企业级全闪存阵列数量仍然只占整个存储市场的一小部分。研究公司DCIG在2018年评估了超过100个全闪存阵列,其中不到20%支持采用NVMe接口的SSD。

NVMe支持在全闪存阵列市场中仍处于初期阶段,因为使用NVMe存储阵列的应用程序智能获得相对较小的性能提升。传统的全闪存阵列使用两个或更多控制器连接到后端使用NVMe的SSD。然后,控制器将这些SSD聚合、管理并以存储卷的形式呈现给网络连接主机。

使用在后端支持NVMe SSD的全闪存阵列,与使用SATA或SAS SSD的全闪存阵列相比,可以将应用程序性能提高20%。主机仍然通过标准光纤通道(FC)或以太网连接到这些支持NVMe的全闪存阵列。这种方法使企业可以轻松获得NVMe SSD带来的性能优势,同时将环境风险降至最低。

20%的性能提升效果确实不错,但NVMe SSD全闪存阵列理论上可以提供更大的性能提升——比使用SAS和SATA SSD的全闪存阵列多10倍。

这种巨大的性能差异源于这样一个事实,即现有的全闪存阵列控制器架构无法释放NVMe SSD提供的全部性能优势。阵列控制器的一个最初目标是加速HDD的性能,而在使用NVMe SSD时,这种控制器会成为一种阻碍。为了更好地释放NVMe SSD的性能,阵列控制器以及存储网络协议必须不断发展。

All In!——NVMe

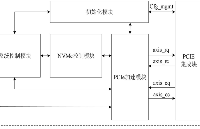

为了获得NVMe SSD在全闪存阵列中提供的高性能提升,企业必须使用那些可提供端到端NVMe连接的产品。此类全闪存阵列提供前端NVMe-oF,通过FC和以太网网络连接到主机,并为NVMe SSD提供后端连接。此设计使主机可以使用本机NVMe协议直接与NVMe SSD通信,并借助全闪存阵列控制器发送本机NVMe命令通过以太网和FC存储网络。

使用这种方法,有些全闪存阵列提供商报告说,理论上应用程序可以实现低于200微秒的延迟,超过100 GB的吞吐量和数千万的IOPS。使用机器学习,预测分析和视频处理的企业可能会需要这种级别的性能。

但要明白,这种方法可能存在风险和一定的局限。必要时,公司还必须限制其环境中NVMe部署的广度。用于操作系统的NVMe-oF驱动程序,仅适用于最新版本的Linux,例如Red Hat Enterprise Linux 7.4或更高版本,也可能来自全闪存阵列提供商。更值得注意的是,主要的操作系统提供商(如Microsoft和VMware)尚未提供NVMe-oF驱动程序。

可组合基础架构

通过使用NVMe SSD全闪存阵列或端到端NVMe的方法提高性能,企业可以获得比较明显的优势。不过一两年后,大多数企业会发现,他们能够获得相对更高的灵活性、性能和价值。很快供应商将提供一种新的全闪存阵列架构,将全闪存阵列控制器与后端NVMe SSD分离,以创建可组合的基础架构。

使用此架构,应用程序可以在全闪存阵列的数据管理功能及其性能之间进行选择。如果应用程序需要NVMe SSD带来更高的性能提升,同时也需要阵列控制器中的数据管理功能,例如LUN管理、快照和复制等等,可以通过阵列控制器访问NVMe SSD并获得数据管理和性能方面的提升。

但是,如果应用程序需要更高的性能提升,可以绕过阵列控制器并通过NVMe-oF直接访问阵列中的NVMe SSD。

-

全闪存阵列

+关注

关注

0文章

11浏览量

8081 -

nvme

+关注

关注

0文章

301浏览量

23919

原文标题:NVMe能否发挥更大价值,取决于全闪存阵列的架构

文章出处:【微信号:D1Net11,微信公众号:存储D1net】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高性能网络存储设计:NVMe-oF IP的实现探讨

NVMe over Fabrics 国产 IP:高性能网络存储解决方案

Neway微波产品:技术领航,创造卓越价值

戴尔科技全闪存存储PowerStore有何独特之处

NVMe高速传输之摆脱XDMA设计37:队列管理功能验证与分析1

如何看懂GPU架构?一分钟带你了解GPU参数指标

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

NVMe高速传输之摆脱XDMA设计之十:NVMe初始化状态机设计

NVMe IP高速传输却不依赖XDMA设计之三:系统架构

NVMe能否发挥更大价值,全闪存阵列的架构是关键

NVMe能否发挥更大价值,全闪存阵列的架构是关键

评论