cpld是什么意思

CPLD(ComplexProgrammableLogicDevice)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

发展历史及应用领域

20世纪70年代,最早的可编程逻辑器件--PLD诞生了。其输出结构是可编程的逻辑宏单元,因为它的硬件结构设计可由软件完成(相当于房子盖好后人工设计局部室内结构),因而它的设计比纯硬件的数字电路具有很强的灵活性,但其过于简单的结构也使它们只能实现规模较小的电路。为弥补PLD只能设计小规模电路这一缺陷,20世纪80年代中期,推出了复杂可编程逻辑器件--CPLD。此应用已深入网络、仪器仪表、汽车电子、数控机床、航天测控设备等方面。

器件特点

它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强、价格大众化等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产(一般在10,000件以下)之中。几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。CPLD器件已成为电子产品不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

如何使用

CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。

这里以抢答器为例讲一下它的设计(装修)过程,即芯片的设计流程。CPLD的工作大部分是在电脑上完成的。打开集成开发软件(Altera公司Max+pluxII)→画原理图、写硬件描述语言(VHDL,Verilog)→编译→给出逻辑电路的输入激励信号,进行仿真,查看逻辑输出结果是否正确→进行管脚输入、输出锁定(7128的64个输入、输出管脚可根据需要设定)→生成代码→通过下载电缆将代码传送并存储在CPLD芯片中。7128这块芯片各管脚已引出,将数码管、抢答开关、指示灯、蜂鸣器通过导线分别接到芯片板上,通电测试,当抢答开关按下,对应位的指示灯应当亮,答对以后,裁判给加分后,看此时数码显示加分结果是否正确,如发现有问题,可重新修改原理图或硬件描述语言,完善设计。设计好后,如批量生产,可直接复制其他CPLD芯片,即写入代码即可。如果要对芯片进行其它设计,比如进行交通灯设计,要重新画原理图、或写硬件描述语言,重复以上工作过程,完成设计。这种修改设计相当于将房屋进行了重新装修,这种装修对CPLD来说可进行上万次。

-

cpld

+关注

关注

32文章

1259浏览量

174209 -

可编程逻辑器件

+关注

关注

5文章

145浏览量

31039

发布评论请先 登录

AG32 MCU Reference Manual(202401008修订版)使用手册

不用再画 CPLD!AG32 替代方案有多香?(二)

不用再画 CPLD!AG32 替代方案有多香?(一)

一起盘点AG32 MCU 的特性及产品特色,异构SOC入门推荐

AG32三合一芯片:为“国产替代”注入强芯动力 MCU+2K CPLD+64Mbit高集成 体积缩减一半 成本直降50%

谁家在低成本MCU中集成CPLD/FPGA,这有何优势呢?

AG32 内置的CPLD 的DMA功能如何实现?

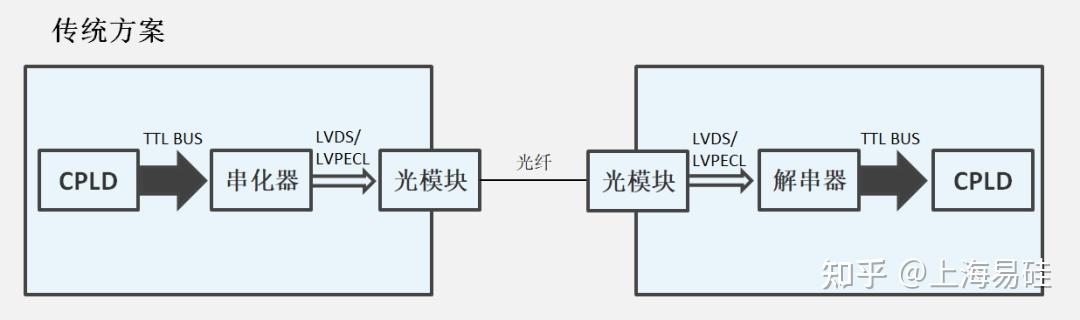

光端机新设计:AG32 + MS21112S 极简架构实现高性能低成本替代

cpld是什么意思

cpld是什么意思

评论