这里的Block是指Block RAM和DSP48。在有些设计中,这两者有其一或者两者均出现利用率比较高的情形,而且在某一版本中可以达到时序收敛。如果后续版本并不涉及到对Block的修改,特别是不会出现对Block RAM位宽的修改,为了达到时序收敛,一个可行的方案就是继承收敛版本的Block的布局。本质上,就是复用这些Block的位置信息。在Vivado下完成这样的操作非常简单。

Step 1

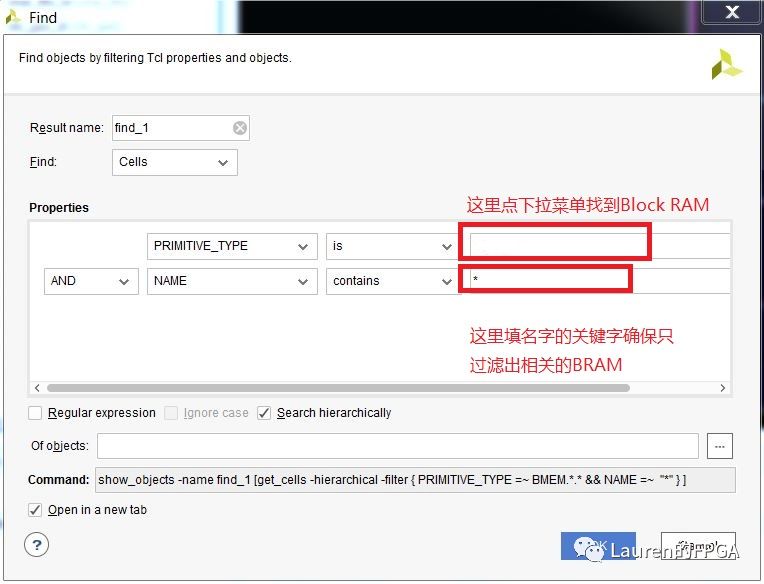

打开布线后的设计,并找到设计中的Block,这里以Block RAM为例,查找方法如下图所示,依次选择Edit -> Find,即可出现此界面。

Step 2

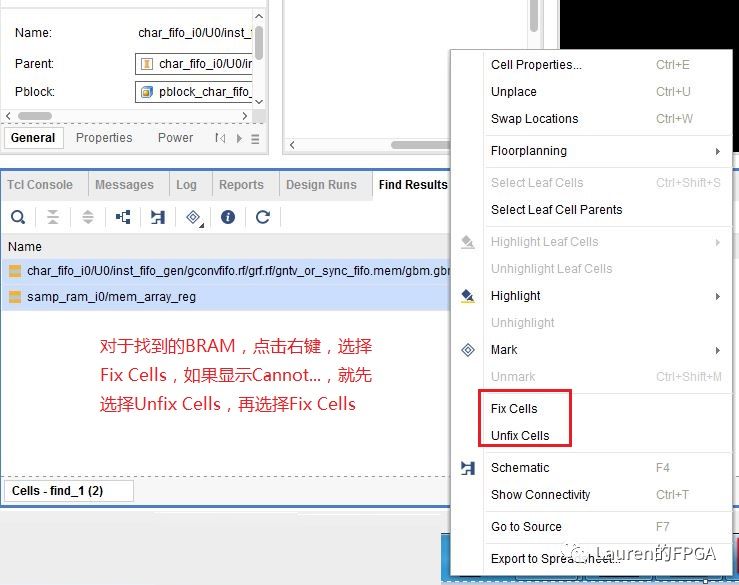

固定BRAM的位置。选中第一步中找到的BRAM,点击右键,选择Fix Cells即可,如下图所示。

Step 3

保存Block的位置信息。一旦固定了BRAM的位置,即可点击Vivado菜单栏内的保存按钮,这样就把BRAM的位置信息保存到了target约束文件中。一个小技巧是在保存之前创建一个新的约束文件,并把该文件设置为target约束文件,然后保存,这些信息就在该文件中,如下图所示。

实际上,上述操作均可通过Tcl脚本完成,如下图所示。

结论

对于Block RAM或DSP48利用率较高的情形,在时序收敛时,可继承其位置信息。这样,如果后续设计不牵涉到这些Block的改动,那么即可复用其位置信息,从而加速时序收敛的进程。

-

Block

+关注

关注

0文章

26浏览量

14562 -

BRAM

+关注

关注

0文章

40浏览量

10888

原文标题:如何复用原有设计中Block的位置

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RAW block 篇

FPGA 中的Block Diagram能直接联合Modelsim仿真吗?

Nand Flash中的坏块(Bad Block)

BCP中MOD子模块如何实现上行CQI复用,以及RI、ACK交织

for always可以在block中合成的吗?

最近在跑sharc中的例程出现问题 是我的block based talk through程序问题?

请问9K Block RAM设计中那些2 9K Block RAM在哪里?

怎么使原有的封装位置不变?

【技术干货】PADS模块复用(Reuse功能)使用方法

如何使用Vivado IP Block Design?

板内快速复用和板间快速复用

关于thumb指令中的IT block描述

光模块中的复用/解复用器——CWDM4 Z-BLOCK组件

如何复用原有设计中Block的位置

如何复用原有设计中Block的位置

评论