Kintex®-7 FPGA KC705 评估套件包括硬件、设计工具、IP 核和预验证参考设计等的所有基本组件,参考设计中包含能实现高性能、串行连接功能和高级存储器接口的目标设计。随套件提供预验证参考设计和行业标准 FPGA 夹层连接器(FMC),能够利用子卡实现升级和定制。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22280浏览量

630047 -

存储器

+关注

关注

39文章

7714浏览量

170797 -

赛灵思

+关注

关注

33文章

1797浏览量

133132

发布评论请先 登录

相关推荐

热点推荐

现已上市:AMD Spartan UltraScale+ FPGA SCU35 评估套件——面向所有开发人员的经济实惠平台

AMD Spartan UltraScale+ FPGA SCU35 评估套件现已开放订购。 该平台由 AMD 构建,为客户提供了一条利用 Spartan UltraScale+ FPGA

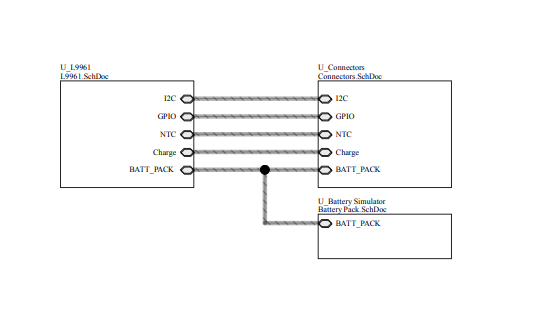

STEVAL-L99615C评估套件技术解析与应用指南

STMicroelectronics STEVAL-L99615C评估套件集成了扩展板,搭载L9961和NUCLEO-G071RB STM32 Nucleo-64开发板。这款评估套件

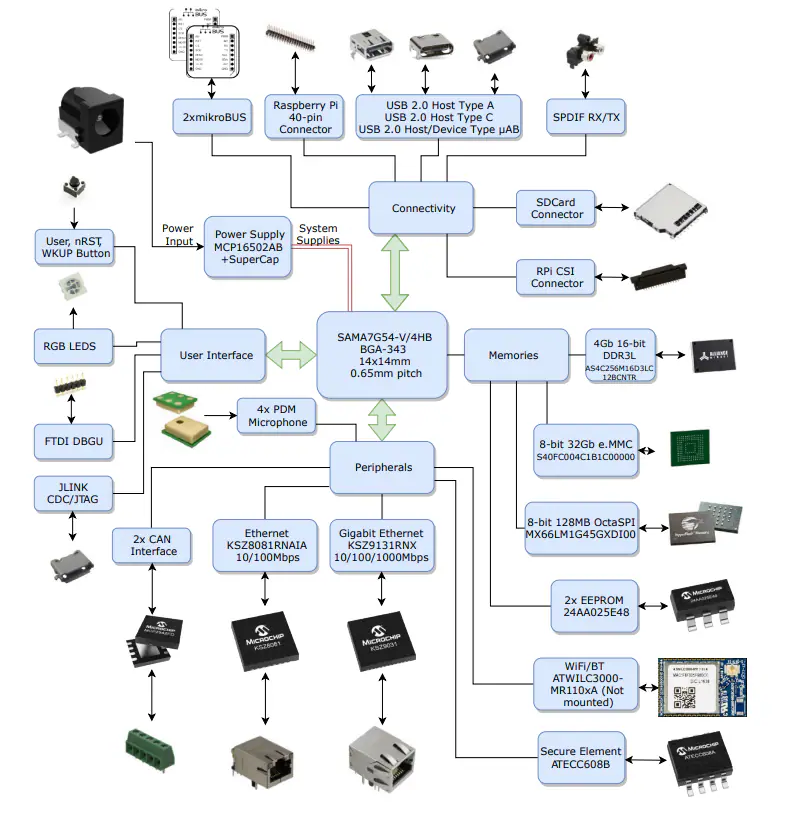

Microchip SAMA7G54-EK评估套件:为高性能嵌入式系统打造的全功能平台

Microchip Technology SAMA7G54-EK评估套件设计用于评估SAMA7G54微处理器以及对其进行原型设计。SAMA

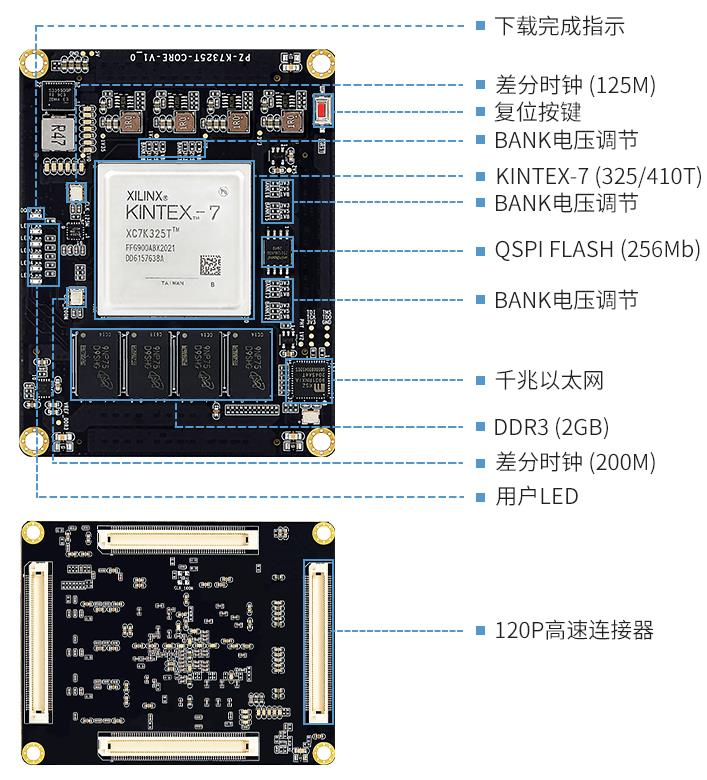

FPGA开发板—璞致 Kintex-7 系列核心板PZ-K7325T/PZ-K7410T 使用说明 XILINX核心板简介

PZ-K7325T/PZ-K7410T核心板采用Xilinx Kintex-7系列FPGA为主控制器,提供326080/406720个逻辑单元、2GB DDR3L内存和32MB QSPI Flash

【TES600G】青翼凌云科技基于JFM7K325T FPGA+FT-M6678 DSP的全国产化信号处理平台

的Kintex-7系列FPGAJFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在FP

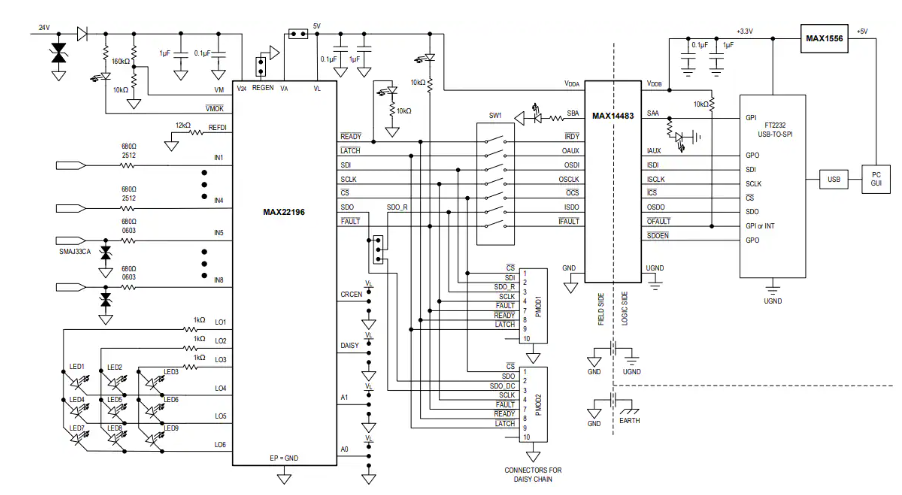

Analog Devices Inc. MAX22196EVKIT评估套件数据手册

的MAX22196之间建立SPI通信交易。MAX22196EVKIT评估套件包括Pmod™兼容连接器,用于与外部主令器件,包括微控制器 (MCU)、单元或现场可编程门阵列 (FPGA) 进行SPI通信。该

Analog Devices Inc. ADES1754 评估套件数据手册

Analog Devices Inc. ADES1754评估套件(EV套件)用于演示ADES1754/ADES1755/ADES1756数据采集系统的功能和特性。该

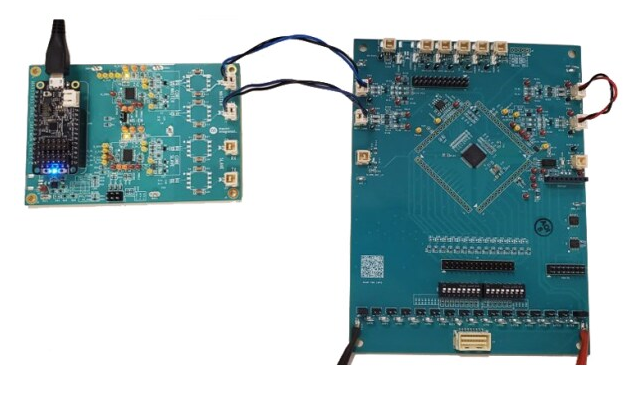

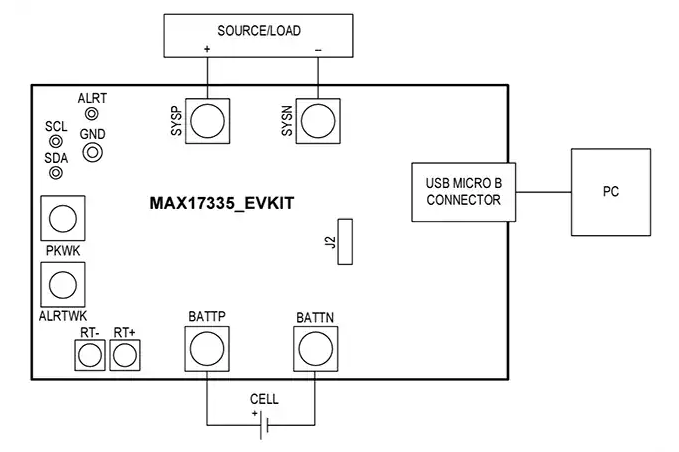

Analog Devices Inc. MAX17335 评估套件数据手册

节锂离子/聚合物电池的可选SHA-256认证。MAX17335评估套件包括带集成I^2^C接口和USB micro-B电缆的IC评估板。还可提供基于Windows®的图形用户界面(GUI)软件。该

Analog Devices Inc. MAX20363评估套件数据手册

可通过^I2C^接口进行配置,允许对各种功能进行编程并读取器件状态。该评估套件GUI应用向MAXPICO2PMB#适配器板发送命令,以配置器件。Analog Devices Inc.评估

Analog Devices / Maxim Integrated MAX9295xEVKIT串行器评估套件数据手册

串行链路(GMSL)串行器。该评估可使用标准FAKRA同轴电缆或屏蔽双绞线(STP)电缆进行。这些评估套件还包括WindowsXP®、Windows Vista®和Windows® 7

什么是SerDes?SerDes有哪些应用?

SerDes是一种功能块,用于对高速芯片间通信中使用的数字化数据进行序列化和反序列化。用于高性能计算(HPC)、人工智能(AI)、汽车、移动和物联网(IoT)应用的现代片上系统(SoC)都实现了

Kintex-7 GTX与TUSB522P数据转输需要注意哪些问题?

Kintex-7 GTX与 TUSB522P数据转输需要注意哪些问题,2.还有它的数据频率最高是5G吗

发表于 12-20 13:08

ADS54J64EVM开发板可以配套使用哪些Xilinx FPGA开发板呢?

个 FMC 连接器,该连接器也可与领先的FPGA制造商提供的许多开发套件兼容。

那么问题来了,TI的这两个AD开发板到底能不能直接用在Xilinx FPGA的其他通用开发板上,例如 KC705

发表于 12-20 10:18

Kintex-7 FPGA KC705评估套件的SERDES功能展示

Kintex-7 FPGA KC705评估套件的SERDES功能展示

评论