写在前面

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,时钟信号的好坏很大程度上影响了整个系统的稳定性,本文主要介绍了数字设计中的非理想时钟的偏差来源与影响。

理想时钟

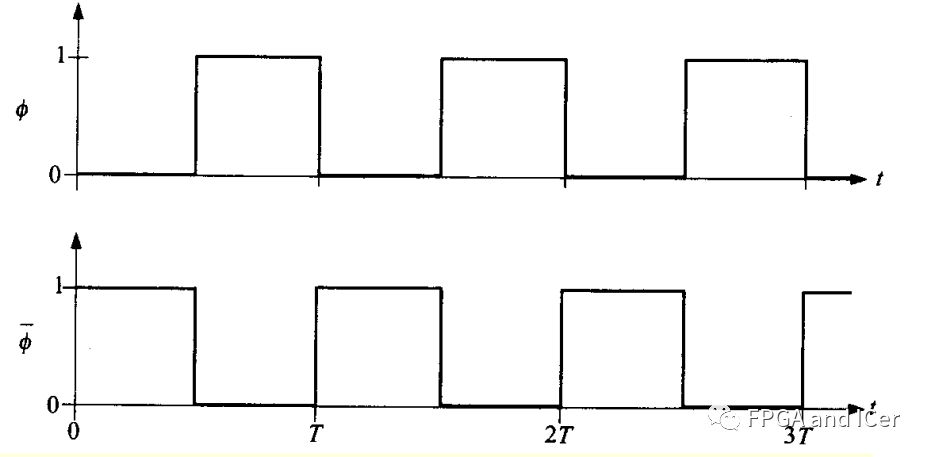

在数字设计中的理想时钟如下图所示:

理想时钟

理想时钟的特点如下:

- 时钟无重叠: 任意时刻下, Φ 与Φ非的与恒为零;

- 全轨输出: VDD - V(Φ) = V (Φ非);

- 时钟无延迟、无偏斜、无抖动 。

非理想性时钟

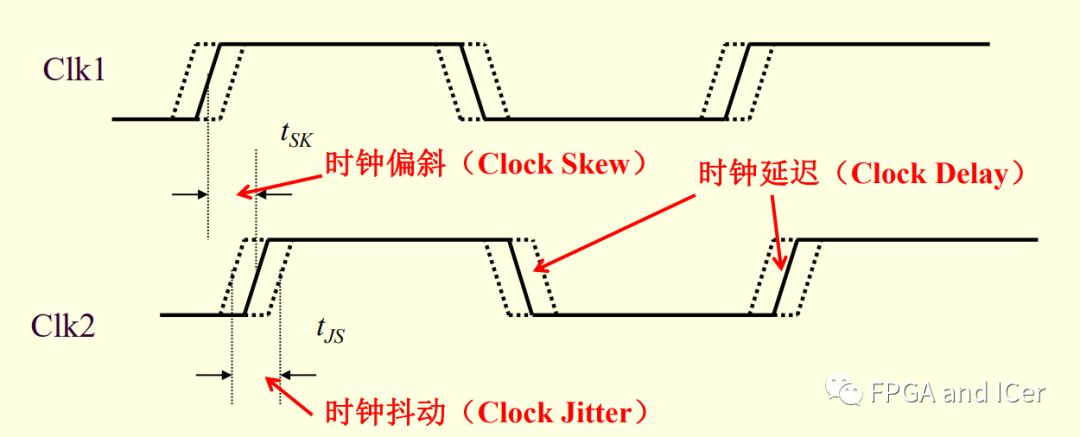

在数字设计中的非理想时钟如下图所示,和理想时钟相对立,如果不满足上述的理想时钟的相关特点,可认为其实一个非理想时钟。

非理想性时钟

对上图进行分析,假设CLK1、CLK2是同一个时钟树下的不同时钟,此时,两个时钟边沿的时间差就为时钟偏斜,同时,对于某一个时钟,在时钟变化边沿时,会有一定的随机性,所以这里随机的时钟周期变化叫做时钟抖动。

假设CLK1是CLK2的前级时钟,所以上图中两个时钟的边沿的时间差即为时钟延迟。

在上图中其实不能很准确体现出时钟延迟和时钟偏斜的概念区别,贴出另外一个图以供参考:

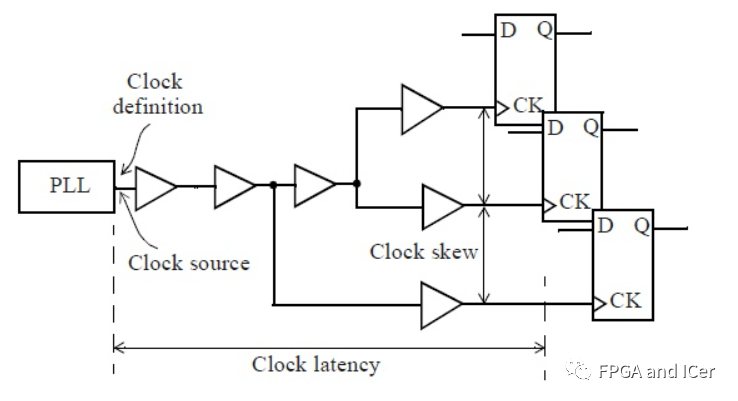

在下图中很容易理解时钟延迟和时钟偏斜的概念:

- 时钟延迟(clock latency)是指从时钟源到终点所花费的总时间。

- 时钟偏斜(clock skew)是指到达不同时钟树终点的时间差。

时钟偏斜主要来自时钟在空间上的不期望变化,时钟延迟和时钟抖动主要来自时钟在时间上的不期望变化。

时钟延迟(clock latency)

时钟延迟 (clock latency)是指从时钟源到终点所花费的总时间,主要针对的是一个时钟,从时钟源端输出到所驱动的器件的时钟输入端的时间延迟。

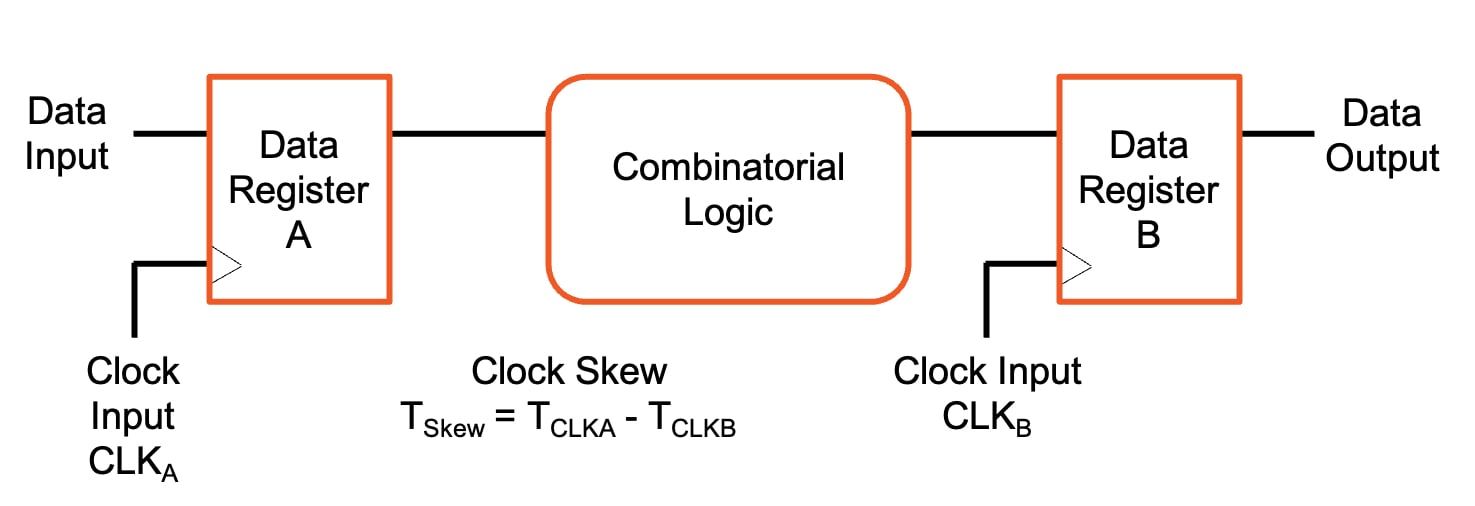

时钟偏斜(clock skew)

时钟偏斜(clock latency)是一对物理时钟的标称时间差与实际时间差之间的区别。理想情况下,时钟应同时到达系统中所有的钟控元件(锁存器、触发器、存储器和动态门等),这样系统才有一个共同的参考时间。实际中,时钟到达各点的时间稍微有些差别,这个差别就叫 时钟偏斜 。

两个不同时钟的时钟延迟,就是时钟偏斜。

时钟偏斜发生在两个时钟信号之间,一般不会引起电路实际时钟周期的变化,只会 导致时钟相位的偏移 ;时钟抖动可以发生在一个时钟信号自身,会 引起时钟周期的变化 。

时钟偏斜与时钟抖动统称为 时钟偏差 ,二者之和也叫 时钟不确定性(uncertainty) 。边沿之间的时钟抖动有时也被归于与时间相关的时钟偏斜。

时钟抖动(clock jitter)

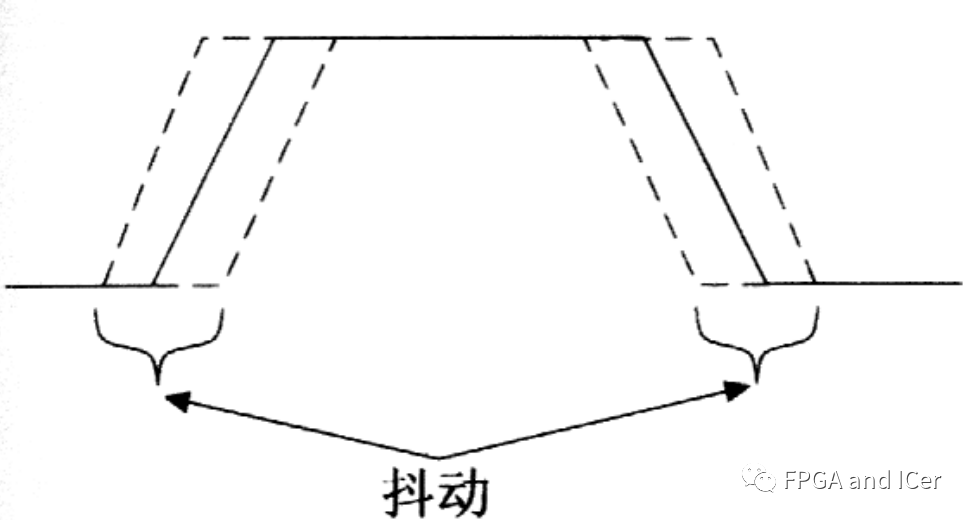

时钟抖动(clock jitter) 是指芯片的某一个给定点上时钟边沿发生暂时的随机变化,会导致时钟周期的缩短或加长。

时钟抖动

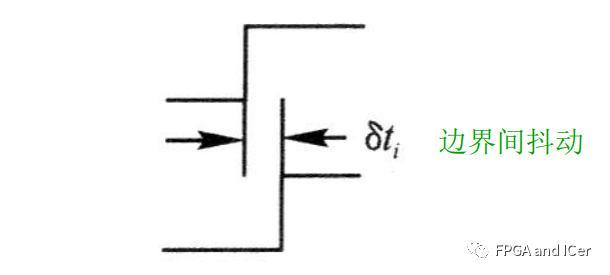

边界间抖动(edge-to-edge) :时钟边沿相对与理想时钟边沿的最大变化值,实际上是随时间变化的时钟偏斜。

边界间抖动

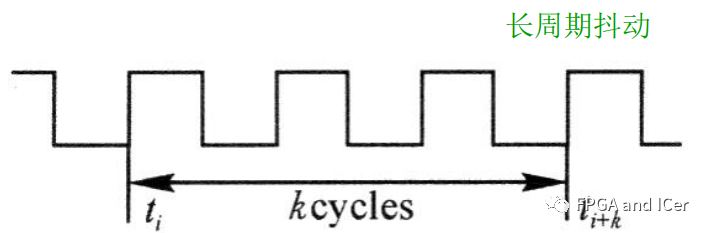

长周期抖动(k-cycle) :数个周期后边沿之间的最大变化值,主要影响芯片间的时序同步,也叫绝对抖动。

长周期抖动

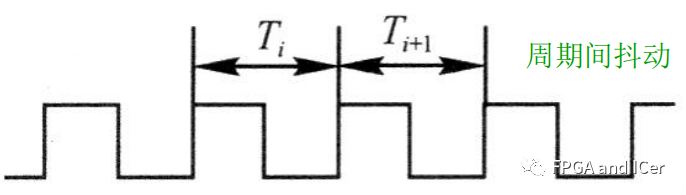

周期间抖动(cycle-to-cycle) :相邻时钟周期间的时变偏离,主要影响芯片内时序同步,也叫相对抖动。

周期间抖动

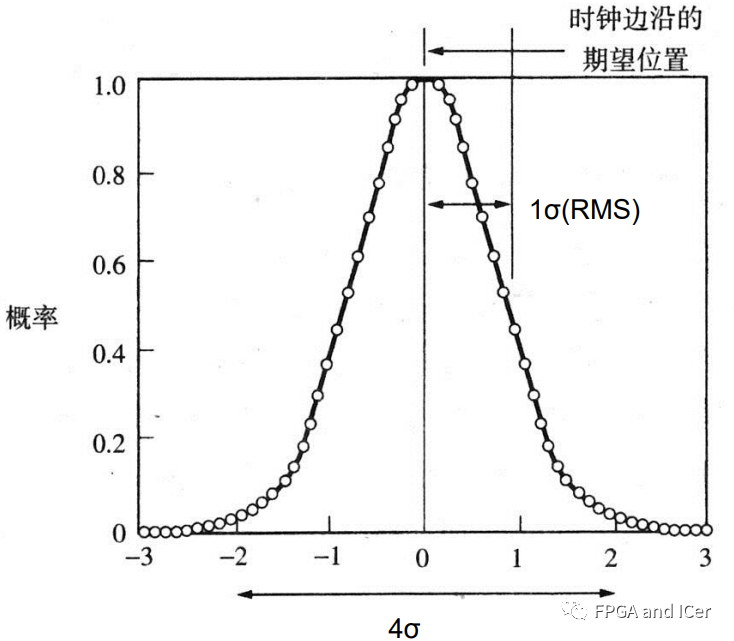

随机抖动(random jitter) :由器件和导线的固有噪声(如热噪声) 所致,为高斯分布,用均方根值(RMS)表征,无法预估。

随机绝对抖动的高斯分布

确定性抖动 (deterministic jitter) :确定性抖动由非理想传输效应、串扰、电源浪涌等所致,为非高斯分布,用峰峰值表征,可以预估。

在逻辑综合前,常采用理想时钟(逻辑时钟)+预设偏差的方式来模拟真实时钟;在物理设计时,完成实际时钟(物理时钟)的设计,其偏差必须满足系统要求。

- 逻辑时钟(logical clock) :没有时钟偏斜的理想时钟,逻辑设计者在用硬件描述语言描述系统行为时使用。

- 物理时钟(physical clock) :带有时钟偏斜的实际时钟,为了使系统达到预期行为,设计者不得不在时钟偏差、功耗、金属化资源利用率和设计代价之间寻求均衡。

- 全局时钟(global clock) :为整个系统提供基准的单一时钟。

布线对时序的影响

同一个时钟下,驱动不同的触发器,都需要在实际设计时候都需要进行布线,所以不同的触发器之间布线长短也会有一定差异。

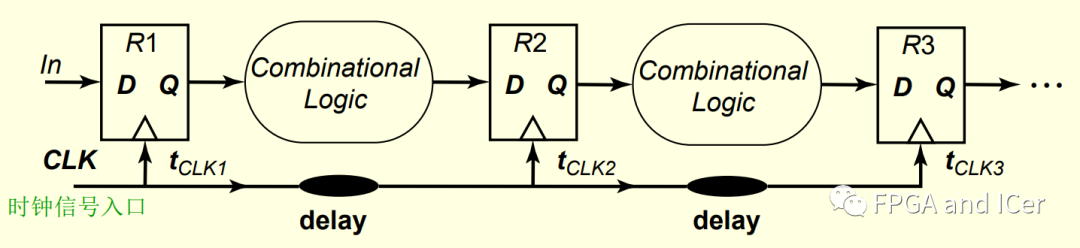

布线方向的影响:正偏差

时钟布线方向与数据通过流水线方向一致会使得时钟正偏差,也即,tskew > 0 。

好处:可采用更短的时钟周期从而得到更高的时钟频率,有利于提高数据通过率。

坏处:需采用更长的保持时间,以免出现冒险竞争。

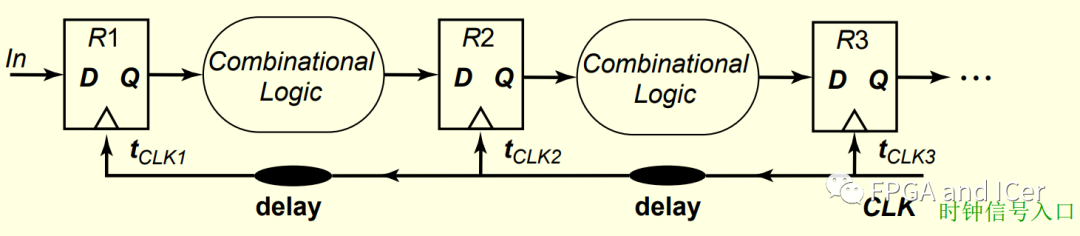

布线方向的影响:负偏差

时钟布线方向与数据通过流水线方向相反会使得时钟负偏差,也即,tskew < 0 。

好处:冒险竞争不易发生,提高了电路的健壮性。

坏处:加长了最小时钟周期从而降低了时钟频率,不利于提高数据通过率。

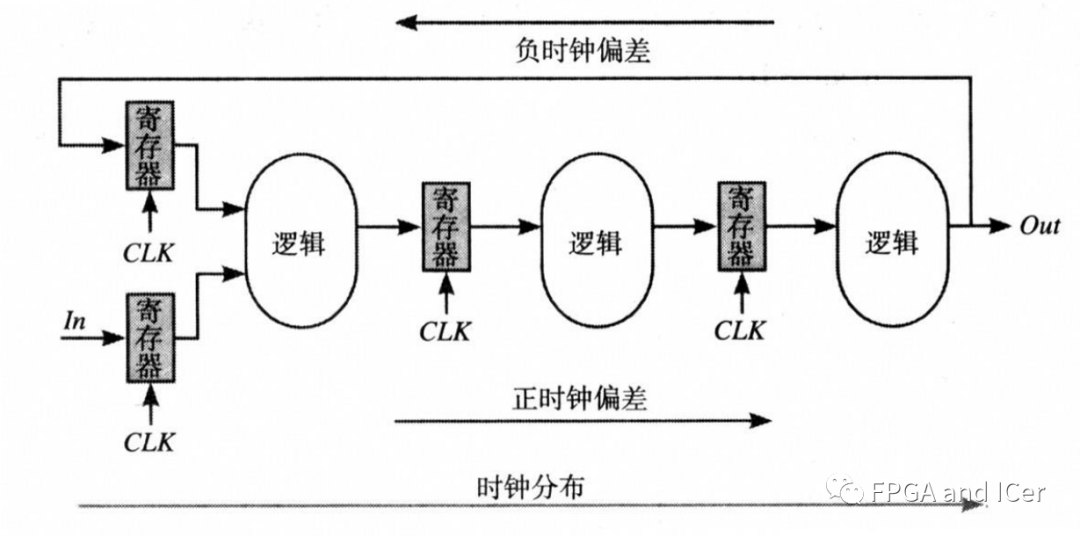

布线方向的影响:双向电路

时钟布线方向与数据通过流水线方向可能相同也可能相反,从而使正负偏差都存在。

一个较为理想的设计目标是使正、负偏差都很小,零偏差最好。

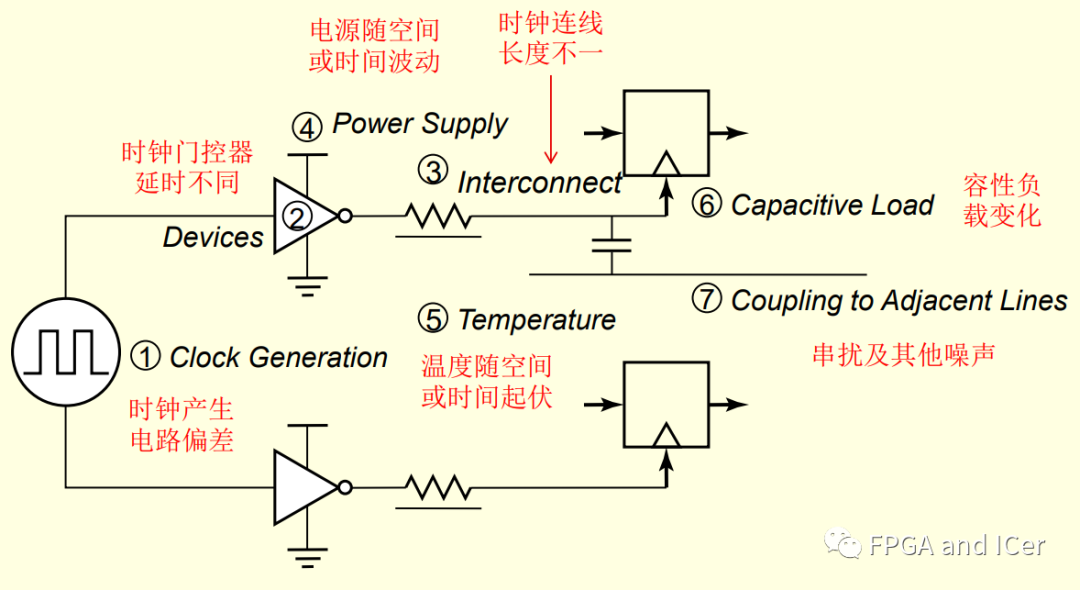

时钟偏差的来源

时钟偏差的来源大致如下图所示:

时钟偏差分析

结合上图中的引起时钟偏差来源,大致可对时钟偏差进行分类,系统偏差、随机(random)偏差、漂移(drift)偏差、抖动(jitter)偏差,不同类型的偏差的原因如下:

- 系统(systematic)偏差:时钟产生器、时钟门控器、电容负载、互连线的偏差,可预估并通过设计来纠正。

- 随机(random)偏差:工艺离散引起元器件和互连线参数的随机变化,无法预估,但可以测试,并用可校准延时元件来补偿。

- 漂移(drift)偏差:与时间有关的环境因素(如温度随时间变化、温度的空间梯度变化)变化所致,也可补偿,但需实时。

- 抖动(jitter)偏差:高频环境变化(如电源浪涌、串扰)导致的电路延时随时间和空间的变化,最难以防范,因补偿电路来不及对它进行响应。

下面针对其中几个原因进行举例分析。

时钟线长度不一引入偏差

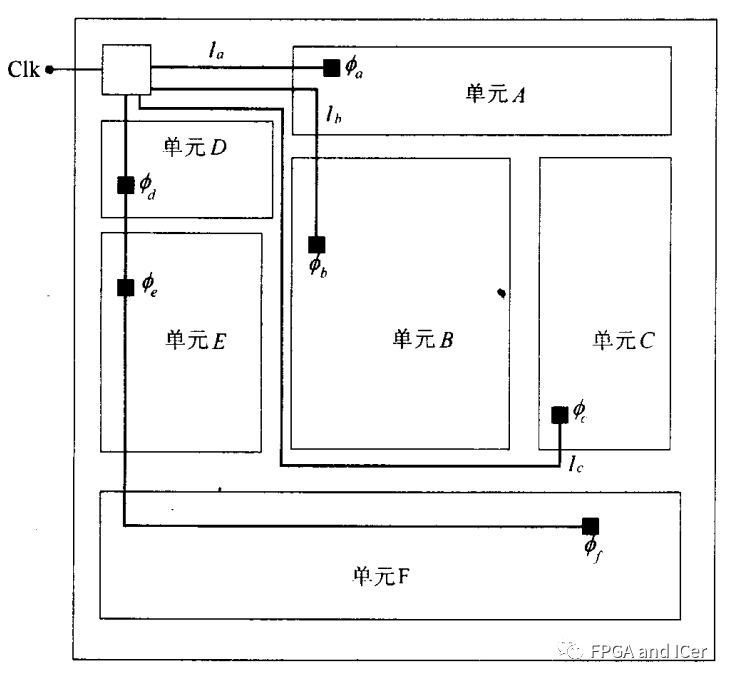

由于时钟在驱动不同单元时,不同单元布局分布在不同区域,所以使得时钟扇出的信号进行实际布线的长度长短不一,从而引起了时钟偏差,如下图所示,La和Lb长度不同,所以时钟对应到单元A和单元B的时钟延迟不同,使两个单元的时钟存在偏斜。

电源变化引入偏差

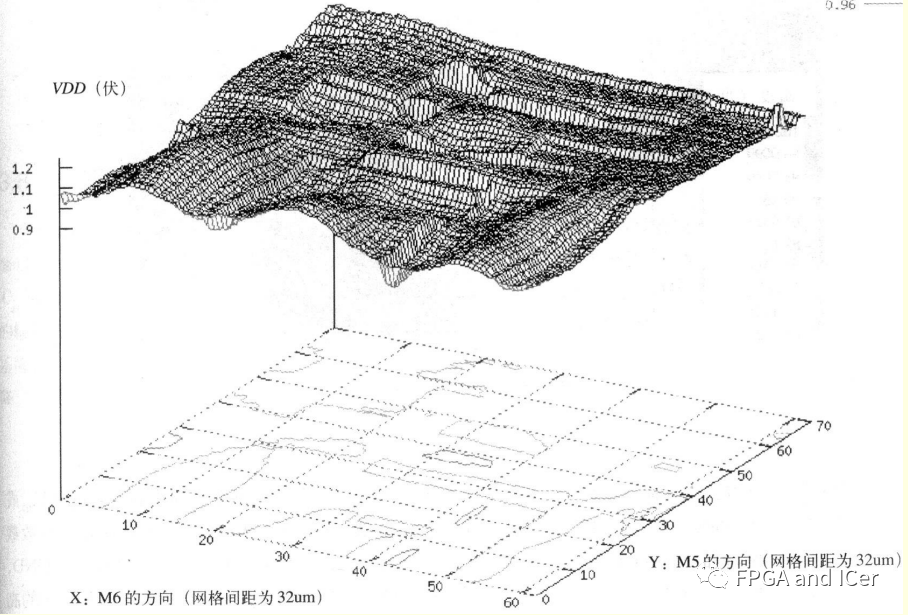

Itanium 2 处理器芯片电源电压的空间分布:1.2V标称电源电压下的最大变化为±100mV,由此导致的延时变化为13%/100mV。

Itanium 2电源电压的空间分布

温度变化引入偏差

对Itanium 2的仿真结果表明,温 度在芯片上的非 均匀分布达到 20℃时,会导致 1.5%的延时变化。

工艺变化引入偏差

工艺上变化也会引入时钟的偏差,如沟道长度、阈值电压和片上误差。

沟道长度:Itanium 2的标称值为180nm,工艺离散导致的偏差可能高达±12.5nm,这会导致±10%的延时变化。

阈值电压:0.18um工艺下,小nMOS管(W<12.5um)、小pMOS管、 大nMOS管、大pMOS管的标准偏差分别为16.8、14.6、7.9、3.5mV, 这会导致一个标准偏差为2%的延时分布。

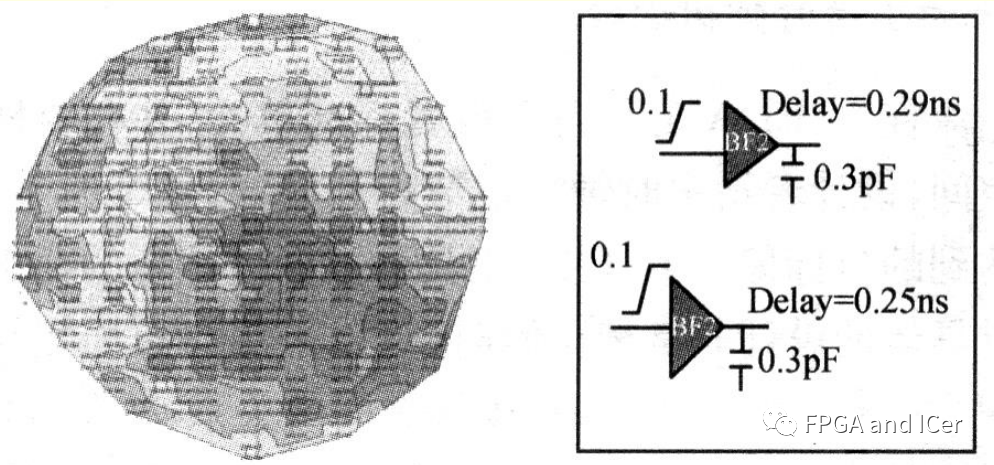

片上误差 (on-chip variation, OCV)空间分布,相同的缓冲器单元因所处芯片位置 不同而产生的延迟误差。

门控器引入偏差

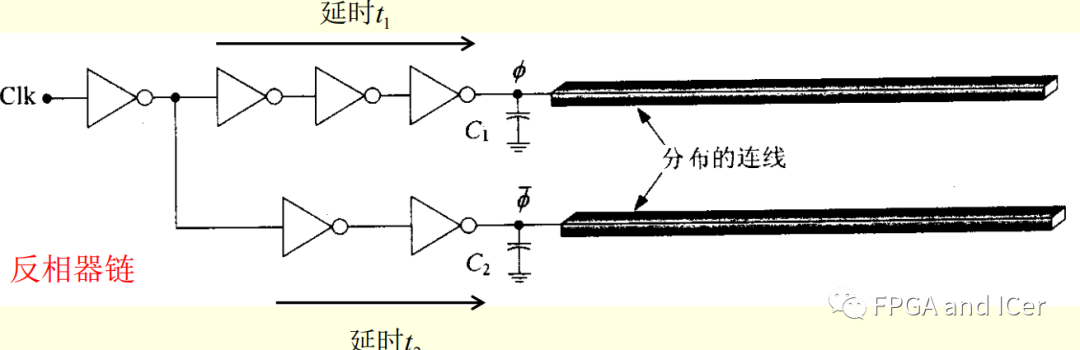

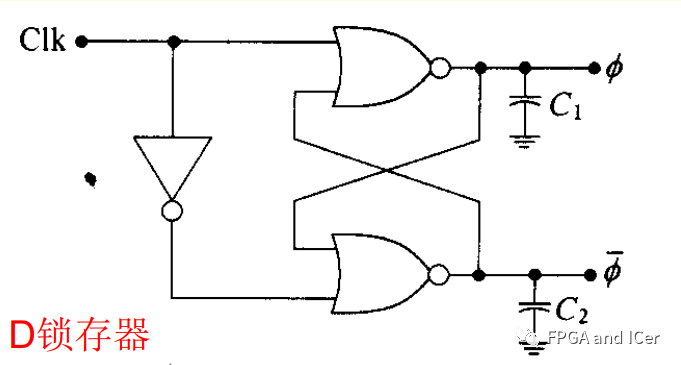

反相器链的延迟差以及C1与C2的差会导致时钟偏斜|t2 -t1 | 。采用逻辑努力技术合理设计反相器链的级数及门间面积比,可减少乃至消除此偏差。

下图的D锁存器的时钟偏斜来源于反相器的延迟以及C1与C2的差。通过调整两个NOR2门的面积 比,可对时钟偏斜进行补偿。

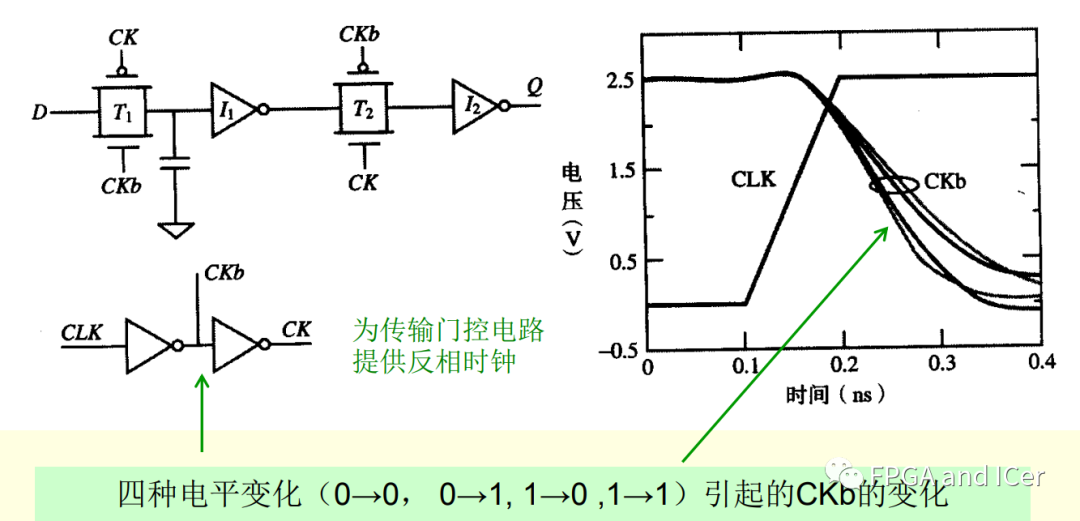

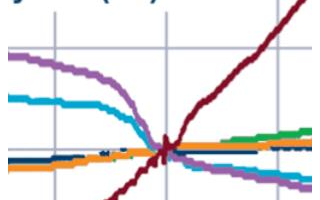

负载变化引入偏差

负载变化会引入时钟偏差,栅电容与所加电压有关,时钟负载与锁存器/寄存器的当前状态及下一个状态有关。如下图所示,不同电平变化会影响时钟负载的微小变化。

总结

- 时钟延迟(clock latency) 是指从时钟源到终点所花费的总时间。时钟偏斜(clock skew) 是指到达不同时钟树终点的时间差。时钟抖动(clock jitter) 是指芯片的某一个给定点上时钟边沿发生暂时的随机变化,会导致时钟周期的缩短或加长。

- 时钟偏斜 主要来自时钟在空间上的不期望变化,时钟延迟和时钟抖动 主要来自时钟在时间上的不期望变化。

- 时钟偏斜发生在两个时钟信号之间,一般不会引起电路实际时钟周期的变化,只会 导致时钟相位的偏移 ;时钟抖动可以发生在一个时钟信号自身,会 引起时钟周期的变化 。

- 时钟偏斜与时钟抖动统称为 时钟偏差 ,二者之和也叫 时钟不确定性(uncertainty) 。边沿之间的时钟抖动有时也被归于与时间相关的时钟偏斜。

- 布线方向会对时序造成正负偏差的影响,一个较为理想的设计目标是使正、负偏差都很小,零偏差最好。

- 时钟偏差分为,系统偏差、随机(random)偏差、漂移(drift)偏差、抖动(jitter)偏差,不同偏差的原因不同,可通过合理的设计将相应的影响规避或影响降至最低。

-

驱动器

+关注

关注

54文章

9012浏览量

153325 -

FPGA设计

+关注

关注

9文章

429浏览量

27997 -

ASIC设计

+关注

关注

0文章

33浏览量

11033 -

VDD

+关注

关注

1文章

318浏览量

36771 -

时钟信号

+关注

关注

4文章

495浏览量

29695

发布评论请先 登录

一文带你深度了解大型多GHz时钟树中的相位偏差

BUFGMUX定时时钟偏差太大

如何使用DCM减少时钟偏差?如何使用DCM来增加时钟?

如何通过PLL修复时钟偏差?

时钟网格与时钟树设计方法对比研究

大型时钟树设计时的相位偏差问题及方法建设

什么是时钟偏斜?了解时钟分配网络中的时钟偏斜

【世说知识】一文带你深度了解大型多GHz时钟树中的相位偏差

谈谈非理想时钟的时钟偏差

谈谈非理想时钟的时钟偏差

评论