UltraScale/UltraScale+芯片开始支持BUFG_*、PLL和MMCM出现在动态区,在7系列FPGA中这些时钟资源只能在静态区。当这些时钟资源出现在动态区时应遵循如下规则:

动态区的Pblock

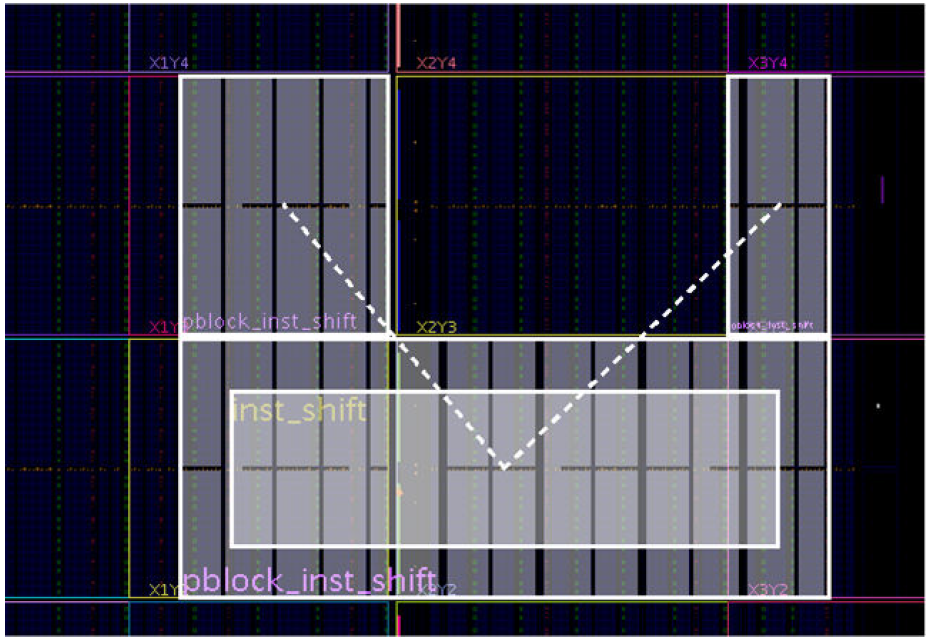

动态区的Pblock形状最好是标准的矩形。如果这个Pblock是由多个矩形共同构成,那么最高的那个矩形应和时钟区域边界对齐。避免出现U形或H形Pblock。U形Pblock如下图所示。这会增大布线难度。

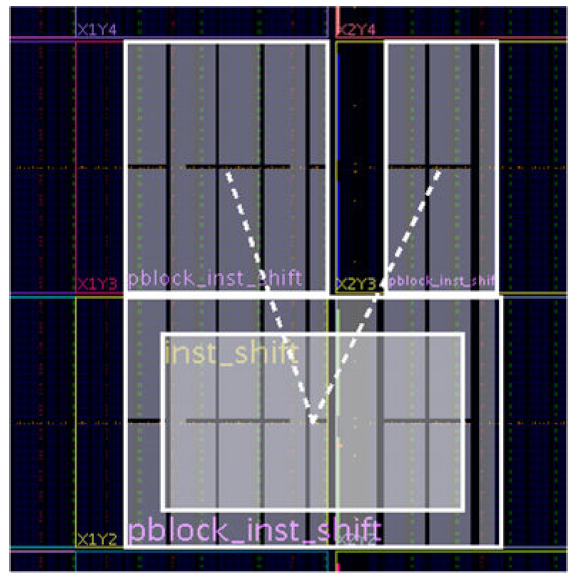

类似地,在动态区中间出现小的静态区,如下图所示,I/O列位于动态区Pblock夹缝中,这是允许的,但仍然要尽量避免,因为在角落处容易出现布线拥塞。

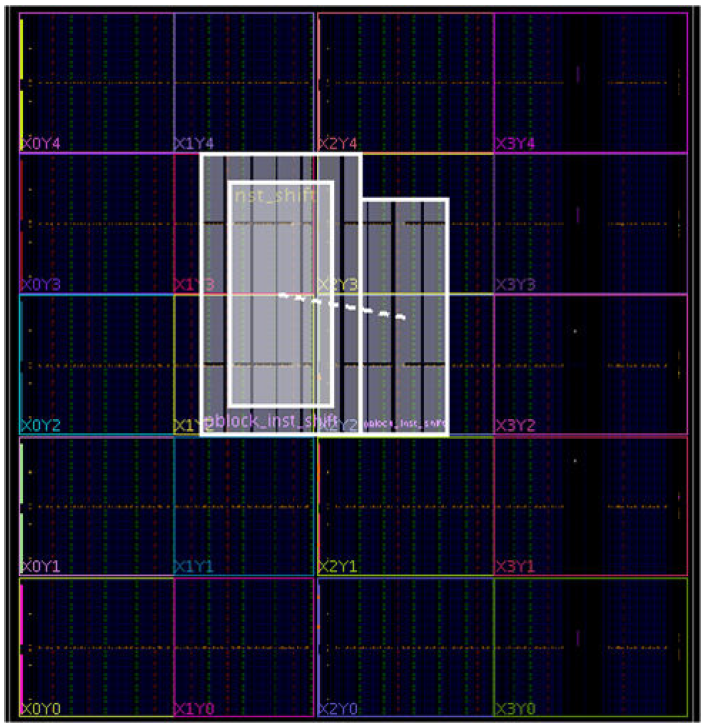

如下图所示的这种楼梯形状的Pblock也要避免,同样会在拐角处导致布线拥塞。

还需要注意的是同一个时钟区域只可以存在一个RP对应的Pblock,换言之,不支持时钟区域被多个RP共享,即使Pblock并未发生重叠。

CLOCK_ROOT

当Pblock是由多个矩形构成时,工具会自动将RM内时钟的CLOCK_ROOT放置在最高的矩形对应的Pblock所在的时钟区域内。

但是,如果用户通过属性USER_CLOCK_ROOT提前约束了该时钟的CLOCK_ROOT,工具就会遵循这个约束值。

这就可能出现USER_CLOCK_ROOT的值不合理的情形即不是最高矩形Pblock所在的时钟区域内,这就很容易导致布线失败。

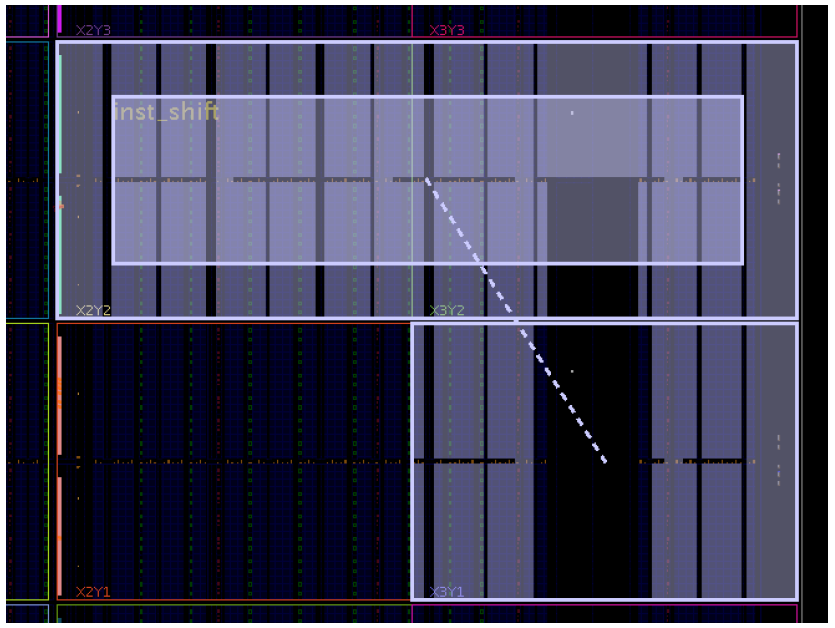

如下图所示,如果USER_CLOCK_ROOT的值为X2Y2,对应Pblock左上角的时钟区域,那么时钟布线是无法到达Pblock

右下角即X3Y1时钟区域的。相反,如果USER_CLOCK_ROOT设定为X3Y1或X3Y2,那么就不会出现布线失败的问题。

当动态区的时钟是由BUFG_GT驱动(显然BUFG_GT的输入来自于高速收发器的输出)时,需要注意BUFG_GT驱动的时钟要求其CLOCK_ROOT和BUFG_GT在同一个时钟区域内。

如果该时钟区域不是最高的Pblock对应的时钟区域,同样会出现布线失败。

这时解决方案是:复制BUFG_GT,一个和GT连接给GT逻辑用,一个给用户逻辑用,这样每个时钟就可以单独设置自己的CLOCK_ROOT。

全局时钟使用规则

如果时钟源在RM(RP1)内,那么该时钟既可以驱动静态区的逻辑,也可以驱动其他RM(RP2)内的逻辑。

但需要注意:因为时钟源是在RP1对应的RM内,因此RP1下的所有RM时钟拓扑结构必须保持一致,即如果RP1/RM1使用的是MMCM+BUFGCE的结构,那么RP1/RM2也必须使用此结构,这样时钟走线才能保持一致。但可以允许RP1/RM1和RP1/RM2内MMCM的参数不同,以支持不同的输出频率。

因为时钟源在动态区,如果动态区产生的时钟要驱动静态区的逻辑,那么对该时钟也要做隔离。常规信号可采用2:1的MUX进行隔离,但对于高扇出的时钟信号是不能采用此隔离方案的。这时可使用BUFGMUX,或者在重配置时将静态区的逻辑置于复位状态。

审核编辑:刘清

-

FPGA

+关注

关注

1655文章

22283浏览量

630271 -

收发器

+关注

关注

10文章

3794浏览量

110578 -

DFx

+关注

关注

0文章

36浏览量

11055 -

时钟源

+关注

关注

0文章

108浏览量

16641 -

时钟信号

+关注

关注

4文章

495浏览量

29695

原文标题:针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(2)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

赛灵思推出全球最大容量的FPGA – Virtex UltraScale+ VU19P

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

闲话Zynq UltraScale+ MPSoC(连载1)

Xilinx 宣布Vivado设计套件开始支持16nm UltraScale+产品早期试用

Zynq UltraScale+ MPSoC的发售消息

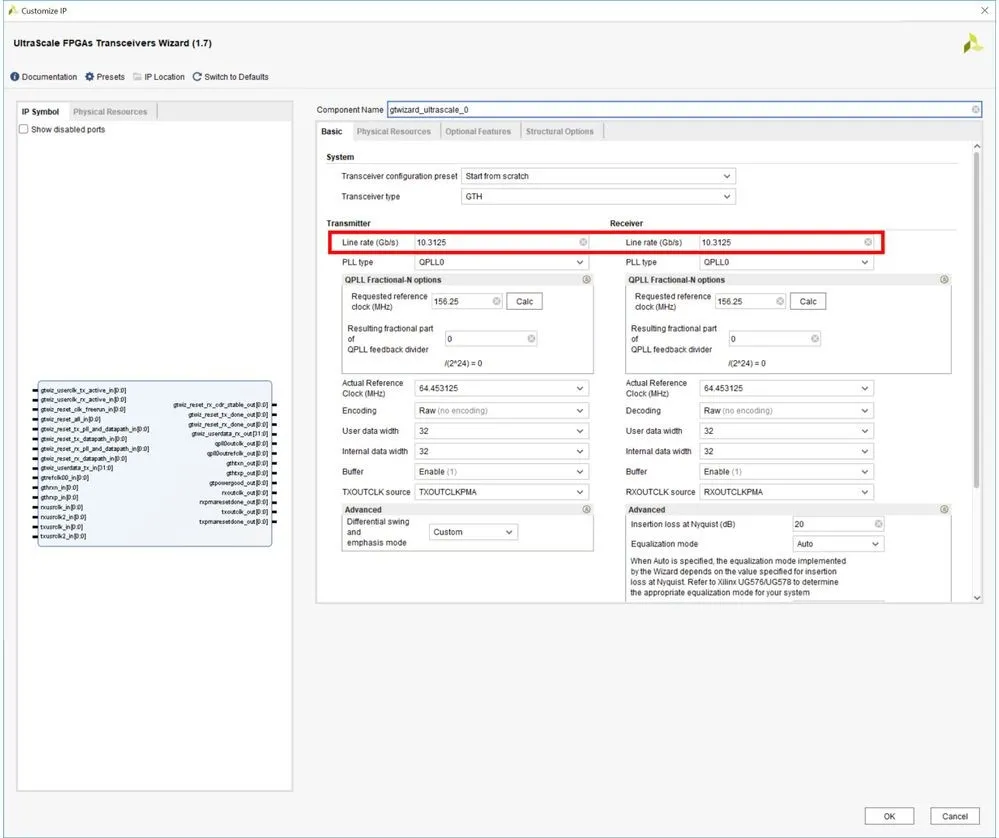

UltraScale/UltraScale+ GTH/GTY 收发器线速率设置的方法

UltraScale/UltraScale+的时钟资源

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计

使用加密和身份验证来保护UltraScale/UltraScale+ FPGA比特流

UltraScale和UltraScale+ FPGA封装和管脚用户指南

AMD推出全新Spartan UltraScale+ FPGA系列

针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(2)

针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(2)

评论