(BLDC)无刷电机内置驱动板因 “电机 + 驱动” 一体化封装,存在功率密度高、PCB 空间狭小、功率回路与控制回路近距离耦合等特点,极易产生电磁干扰(EMI),同时对外部电磁骚扰(EMS)敏感度提升,成为制约产品合规与可靠性的核心瓶颈。本文从内置驱动板 EMC 干扰源机理出发,系统剖析传导干扰、辐射干扰、静电放电(ESD)、浪涌等电磁兼容问题成因,重点阐述硬件电路 EMC 优化、PCB 电磁兼容布局、滤波与接地设计、屏蔽隔离技术及软件降噪策略,形成 “干扰源抑制 - 传播路径阻断 - 敏感电路防护” 全链路 EMC 解决方案,为内置驱动板通过 CE/FCC 认证、降低电磁噪声、提升工作稳定性提供技术支撑。

1 引言

内置驱动板将三相功率逆变、栅极驱动、MCU 主控、采样检测、电源管理等电路集成于电机壳体内,功率回路走线极短、寄生参数小的同时,也导致强电与弱电高度密集、电磁耦合路径短、散热条件受限,EMC 问题更为突出:

传导干扰:通过电源母线向外辐射 150kHz~30MHz 的差模 / 共模干扰,超标会导致电网污染;

辐射干扰:MOS 管高速开关产生的 dv/dt、di/dt 形成高频辐射(30MHz~1GHz),干扰周边敏感电子设备;

电磁敏感度:电机反向电动势、静电放电、电网浪涌易击穿驱动器件或导致 MCU 误触发;

电磁噪声:EMI 耦合至采样电路与控制回路,引发电流 / 转速波动、换相抖动,影响控制精度。

EMC 设计的核心是 “抑制干扰源、切断传播路径、保护敏感电路”,结合内置驱动板的集成特性,需从硬件选型、电路拓扑、PCB 布局、接地滤波、软件优化多维度协同设计,才能实现电磁兼容与降噪目标。

2 内置驱动板 EMC 干扰源与传播机理

2.1 核心干扰源分析

2.1.1 功率开关干扰(主要干扰源)

三相全桥 MOS 管(或 IGBT)的高频开关动作是最大 EMI 源头:

电压跳变干扰(dv/dt):MOS 管开关速度达 ns 级,漏源极电压变化率可达 10~100V/ns,产生强电场辐射;

电流跳变干扰(di/dt):开关过程中回路电流快速变化(可达 10~100A/μs),在寄生电感上感应高压尖峰(U=L・di/dt),形成传导与辐射干扰;

开关损耗与振铃:MOS 管开通 / 关断延迟、寄生参数引发的续流振铃,产生宽频谱噪声。

2.1.2 电机侧干扰

反向电动势:电机绕组高速换相时产生千伏级电压尖峰,通过功率回路耦合至驱动电路;

绕组共模电流:电机绕组对地分布电容形成共模电流回路,成为传导干扰的重要组成部分;

机械电磁噪声:电机气隙磁场不平衡、磁滞损耗引发的电磁振动,叠加电磁干扰形成复合噪声。

2.1.3 控制与采样回路干扰

MCU 时钟噪声:晶振、PWM 输出产生的高频时钟信号(1~100MHz),通过 PCB 走线辐射;

采样信号耦合:电流 / 电压采样电路受功率回路电磁耦合,导致采样失真,引发控制误差。

2.2 干扰传播路径

传导路径:通过电源母线(差模干扰)、接地回路(共模干扰)、信号线传导;

辐射路径:通过空间电磁场耦合,高频电流回路形成 “小天线” 辐射,或通过 PCB 辐射;

耦合路径:功率回路与控制回路之间的寄生电容、互感耦合,即 “近场耦合”。

3 硬件电路 EMC 优化设计(干扰源抑制)

3.1 功率器件选型与驱动优化

3.1.1 MOS 管选型

平衡开关速度与 EMI:选择中等开关速度(trr=50~200ns)的 MOS 管,避免追求极致开关速度导致的强 dv/dt 干扰;

低寄生参数:优先选择 Ciss、Coss、Crss 小的 MOS 管,降低开关过程中的电容充放电噪声;

足够耐压余量:MOS 管耐压≥母线电压 2 倍,耐受反向电动势尖峰,减少击穿风险。

3.1.2 栅极驱动电路优化

栅极驱动是控制 MOS 管开关特性的核心,直接影响 EMI 水平:

可调栅极电阻:串联 10~100Ω 栅极电阻,减缓开关速度(降低 dv/dt、di/dt),抑制 EMI;上桥臂与下桥臂可选用不同阻值,平衡开关损耗与干扰;

栅极钳位与续流:并联 TVS 管或稳压管钳位栅极电压,防止过压击穿;增加栅极下拉电阻,避免悬空误开通;

集成预驱芯片:选用带死区控制、斜率控制的栅极驱动芯片,内置抗干扰逻辑,减少驱动回路噪声。

3.2 电源电路 EMC 设计

3.2.1 输入 EMI 滤波

采用 “差模 + 共模” 复合滤波拓扑,抑制传导干扰:

π 型滤波网络:串联共模电感(CMC),并联 X 电容(跨接火线 - 零线 / 正极 - 负极)、Y 电容(跨接火线 - 地 / 正极 - 地);

共模电感选型:选择高磁导率、低直流电阻的共模电感,额定电流≥1.5 倍最大工作电流,抑制共模干扰;

滤波电容选型:X 电容选用聚丙烯电容(耐高压、低 ESR),Y 电容选用安规电容(满足 IEC 60384-14),容量根据滤波频率匹配(150kHz~30MHz 常用 0.1~1μF)。

3.2.2 电源稳压与去耦

高压母线去耦:在 MOS 桥附近并联高频电解电容(10~100μF)+ 陶瓷电容(0.1~1μF),抑制母线电压波动,就近提供开关电流;

低压控制电滤波:DC-DC 输出端并联多层陶瓷电容(0.1μF+1μF),MCU、运放等敏感器件电源引脚旁放置 0402 封装的 0.1μF 去耦电容,缩短去耦路径;

隔离电源(可选):对敏感控制电路采用隔离 DC-DC 供电,切断共模干扰传导路径。

3.3 钳位与保护电路设计

抑制电压尖峰与静电 / 浪涌干扰:

母线钳位:在三相输出端、母线正负极并联 TVS 管或 RC 吸收网络(R=10~100Ω,C=10~100nF),吸收反向电动势与开关尖峰;

ESD 防护:通信接口(UART/CAN/PWM)、电源输入端串联 ESD 二极管(IEC 61000-4-2 Level 4,±8kV 接触放电);

浪涌抑制:电源输入端串联自恢复保险丝 + 压敏电阻,抑制电网浪涌(IEC 61000-4-5 Level 3,2kV/5kA)。

4 PCB 布局 EMC 设计(传播路径阻断)

内置驱动板 PCB 空间狭小、异形布局多,布局是 EMC 设计的关键,核心原则是 “缩短功率回路、强弱电分区、减少电磁耦合”。

4.1 功率回路布局优化

功率回路(MOS 桥、母线电容、电机接线柱)是 EMI 强辐射源,布局核心是 “最小化回路面积”:

三相全桥 MOS 管紧凑布局:上桥臂与下桥臂 MOS 管对称排列,源极 / 漏极走线短而粗(铜皮厚度≥2oz),减少寄生电感;

母线电容就近摆放:高频去耦电容紧贴 MOS 桥电源引脚,正负极走线最短,形成 “电容 - MOS 管” 小面积回路,降低 di/dt 引发的尖峰;

电机接线柱靠近 MOS 桥输出端:三相输出走线短、等长,避免长距离走线形成 “辐射天线”;输出走线采用差分对称布局,减少差模干扰。

4.2 强弱电分区与隔离

物理分区:PCB 划分 “功率区”(MOS 桥、母线电容、电机接口)与 “控制区”(MCU、采样电路、通信接口),两区之间预留 2~5mm 隔离带,或用地沟隔离;

走线隔离:功率走线与控制走线(尤其是采样线、时钟线)保持≥3mm 距离,避免平行走线;若必须交叉,采用垂直交叉减少耦合;

接口隔离:CAN、UART 等外部接口采用光耦或隔离芯片隔离,切断共模干扰传导路径。

4.3 敏感电路布局保护

采样电路:电流采样电阻紧贴 MOS 桥下桥臂,采样走线采用差分走线,远离功率走线;采样运放放置在采样电阻附近,缩短输入线长度,避免干扰耦合;

MCU 电路:晶振电路是高频干扰源,晶振、电容紧贴 MCU 晶振引脚,晶振外壳接地;MCU 电源引脚去耦电容就近摆放,时钟线、PWM 输出线尽量短,避免形成长走线辐射;

霍尔 / 位置传感电路:霍尔接口走线采用上拉电阻 + 滤波电容,远离功率回路,必要时采用屏蔽线。

5 滤波与接地设计(干扰抑制关键)

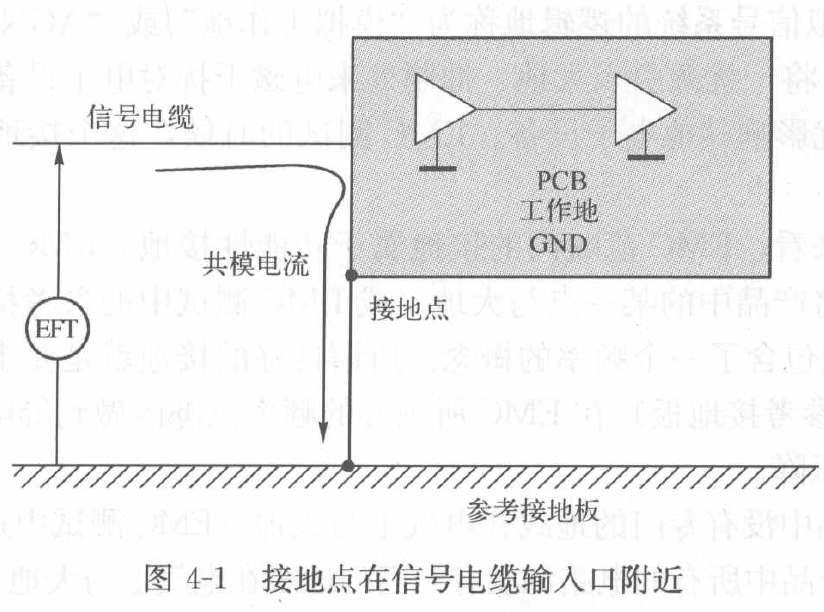

5.1 接地系统设计

接地是 EMC 设计的 “生命线”,内置驱动板需采用 “分区接地、单点共地” 策略,避免地弹噪声与共模干扰:

地平面划分:PCB 设置独立的 “功率地(PGND)” 与 “信号地(SGND)”,功率地承载大电流,信号地保障控制回路稳定性;

单点共地:功率地与信号地在 PCB 单点连接(推荐在电源滤波电容处共地),避免大电流在信号地平面形成压降,导致控制电路误动作;

地平面完整性:信号地平面尽量完整,减少开槽,降低接地阻抗;功率地平面采用大面积铜皮,提升散热与抗干扰能力。

5.2 关键信号滤波设计

采样信号滤波:电流 / 电压采样信号经 RC 低通滤波(R=1~10kΩ,C=10~100nF)后送入 MCU ADC,截止频率根据采样频率与干扰频率匹配,抑制高频噪声;

通信接口滤波:UART/CAN 接口串联共模电感,并联 TVS 管与滤波电容,抑制线缆传导与辐射干扰;

霍尔信号滤波:霍尔输出信号并联 0.1~0.01μF 滤波电容,上拉电阻靠近电源端,减少信号抖动。

6 屏蔽与隔离技术(敏感电路防护)

6.1 电磁屏蔽设计

针对内置驱动板的密闭环境,采用局部屏蔽与结构屏蔽结合:

PCB 局部屏蔽:功率区与控制区之间设置铜皮屏蔽墙(高度≥2mm),并接地,阻断电磁耦合;

器件屏蔽:选用带屏蔽罩的共模电感、晶振,减少器件自身辐射与外界干扰;

结构屏蔽:电机壳体接地,驱动板关键区域(如 MOS 桥、采样电路)铺铜开窗,通过导热垫与电机壳体连接,利用壳体实现电磁屏蔽与散热。

6.2 隔离技术应用

电源隔离:采用隔离式 DC-DC 模块给 MCU、采样运放供电,隔离高压侧与低压侧的共模干扰;

信号隔离:霍尔传感器、通信接口采用光耦或数字隔离芯片隔离,避免强电干扰传导至控制回路;

驱动隔离:栅极驱动电路与 MCU 之间采用光耦隔离,防止功率回路的高压尖峰击穿 MCU I/O 口。

7 软件降噪优化(辅助抑制干扰)

软件优化作为硬件 EMC 设计的补充,可进一步降低电磁噪声与控制误差:

PWM 频率优化:选择合适的 PWM 载波频率(10~20kHz),避免与周边设备共振频率重叠;采用变频 PWM(跳频技术),分散干扰频谱,降低峰值干扰强度;

死区时间优化:合理设置 MOS 管上下桥臂死区时间(1~5μs),避免直通烧毁的同时,减少死区时间过长导致的电流畸变与 EMI;

控制算法优化:采用 FOC 矢量控制替代方波六步换相,降低电流纹波与转矩脉动,减少电磁噪声;增加软件滤波算法(如滑动平均滤波、卡尔曼滤波),对采样信号与转速信号降噪,提升控制稳定性;

故障容错设计:MCU 增加看门狗定时器、电源监控电路,避免电磁干扰导致程序跑飞;软件检测过流、过压、过温故障时,快速封锁 PWM 输出,保护驱动板与电机。

8 EMC 测试与调试要点

8.1 关键 EMC 测试项目

传导发射(CE):测试 150kHz~30MHz 电源母线传导干扰,需满足 EN 55032 Class B 标准;

辐射发射(RE):测试 30MHz~1GHz 空间辐射干扰,需满足 EN 55032 Class B 标准;

静电放电(ESD):测试接触放电 ±8kV、空气放电 ±15kV,满足 IEC 61000-4-2 标准;

浪涌抗扰度:测试电源端 ±2kV 浪涌,满足 IEC 61000-4-5 标准。

8.2 调试优化技巧

干扰定位:使用示波器 + 电流探头、频谱分析仪定位干扰源(如 MOS 管开关尖峰、母线噪声),针对性优化;

滤波参数调整:通过测试调整 EMI 滤波器、RC 滤波的电阻电容值,使干扰频谱低于限值;

布局迭代:若 EMI 超标,优先优化功率回路布局(缩短回路面积、增加隔离距离),其次调整滤波与接地。

无刷电机内置驱动板的 EMC 设计需围绕 “干扰源抑制、传播路径阻断、敏感电路防护” 核心逻辑,通过硬件选型优化(低 EMI 功率器件、可调栅极驱动)、电路拓扑设计(EMI 滤波、钳位保护)、PCB 精细化布局(功率回路最小化、强弱电分区)、接地滤波优化(分区接地、单点共地)、屏蔽隔离技术(局部屏蔽、电源 / 信号隔离)及软件降噪策略(变频 PWM、算法滤波)的协同配合,才能有效抑制传导 / 辐射干扰、提升电磁敏感度、降低电磁噪声。

随着内置驱动板向更高功率密度、更小体积、更高集成度发展,EMC 设计将面临更大挑战,未来需结合宽禁带半导体器件(SiC/GaN)的应用、集成 EMI 滤波器的功率模块、AI 辅助 EMC 仿真优化等技术,进一步提升电磁兼容性能,推动内置驱动板在工业、车载、智能家居等领域的广泛应用。

审核编辑 黄宇

-

emc

+关注

关注

177文章

4465浏览量

192369 -

无刷电机

+关注

关注

60文章

997浏览量

49705 -

驱动板

+关注

关注

21文章

293浏览量

33655 -

电磁兼容设计

+关注

关注

2文章

58浏览量

14273

发布评论请先 登录

高集成度无刷电机内置驱动板硬件电路与控制技术

电磁兼容与电磁干扰在电磁兼容性大数据分析中的智能管理系统

产品接地设计与 EMC 分析:打造电磁兼容的坚实基础

无刷电机内置驱动板 EMC 电磁兼容设计与降噪技术

无刷电机内置驱动板 EMC 电磁兼容设计与降噪技术

评论