上一篇我们给出了四个验证标准:

2. 能否将芯片-封装-板级放在同一环境协同仿真

3. 统计法和瞬态法两条路径是否同时支持

4. 全流程能否在一个平台内完成

最后留了一个问题:四个标准同时达标,市面上有没有这样的工具?

这篇来回答。

标准一:更高精度的备用路径

SIDesigner 的精度底座是自主研发的SIDCore 引擎,在统计通道仿真之外,内置 True-SPICE 路径作为高精度备选方案。

IBIS 宏模型适合快速仿真,但当结果落在裕量边缘、或者需要在极端 PVT corner 下做确认时,IBIS 的近似误差可能已经超过设计裕量本身的范围。SIDCore 的 True-SPICE 路径在时域内直接对通道进行高保真仿真,不依赖宏模型的线性化近似,时域仿真精度与业界 Golden 标准完全对标,可作为统计法结果的精度基准。

两条路径可以在同一个环境内切换:常规迭代用统计通道仿真保持效率,结果存疑时切换到 True-SPICE 路径做精度确认。不需要换工具,不需要重新建模。

标准二:芯片-封装-板级协同仿真

这是 SIDesigner 从立项之初就主打的定位:一站式从芯片、封装到系统的 SI/PI 仿真签核平台。

具体实现上,SIDesigner 支持在同一仿真环境内整合芯片 IO 模型、封装寄生参数与 PCB 传输线——三层结构同时纳入,耦合效应在系统层面完整保留,而不是分开仿真后再叠加。

封装的寄生电感与芯片 I/O 驱动能力之间的相互作用、PCB 阻抗不连续在封装引脚处产生的反射,这些系统级效应在 SIDesigner 的协同仿真环境里都可以被直接捕捉到。

适用于 DDR5、HBM3、UCIe 等对系统级精度要求严格的高速并行接口,以及 PCIe、USB4、XSR 等串行接口场景。

标准三:统计法和瞬态法同时支持

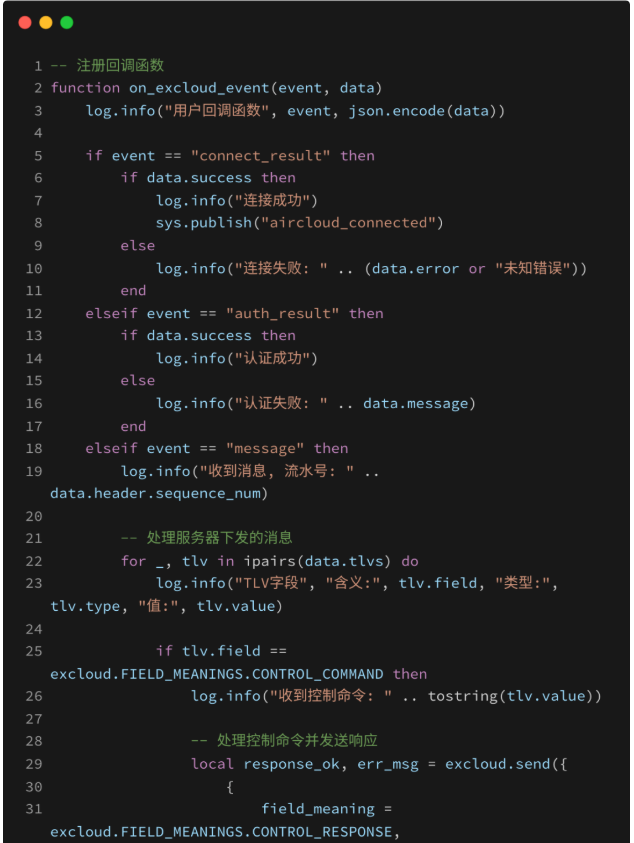

SIDesigner 的核心是SIDCore,同时内置两条仿真路径:

· Channel Simulation(统计通道仿真):快速完成大量参数扫描,适合设计前期快速迭代;SerDes 通道仿真精度与业界 Golden 标准完全对标

· True-SPICE:时域精度仿真,时域仿真精度与业界 Golden 标准完全对标,适合裕量确认和非线性场景兜底

上一篇我们给出了具体数据:同一 DDR 接口 EQ 场景下,统计法(Statistical BER 1e-6)算出的眼宽是 260ps,瞬态基准(Long Transient)是 362ps,差距 28%——足以让 Signoff 结论从"过"变成"不过"。

SIDCore 的解法不是二选一,而是让两条路径共存:统计法跑不准的场景(比如 DFE 等非线性均衡),可以直接切换到瞬态路径做精度兜底,而不是只能继续相信一个系统性偏低的结果。

▲SIDCore 双引擎:Channel Simulation 与 True-SPICE 两条路径共存,按场景切换

标准四:全流程在一个平台内完成

从 AC 分析、通道仿真、瞬态仿真,到系统级参数验证、眼图后处理、批量 DOE 扫描,SIDesigner 在统一平台内完成全流程,不需要在多个工具之间来回切换。

这不只是使用便利的问题。数据在工具间传递时,格式转换和参数设置不一致本身会带来误差——这种误差往往比工具本身的精度差异更难被发现和排查。全流程在同一环境内,这一类隐性误差被从源头消除了。

在效率层面,SIDesigner 在部分场景可将工程师验证效率提升 10 倍以上。

支持脚本定制与主流设计工具集成,可融入已有的设计验证流程。

两个方向的实际验证

DDR 接口 DFQ 优化

上一篇给出了具体数据:某头部存储芯片公司使用 SIDesigner 内置的 DFQ(Design For Quality)模块对 DDR 接口做多参数协同寻优,缺陷率从13.8% 降到 7.6%,眼高和眼宽几乎没有损失。(详见上一篇)

SerDes 高速接口 RSFEC BER 仿真

随着信号速率迈向 56/112/224G,PAM4 信号叠加 DFE 均衡后误码传播效应显著,单靠链路预算已经难以准确预测系统级性能——RSFEC BER 仿真成为这类场景下不可绕开的验证环节。

SIDesigner 支持完整的 RSFEC BER 仿真流程,可对 KP4、KR4 等主流 FEC 配置下的均衡前后性能做定量预测。某头部 IC 设计公司的实际验证结果:SIDesigner 的仿真结果与理论预期在全 Pre-FEC BER 范围内高度吻合,为高速 SerDes 链路的 Signoff 决策提供了可靠的仿真依据。

▲ Pre-FEC BER vs Post-FEC BER:SIDesigner 仿真结果(点)与理论预期(曲线)高度吻合,覆盖 KP4/KR4 两种 FEC 配置

第三方验收结论

某头部芯片设计公司按照标准的 Benchmark 框架对 SIDesigner 做了完整评估,从精度和功能两个维度分别给出结论:

精度验证

·在存在 TX 抖动放大的复杂场景下,SIDesigner 统计眼图算法与 Golden 工具仿真结果高度一致

·在负眼高场景下,SIDesigner 通过完整保留原始数据(无截断处理),输出结果与 Golden 工具完全一致

功能验证

·具备完整的抖动放大建模与仿真能力

·负眼高计算结果连续性完整,无截断导致的偏离

·核心指标与 Golden 工具高度对齐

综合验收结论

SIDesigner 的统计眼图算法在精度和功能两方面均达到验收要求,符合评估标准,可正式投入应用。

对比测试中,另一款同类商业工具在 TX 抖动放大场景直接显示「不支持」。

如果你正在评估 DDR5、HBM3 或其他高速接口的 SI 仿真工具,或者想用你的具体项目场景测一测这四个标准,欢迎扫描下方二维码,填写需求,我们安排技术工程师做一对一演示。

-

仿真

+关注

关注

55文章

4543浏览量

138717 -

信号完整性

+关注

关注

68文章

1501浏览量

98287 -

SPICE

+关注

关注

6文章

200浏览量

44724

原文标题:信号完整性仿真工具选型:SIDesigner 四个核心能力的实战验证

文章出处:【微信号:巨霖,微信公众号:巨霖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

巨霖科技荣膺2026中国IC设计成就奖之年度技术突破EDA公司

巨霖科技PanosSPICE仿真平台的核心技术亮点

PCBA生产过程的四个主要环节?

AirCloud平台+excloud扩展库:核心功能实战应用!

合科泰MOSFET选型的四个核心步骤

巨霖科技荣获2025上海最具投资潜力50佳创业企业

巨霖科技分享国产SI仿真工具的破局之道

巨霖科技荣获2025湾芯奖技术创新奖

【直播预告】10月14日 本周二晚8点|睿擎平台首场实战直播:从快速上手到实现远程监控网关

巨霖科技荣获安永复旦2025最具潜力企业奖

【直播预告】10月14日晚8点|睿擎平台首场实战直播:从快速上手到实现远程监控网关

巨霖科技乔迁仪式隆重举行

基于巨霖SIDesigner实现PCIe仿真的步骤

巨霖科技高速信号仿真平台SIDesigner支持DFQ功能

巨霖科技SIDesigner平台四个核心能力的实战验证

巨霖科技SIDesigner平台四个核心能力的实战验证

评论