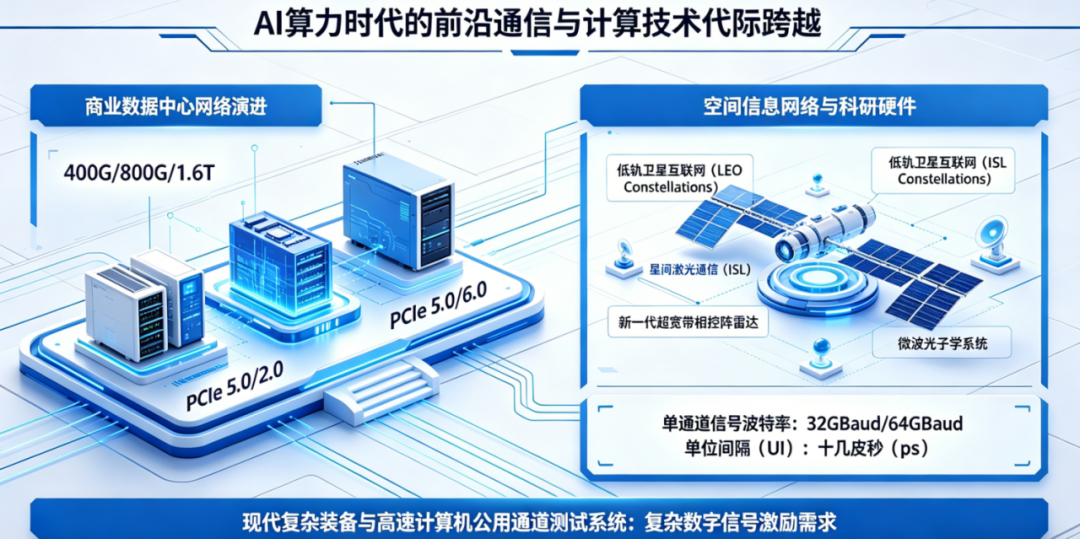

在当今由 AI 算力爆发的时代,前沿通信与计算技术正经历着深刻的代际跨越。一方面,商业数据中心网络正向 400G/800G 甚至 1.6T 演进,计算总线加速向 PCIe 5.0/6.0 迭代;另一方面,以低轨卫星互联网(LEO Constellations)、星间激光通信(ISL)为代表的空间信息网络,以及新一代超宽带相控阵雷达和微波光子学系统,正推动着国防与科研领域的物理层硬件向着极高频段与超大带宽挺进。

无论是 AI 服务器内部的互连,还是跨越数千公里的星地链路,单通道信号的波特率都已逼近甚至突破 32GBaud 乃至 64GBaud,单位间隔(UI)被无情压缩至十几皮秒(ps)量级。现代复杂装备与高速总线的测试系统,正面临着极其苛刻的复杂数字信号激励需求。

当今高速应用的发展趋势

及数字激励生成的挑战

在追求极致互连带宽与超大探测容量的驱动下,无论是商用通信还是国防电子,其底层架构都在发生根本性的物理层变革。这种变革不仅体现在调制格式的不断升级(从 NRZ 到 PAM4,再到相干 DP-QAM),更体现在系统架构向“空间换时间”的并行多通道以及精密相位控制方向全面转移。

针对不断涌现的高速数字总线测试,使用传统的RF模拟信号源来替代参考时钟源的问题逐渐显现。 首先是虽然RF信号源本身的相噪性能优越,但是由于输出是正弦波,对于一个数字系统输入,会产生由于信号斜率导致的额外抖动。 所以几乎最新的芯片参考时钟都明确要求尽量用真实的方波信号作为参考时钟输出, 另外多数参考是时钟要求差分信号。参考时钟和PLL作为一个高速系统的心脏,需要对参考时钟进行精确的恶化来模拟真实世界复杂环境。 这个就明确需要注入模拟相噪恶化的随机抖动以及模拟电源或者其他时钟域干扰的周期抖动。

在企业研发与高校重点实验室中,下面是四个前沿领域的时序同步与多通道激励的应用场景:

数字激励需求与传统测试仪器的局限

数字激励源典型应用场景

为了完整验证 DUT 在极限条件下的容限能力,工程师在搭建验证平台时,往往面临以下三大激励源应用:

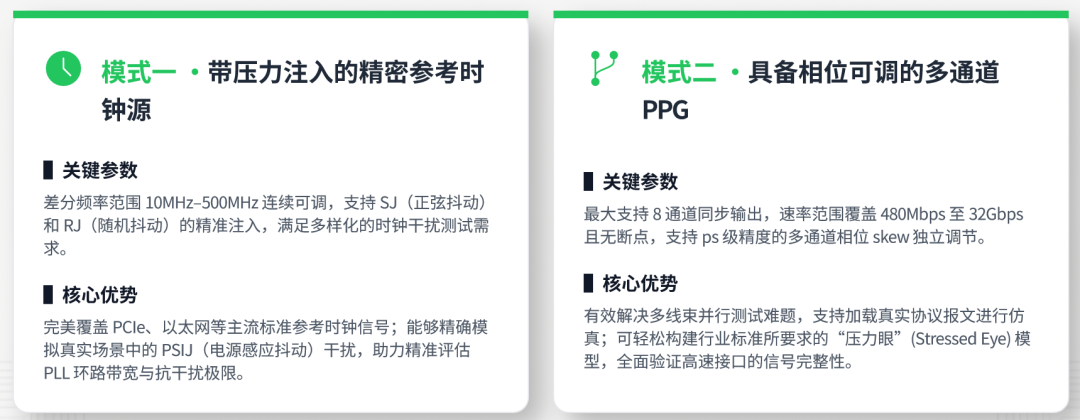

可控恶化的参考时钟(Reference Clock):无论是高速接口芯片还是FPGA/SOC/ASIC芯片,其内部锁相环(PLL)对参考时钟质量极为敏感。测试不仅需要极低相位噪声的高频时钟,更要求能够精确、定量地注入随机抖动(RJ)和正弦抖动(SJ),以模拟电源分布网络(PDN)噪声(PSIJ)或参考时钟链路的劣化。

多通道数字激励输出,并且需要通道间相位可调:多通道总线(如 4-lane 或 8-lane 结构)要求数据源不仅具备极低的本底抖动,还必须能够实现皮秒(ps)级通道间相位偏斜(Skew)调节。

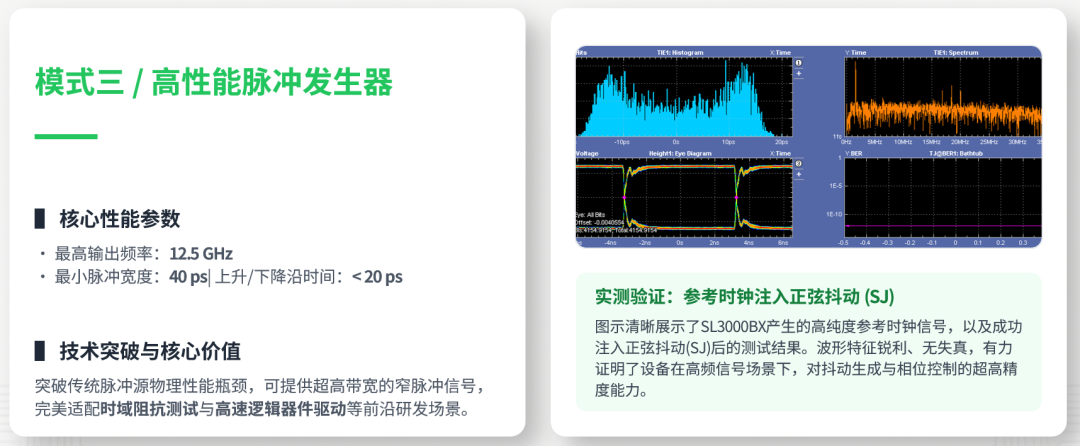

高速窄脉冲激励:在进行接收机建立/保持时间(Setup/Hold Time)测试、或者驱动超高速光电器件(如电光调制器)时,需要具备极快上升沿(<20ps)和极窄脉宽(<40ps)的脉冲源。

用分离的不同仪器构建数字

和时钟激励源的局限性

测试环境搭建复杂:传统的测试台架通常采用离散仪器拼接方案——由独立的模拟信号源,任意波形发生器(AFG/AWG)、专用脉冲发生器(Pulse Generator)、独立时钟综合器(Clock Synthesizer)和外置抖动干扰源通过射频线缆、功分器和混频器组合而成。

仪器间时基漂移:不同仪器依赖各自内部的晶振或外部 10MHz 参考锁相环。受限于温漂和锁相环带宽,仪器间存在固有的、不可预测的低频相位漂移,使得精确的皮秒级相位调整和稳定性变的异常困难。

抖动注入的不可控性:外部注入抖动往往需要经过混频器或外部调制的信号源或者函数发生器输入端叠加,链路插入损耗,难以精确校准注入量,复现度极低。

模拟信号源和数字激励源的区别:独立的模拟信号源能够输出非常纯净的周期信号,相位噪声低,频率范围也非常大,例如中星联华的模拟信号源可以支持到67GHz。 但是模拟源或者矢量信号源的输出存在2个明显的不足,首先输出的是正弦信号,导致上升时间和下降时间非常慢。 另外输出的场景多为单端输出,即便外置巴伦也会导致受限于巴伦的相频特性和Skew偏差。 在一个高速的数字系统中,绝大多数要求的是上升/下降时间陡峭的方波差分信号。 而模拟信号源用作时钟的时候会导致时域测试的抖动分量过大。

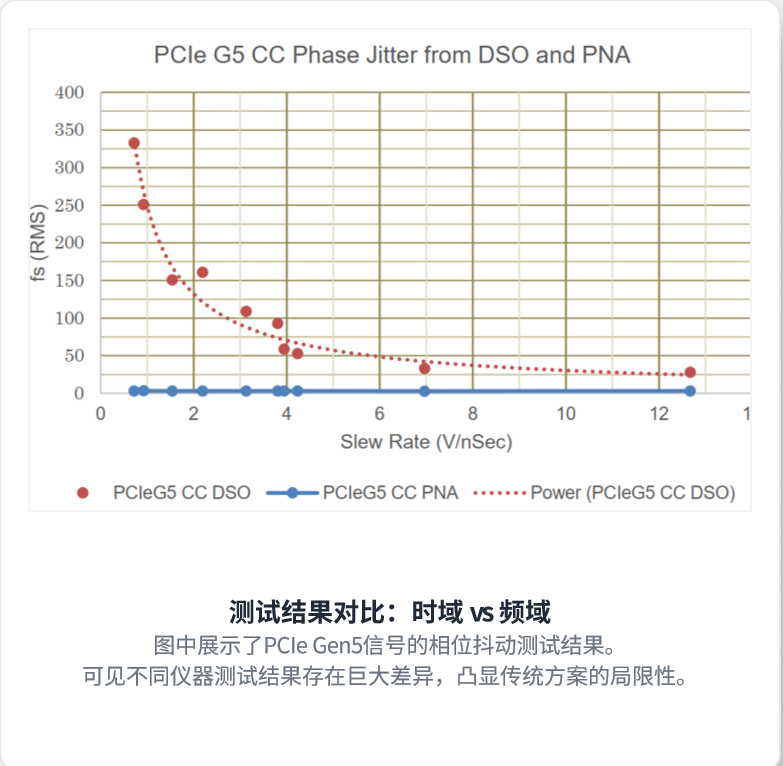

下图是一个参考时钟用不同的仪器测试得到结果的巨大差别。主要是对比了相噪分析仪和实时示波器的差别。 对于一个时域的电路,因为相噪仪无法得到输入信号的斜率信息,实时示波器测试最全面时间和斜率, 在一个时域被测DUT的接收机也会被看到,所以首选时域的示波器进行测试。

下图是针对同一个时钟信号,当斜率不同的时候,用实时示波器和相噪仪测试的结果对比。 可见当时钟的斜率过慢的时候,会导致测试的抖动值非常大,而这个由于斜率导致的抖动无法满足DUT被测电路的要求,所以推荐用数字激励源来构建测试环境。

误码仪能力的扩展:

从单一测误码到“多域激励源”

为了解决多通道皮秒级相位控制与 Skew 容限评估的难题,测试测量仪器的底层架构必须发生根本性的转变。现代高性能误码仪(BERT)早已打破了仅限于发送 PRBS 码流的固化定位,演进为具备统一高精度时基的多通道融合数字激励中心。

在这种先进的测试架构中,所有的高速数据通道(PPG)、时钟输出以及脉冲信号,均由仪器内部同一个超低相噪的时钟综合器网络驱动。这种设计从根本上消除了仪器间的温漂与时基漂移。更关键的是,其在数字底层集成了精密的高频移相器或高级抖动和相噪恶化的设计,实现了对各个输出通道之间相位的独立、连续且高分辨率的滑动调节。

以中星联华(Sinolink)推出的 SL3000BX 高性能误码仪为例,其硬件底层与算法架构在设计之初,就专门针对多通道数据、时钟和脉冲输出的应用模式进行了深度优化。工程师可以一机多用,在一个高速系统中,产生参考时钟、高速时钟或多通道数据,全方位摸底 DUT 的时序容限极限。

误码仪作为多域激励源的典型应用

下面是基于多域数字激励源的物理层测试应用的一些典型实例

SL3000BX 作为数字激励源

的三大工作模式与特点概览

针对上述复杂的测试需求,中星联华 SL3000BX 高性能误码仪作为集成化多域激励中心的代表,提供了三种独立且高性能的输出模式。

下图是SL3000BX的多通道输出相位可调的数字激励源图例。

总结

在由 AI 算力集群、光电共封装(CPO)和下一代雷达传感驱动的“超宽带”时代,物理层通信的测试痛点已从单一的“信号速率”向“多维度的信号完整性压力测试”转移。传统的离散化测试工具已无法胜任前沿物理边界的探索,测试台架自身引入的不确定度,往往超过了被测芯片本身的性能极限。

面对相干光 IQ 校准、ADC 交织杂散定位、SerDes 容限描绘以及相控阵列驱动等严苛挑战,以中星联华 SL3000BX 为代表的融合共基时架构误码仪,正是为解决这些应用痛点而设计。能够在研发最早期帮助用户评估被测DUT在各种压力下的表现和性能,全面摸底硅光、DSP 与超高速模拟射频集成电路的潜能。

-

超宽带

+关注

关注

1文章

256浏览量

24430 -

时钟源

+关注

关注

0文章

114浏览量

16834 -

误码仪

+关注

关注

0文章

17浏览量

10814

发布评论请先 登录

ADRF5714:超宽带1位数字衰减器的卓越之选

IDT ICS664 - 01数字视频时钟源:高清电视数字视频设备的时钟解决方案

IDT ICS664 - 03数字视频时钟源:设计与应用详解

IDT ICS664 - 02 PECL数字视频时钟源:高清电视数字视频设备的理想之选

Renesas ICS660数字视频时钟源:设计与应用详解

探索 RENESAS ICS664 - 01 数字视频时钟源:特性、应用与设计要点

探索 RENESAS ICS664 - 02 PECL 数字视频时钟源

是德科技推出全新多通道误码仪FITS-8CH

RENESAS ICS664 - 02 PECL数字视频时钟源:高清电视时钟解决方案

探索源仪电子数字功率计的技术优势

ADM-10701PSM超宽带低噪声放大器Marki

艾德克斯IT2700多通道源载模组系统再添低压大电流新成员

Analog Devices Inc. AD-SYNCHRONA14-EBZ多通道时钟器件特性/应用/框图

超宽带时代,误码仪在多通道数字激励源和时钟源的应用

超宽带时代,误码仪在多通道数字激励源和时钟源的应用

评论