基于xilinx k7 325t实现的千兆网udp协议,只需要设置好IP,端口,就可以直接给数据,基本等同于透传,可以不用管底层协议。 可以 # FPGA 实现udp模块说明 ## udp_protocol_top gig_ethernet_pcs_pma有脚本生成,任何版本vivado都可以支持,注释里面有对重要信号的说明,默认是1000M,100M需要改内部信号,PHY芯片是88E1512,SGMII接口。 FPGA和上位机IP,端口都要设置好才能收到数据,注意在同一个网段 ## 接收数据 udp_protocol_top.rx_udp_payload_axis_tvalid拉高的时候就代表udp_protocol_top.rx_udp_payload_axis_tdata有效,udp_protocol_top.rx_udp_payload_axis_tready默认给1可以一直收数据 ## 发送数据 tx_udp_payload_axis_tready=1的时候拉高tx_udp_payload_axis_tvalid,数据才有效,发送完成以后一定要发送一个tx_udp_payload_axis_tlast脉冲指示最后一个数据

最近在项目中基于 Xilinx K7 325t 完成了千兆网 UDP 协议的相关实现,感觉挺有意思,来和大家分享下。

这个实现基本就像是透传一样,只要设置好 IP 和端口,就能直接给数据,底层协议不用我们太操心。

FPGA 实现 udp 模块说明

udp_protocol_top

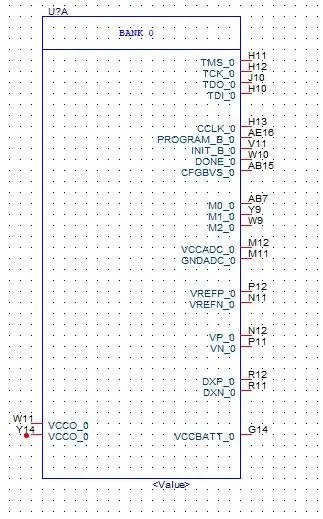

这里面的 gigethernetpcs_pma 是通过脚本生成的,而且不管啥版本的 Vivado 都能支持它,这点还是挺方便的。在代码注释里对重要信号都有说明,默认情况下是 1000M 的速率,如果要改成 100M 的话,就得改改内部信号。这里用的 PHY 芯片是 88E1512,采用的是 SGMII 接口。

在实际应用中,FPGA 和上位机的 IP 以及端口都得设置好,而且要注意在同一个网段,不然数据可收不到哦。

基于xilinx k7 325t实现的千兆网udp协议,只需要设置好IP,端口,就可以直接给数据,基本等同于透传,可以不用管底层协议。 可以 # FPGA 实现udp模块说明 ## udp_protocol_top gig_ethernet_pcs_pma有脚本生成,任何版本vivado都可以支持,注释里面有对重要信号的说明,默认是1000M,100M需要改内部信号,PHY芯片是88E1512,SGMII接口。 FPGA和上位机IP,端口都要设置好才能收到数据,注意在同一个网段 ## 接收数据 udp_protocol_top.rx_udp_payload_axis_tvalid拉高的时候就代表udp_protocol_top.rx_udp_payload_axis_tdata有效,udp_protocol_top.rx_udp_payload_axis_tready默认给1可以一直收数据 ## 发送数据 tx_udp_payload_axis_tready=1的时候拉高tx_udp_payload_axis_tvalid,数据才有效,发送完成以后一定要发送一个tx_udp_payload_axis_tlast脉冲指示最后一个数据

下面简单看一下代码结构(这里只是示意,非完整代码):

module udp_protocol_top ( // 各种信号声明 input wire clk, input wire rst, // 与千兆网相关信号 wire [31:0] gig_ethernet_pcs_pma_sig, // 接收数据相关信号 output wire rx_udp_payload_axis_tvalid, output wire [63:0] rx_udp_payload_axis_tdata, input wire rx_udp_payload_axis_tready, // 发送数据相关信号 input wire tx_udp_payload_axis_tvalid, input wire [63:0] tx_udp_payload_axis_tdata, output wire tx_udp_payload_axis_tready, output wire tx_udp_payload_axis_tlast ); // 这里面会实例化 gig_ethernet_pcs_pma 模块 gig_ethernet_pcs_pma#( .PARAM1(VALUE1), .PARAM2(VALUE2))u_gig_ethernet_pcs_pma ( .clk(clk), .rst(rst), .sig(gig_ethernet_pcs_pma_sig) ); // 其他逻辑代码,比如数据处理,UDP 协议相关逻辑等 endmodule

这里面gigethernetpcspma模块负责和千兆网物理层相关的处理,而udpprotocol_top模块则在这个基础上完成 UDP 协议相关的数据收发等功能。

接收数据

在接收数据的时候,当udpprotocoltop.rxudppayloadaxistvalid拉高,就意味着udpprotocoltop.rxudppayloadaxistdata里面的数据是有效的。而udpprotocoltop.rxudppayloadaxistready这个信号默认给 1 的话,就能一直接收数据啦。

从代码逻辑上看,就像下面这样:

always @(posedge clk or posedge rst) begin

if (rst) begin

// 复位相关信号

end else begin

if (rx_udp_payload_axis_tvalid && rx_udp_payload_axis_tready) begin

// 处理接收到的数据,比如存入缓存等操作

received_data <= rx_udp_payload_axis_tdata;

end

end

end

上面这段代码就是当接收数据有效且接收准备好的时候,把接收到的数据存到received_data这个变量里(实际应用可能会更复杂,比如存入 FIFO 等)。

发送数据

发送数据也有讲究,当txudppayloadaxistready=1的时候,拉高txudppayloadaxistvalid,这时的数据才有效。而且在发送完成以后,一定要发送一个txudppayloadaxistlast脉冲来指示这是最后一个数据。

看下面这段代码示例:

reg [63:0] data_to_send;

reg send_data;

always @(posedge clk or posedge rst) begin

if (rst) begin

send_data <= 0;

end else begin

if (some_condition) begin // 这里 some_condition 代表发送数据的条件,比如缓存有数据等

send_data <= 1;

data_to_send <= some_data; // some_data 是要发送的数据

end

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

tx_udp_payload_axis_tvalid <= 0;

tx_udp_payload_axis_tlast <= 0;

end else begin

if (send_data && tx_udp_payload_axis_tready) begin

tx_udp_payload_axis_tvalid <= 1;

tx_udp_payload_axis_tdata <= data_to_send;

if (is_last_data) begin // is_last_data 代表是否是最后一个数据的判断

tx_udp_payload_axis_tlast <= 1;

end

end else begin

tx_udp_payload_axis_tvalid <= 0;

tx_udp_payload_axis_tlast <= 0;

end

end

end

在这段代码里,当满足发送条件somecondition时,准备好要发送的数据datatosend并拉高senddata。然后当txudppayloadaxistready为 1 时,发送数据,并在判断是最后一个数据时,拉高txudppayloadaxistlast。

总的来说,基于 Xilinx K7 325t 实现的这个千兆网 UDP 协议模块,虽然功能类似透传,但在数据收发的细节处理上还是有不少需要注意的地方,希望我的这些分享能给大家带来一些帮助和启发。

-

FPGA

+关注

关注

1664文章

22504浏览量

639300 -

Xilinx

+关注

关注

73文章

2208浏览量

131908 -

UDP协议

+关注

关注

0文章

71浏览量

13770 -

千兆网

+关注

关注

0文章

37浏览量

9995

原文标题:基于 Xilinx K7 325t 的千兆网 UDP 协议实现小记

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

K7 325T 的 SRIO核 有哪位用过啊?

基于Xilinx Kintex-7 FPGA K7 XC7K325T PCIeX8 四路光纤卡

请教一个关于Xilinx pcie的问题

233-基于TMS320C6678+XC7K325T的CPCIe开发平台

237-基于Xilinx Kintex-7 XC7K325T 的FMC/千兆以太网/SATA/四路光纤数据转发卡

基于TI DSP TMS320C6657、XC7K325T的高速数据处理核心板 解决法案

与PCI Express端点相关的定时故障,K7 325T与160T相关

Xlinx K7 千兆网口数据传输项目请大神出手搭救,急急急!

JFM7K325T的JTAG识别连接问题

325T/410T PCIe2.0×8千兆网 信号处理设计

Xilinx A7 K7 V7系列Cadence符号库及PCB库免费下载

6678板卡设计原理图:基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速数据处理核心板

基于Xilinx K7 325t的千兆网UDP协议实现小记

基于Xilinx K7 325t的千兆网UDP协议实现小记

评论