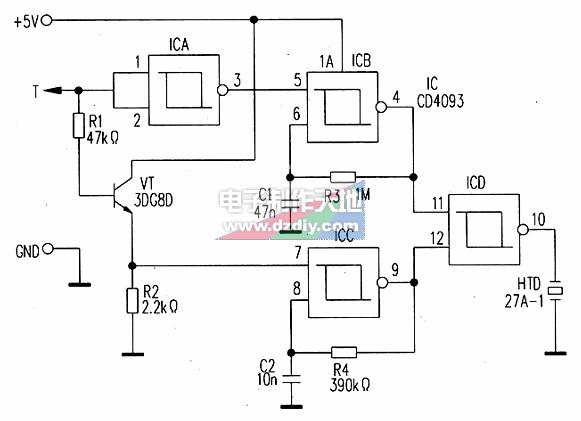

关键字:CD4093,逻辑测试电路

电路如图所示。由4个二输出端与非门,一只晶体管组成,并采用压电陶瓷蜂鸣器发声,根据音调不同判断被测逻辑状态。

电路原理:电路中由与非门ICB、R3、C1组成“0”振荡器,与非门Icc、H4、C2组成“1”振荡器,R3、C1或R4、C2取值不同时,振荡器的频率也不同。ICB的⑤脚和ICC的⑦脚是控制端,加高电平“1”时振荡器工作,输出矩形波。该逻辑笔的检测状态为:(1)当探针T未检测或检测到“悬空”状态时,I—CA输出“0”(一般认为逻辑门输入端开路时,输入为“1”)。同时VT截止,ICC的⑦脚被R2下拉为“0”,“0”振荡器和“1”振荡器均停振,ICD无输出,蜂鸣器HTD不发声:(2)当探针T检测到“0”时,VT截止,Icc的⑦脚为“0”,“1'’振荡器不工作。同时,“0”信号经ICA反相后使ICB的⑤脚为“1”,“0”振荡器起振,产生较低频率(以200Hz~600Hz为宜)的矩形波振荡信号,通过ICD驱动HTD发出低频鸣响;(3)当探针T检测到“1”时间,经ICA反相使ICB的⑤脚为“0”,“0”振荡器不工作,此时VT导通,Icc的⑦脚为“1”,“1”振荡器起振。以1000Hz-1500Hz为宜的振荡信号,经ICD驱动HTD发出高频鸣响:(4)当探针T检测到“CP”脉冲时,相当于“0”、“1”交替输入,“0”振荡器和“1”振荡器轮流输出,HTD产生高、低频率的混合鸣响。 元件选用:ICA—ICD选用带施密特触发器的二输入端与非门集成电路CD4093,其内含有4个二输入端与非门,故可满足要求。VT选用3DG8D.取β=80~120,HTD使用27A-1型压电蜂鸣器,图中的+5V、GND分别接被测电路的电源和地。

作者:沈左

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

热点推荐

连接器-TERM-50W-183S+ Mini-Circuits RF端接器

and partners like family. 20,000+ customers prefer Mini-Circuits for the demanding quality standards

发表于 11-26 11:39

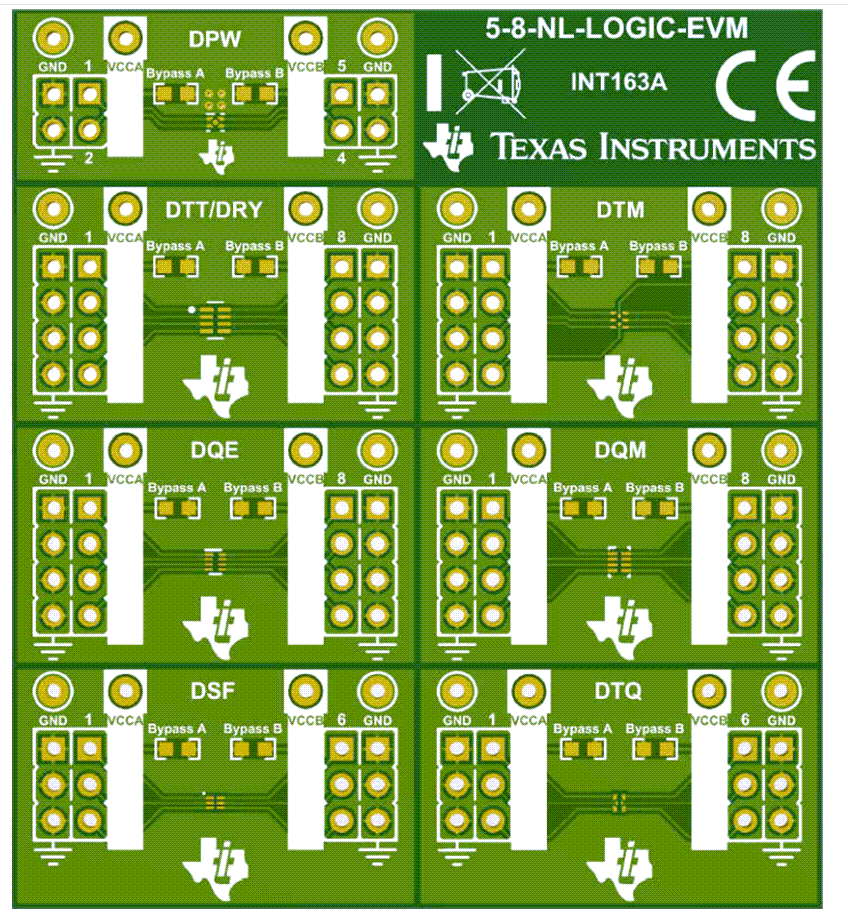

Texas Instruments 5-8-NL-LOGIC-EVM逻辑转换评估模块技术解析

Texas Instruments 5-8-NL-LOGIC-EVM逻辑和转换评估模块 (EVM) 设计用于支持任何逻辑或转换器件。它支持DTT (X1QFN-8)、DRY (USON-6)、DPW

环保与效能兼备:永铭超级电容SDS/SLX系列改写电子笔市场

关于电子笔随着科技的进步,电子笔逐渐成为教育、设计和商务等多个领域的重要工具。永铭推出了超级电容器SDS系列超小型电容器(EDLC)和SLX系列超小型电容器(LIC),这些产品因其尖端技术和优异性

频率扩频设计的关键参数

,以分散频谱中的噪声能量,从而降低EMI噪声频谱峰值,满足汽车、工业等场景的严苛标准。接下来,我们来一起探讨频率扩频设计中的参数选择逻辑及其实际应用。

基于BLE技术 智能手写笔解决方案:改变你的书写体验PTR5415

方案说明:

我们的智能手写笔方案基于BLE技术,利用蓝牙低功耗连接手写笔与移动设备(如智能手机、平板电脑)之间的无线通信。可以实时将书写数据上传到手机APP及云端,及时有效的对书写数据进行存档及管理

发表于 03-11 17:50

STM32G070配置为主机只接收模式,并开启CRC功能,发现波形会多读一笔数据,为什么?

配置为主机只接收模式,并开启CRC功能,发现波形会多读一笔数据,调试看代码确实多读了一笔,这里是不是一个bug?

if (hspi->Init.CRCCalculation

发表于 03-10 07:29

Display下面测试Test模式出错的原因?

Display下面测试Test模式。如Test模式SET会报I2C错误。Splash Images里面set。第一次会闪一下就黑了。再点set就报I2C错误

发表于 02-26 06:36

【米尔-Xilinx XC7A100T FPGA开发板试用】Key-test

硬件:

一Xilinx XC7A100T FPGA开发板

二12V电源适配器

三下载器

四 win10笔记本

软件:

一Vivado (指导手册有详细的安装下载流程)

二官方按键示例工程

按键示例

发表于 01-09 16:08

OLED笔电渗透率将逐年提升

近日,根据TrendForce集邦咨询的最新OLED技术及市场发展分析报告,OLED笔记本电脑(笔电)的市场渗透率预计将在未来几年内稳步增长。其中,由于中国大陆笔电品牌的大规模采购,2024年

PADS逻辑教程

PADSlogic9.6电路图设计资料手册(中文教程)为motor Graphics公司软件提供的原本中文手册,用于PADSlogic软件电路图设计参考使用。PADS Logic用户界面旨在提高

发表于 12-16 14:33

•1次下载

频率逻辑笔,Logic test circuits

频率逻辑笔,Logic test circuits

评论