作者:Reuben George

市场背景

当今,物联网(IoT)已对所有行业产生了影响,而且有望到2020年成为一个1.7万亿美元的市场。IoT领域建立在云计算以及由移动、虚拟和即时连接搭建的数据采集传感器网络的基础之上。行业专家认为,它将让我们生活中的一切变得更加“智能”。IoT已经渗透至各行各业:从工厂自动化到点播娱乐和可穿戴设备。但在大多数情况下,这个庞大的智能设备互联系统在改变我们的工作方式方面还未充分发挥其全部潜能。

IoT无疑是推动半导体行业和嵌入式系统发展的新动力。它的诞生推升了市场对众多新使能技术的需求,其中包括:

-

新一代超低功耗IC

-

全新的无线通信协议

-

分析及云计算用高级数据处理技术

随着芯片朝着更小尺寸的工艺节点迈进,此前相对不引人注目而现在变得愈发显眼的一个半导体细分市场就是存储器。物联网及其艾字节数量级的数据流量正在推升市场对高性能、低功耗、超小封装的存储器的需求。IoT对半导体-尤其是存储器的-强加的另一个约束就是安全性和可靠性要求。大量隐私信息将被存储在可穿戴设备、服务器和其它物联网节点上。

过去十年来,存储器领域被分为两个截然不同的产品家族:即快速和低功耗存储器,每个都有其自身的特性、应用和定价。只要愿意牺牲功耗甚至尺寸,OEM就能找到高速度性能的存储器产品。对于需要低功耗的易失性和非易失性存储器而言,反之亦然。

但是,IoT 改变了市场对存储器的要求。现在的需求是高性能、低功耗器件。这些器件被要求能够使用便携式电源执行复杂的运算。它们还必需尽量缩减引脚数量和外形尺寸。通过内置深度关机、深度睡眠等低功耗模式,同时提供一代高于一代的性能(即时钟频率和特性集),微控制器已可以满足这些要求。为了与微控制器保持同步,存储器一定不能让设计人员担忧性能和功耗之间的取舍。

本文将聚焦于存储器在已受IoT影响的一个领域―零售购物领域中的发展趋势。在借助IoT给消费者带来便利方面,这个2万亿美元的市场蕴含着巨大潜力。零售是世界上竞争最为激烈的行业之一,数百万个零售商争夺一个成熟客户群,因此利润率很低。大型商场已经开始利用物联网吸引客户,为他们提供个性化购物体验。零售商正在整合商场中的所有设备、公司总部云端资源。最终目标是一个互联商场,它能够利用所采集的数据进行促销、打造客户忠诚度、管理库存和提升运营效率。

当今的消费者正在广泛使用互联网影响他们的购物决策:从研究产品到网上购物再到评论产品。在利用互联网进行购物方面,零售商已经落后于消费者。为了跟上消费者的步伐,零售商正在关联零售的物理和在线层面,从而让每一次互动都有回报,以便让他们的商场变得更加“智能”。

智能POS终端

IoT已给零售领域带来的一个显著影响就是智能销售点(POS)终端。POS终端在某种意义上就是零售商使用IoT的中心节点。很多领先的“智能”商场利用POS数据了解客户的购物趋势,实时追踪库存,并帮助在线购物者准确确定产品的本地存货情况。它们还能帮助零售商根据客户购买特定物品的频率为他们提供定制建议。

为了追踪购物者的购物统计数据,智能POS终端需要连接扫描仪。这意味着智能POS终端必须处理数倍于传统POS终端所处理的数据。很多最新型号的智能POS终端采用了主频达到Ghz级别的最新的ARM处理器。与此同时,这些终端大多是由电池供电的便携式设备,换句话说,这些系统需要尽可能地少用电。此外,由于所传输的数据是高度个人化的数据,因此要求最高级别的数据完整性,即需要使用比传统终端更为严格的加密标准。最后,还要采用所有POS终端都采用的标准的故障安全技术(如lockout模式)。

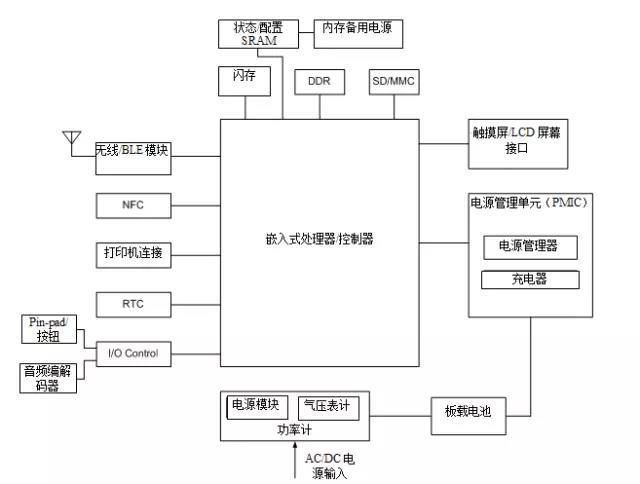

POS终端采用多种类型的存储器:用于非易失性数据存储的闪存,用于高速缓存的DRAM,以及用于微控制器存储扩展和电池备份配置数据日志的SRAM。有时甚至会使用一个外置的MMC。图1显示了一个典型POS终端设计的框图,为了满足智能POS终端的要求,存储器应提供最高的可靠性和足够的带宽。不仅如此,为了满足便携要求,存储器还必须具备低功耗、小尺寸的特点。

过去,存储器的发展一直试图结合快速的存取速度、低功耗和小尺寸特性。但是,随着Octi-SPI、HyperBus™等新一代低引脚数接口的问世,现在出现了能够媲美甚至超过快速存取式存储器的带宽,同时匹敌低功耗存储器的功耗,并使用最低数量的微控制器引脚的存储器。从微控制器传承到SRAM等存储器的另一项创新技术就是引入了深度睡眠模式。例如,赛普拉斯的PowerSnooze™ SRAM就是一种深度睡眠能效媲美Micropower SRAM的Fast SRAM。

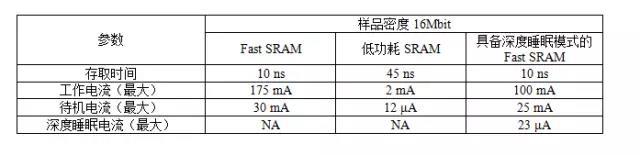

让我们比较一下两种常用SRAM-Fast和Micropower,以及具备深度睡眠模式的Fast SRAM的功耗和存取时间。

通过结合快速存取和深度睡眠特性,这些存储器能够媲美SRAM的速度和低功耗SRAM的能效。在SRAM在大多数时间处于待机状态的应用中,这种结合的优势更加显著。

在使用SRAM记录配置数据的一个典型POS终端中,SRAM的运行时间只占总工作时间的20%。如果这个SRAM是工作电压为3.3V的Fast SRAM,它工作时将消耗120瓦时(WH)的电能,待机时将消耗80 WH的电能,总能耗为200 WH。如果是一个具备深度睡眠模式的Fast SRAM,工作时仍消耗120 WH的电能,但待机时能耗降至0.06 WH,因此总能耗约为121 WH。在这个具体的例子中,深度睡眠选项将能耗降低了40%。

对于一颗240mAH的板载纽扣电池而言,一个处于待机状态的16Mb Fast SRAM将能让电池续航超过12小时,而一个处于待机状态的低功耗SRAM将能让电池续航超过3年,但后者的局限是存储速度较慢。此时,一个具备深度睡眠模式的Fast SRAM与低功耗SRAM相比优势显著,其带宽是后者的4倍多(即10ns存取时间vs. 45ns存取时间),而且没有功耗代价。尽管如此,无论是MCU或SRAM,使用深度睡眠模式时应考虑一个因素:进入和退出深度睡眠模式的时间。如果两个工作周期之间的时间间隔与SRAM进入或退出深度睡眠模式所用时间相比太短,那么这种方法将会无用。例如,对于赛普拉斯出品的具备深度睡眠模式的Fast SRAM而言,这个时间间隔是300 µs(最大)。这可能是推广具备深度睡眠模式的Fast SRAM的最大障碍。

存储器领域的另一个有趣趋势是:随着闪存变得越来越快,对高速缓存的需求正在发生改变。很多需要RAM的微控制器工艺现在可以利用XIP(Execute In Place)在闪存上实现。这意味着RAM越来越多被用于扩展内存或电池系统备份。与此同时,已被运用于这两种应用的SRAM正在增加容量选择。换句话说,传统上首选的DRAM正变得越来越不重要,因为就像容量更大、速度更快、功耗更低的闪存可以满足大型存储的需求那样,容量更高、功耗更低、尺寸更小的SRAM也可以满足小型存储的需求。

其他组件

用于构筑智能购物体验的还有很多其它组件:各种类型的传感器、电子货架标签及信标、存储设备以及用于处理所采集数据的数据处理终端。在一篇文章中探讨所有这些设备的应用和内存需求难度很大。我计划在近期探讨这些设备的内存需求。但是,基本的要求不变,即低功耗、高速、小尺寸和高可靠性。

-

存储器

+关注

关注

39文章

7753浏览量

172164 -

物联网

+关注

关注

2950文章

48108浏览量

418160

发布评论请先 登录

SDRAM工业动态随机存储器在可编程逻辑控制器(PLC)的应用

串行mram磁性随机存储器的工作原理与存储机制

半导体存储器的发展过程和主要分类

VTI低功耗SRAM存储器VTI508HB08

DDR SDRAM是什么存储器(双数据速率同步动态随机存取存储器介绍)

双口SRAM静态随机存储器存储原理

芯源的片上存储器介绍

高速存储器sram,带ECC的异步SRAM系列存储方案

Everspin存储器8位并行总线MRAM概述

华大九天新一代存储器电路特征化提取工具Liberal Mem的核心功能

智能购物系统中的存储器应用

智能购物系统中的存储器应用

评论