说出来你可能不信,很多工程师拿着漂亮的仿真报告,实物一测试,问题全出来了。返工、延期、挨骂,样样都逃不掉。

归根结底,大多数问题都出在仿真方法上。今天就来聊聊信号完整性仿真中,90%的工程师都在犯的几个错误。

错误一:时域仿真和频域仿真傻傻分不清

有些工程师做仿真,要么只跑时域,要么只跑频域,觉得跑一个就够了。这其实是个大坑。

时域仿真告诉你的是:信号长什么样、眼图开多大、有没有出现过冲下冲。就像给你一张照片,能看到表象。

频域仿真告诉你的是:信号在不同频率下的表现、S参数曲线、阻抗匹配情况。这更像是一份体检报告,能看到内在问题。

这俩是互补的关系,缺一不可。时域看结果,频域找原因。比如你看到眼图闭合了,不懂频域分析的话,只能干瞪眼。但跑一下S参数,就能定位是哪个频点出了问题。

正确做法是:两个都要跑,而且要根据信号速率选择合适的仿真范围。比如DDR4跑到了3200Mbps,仿真频率至少要到5GHz以上才有参考价值。再比如现在火热的AI服务器,112G SerDiff链路,仿真频段要到40GHz以上才稳妥。

图1:时域仿真与频域仿真对比

错误二:眼图只盯着开口看

拿到仿真眼图,很多人第一反应就是看眼图开口大不大。开口大就觉得没问题,开口小就觉得要完蛋。实际上,这只是最基础的分析,相当于只看了体检报告上的身高体重。

除了眼高(Eye Height)和眼宽(Eye Width),这几个参数同样重要:

抖动(Jitter):抖得太厉害,接收端很容易采错数据。常见的RJ和DJ要分开看,很多问题出在DJ上。

上升时间/下降时间:边沿太缓,高速信号容易失真。10%-90%上升沿不能超过UI的20%。

眼交叉百分比:偏离50%太多,说明占空比失真严重,接收端时钟恢复会出问题。

眼图模板:有没有触犯模板?触犯了就是硬伤,再好看的眼图也不行。

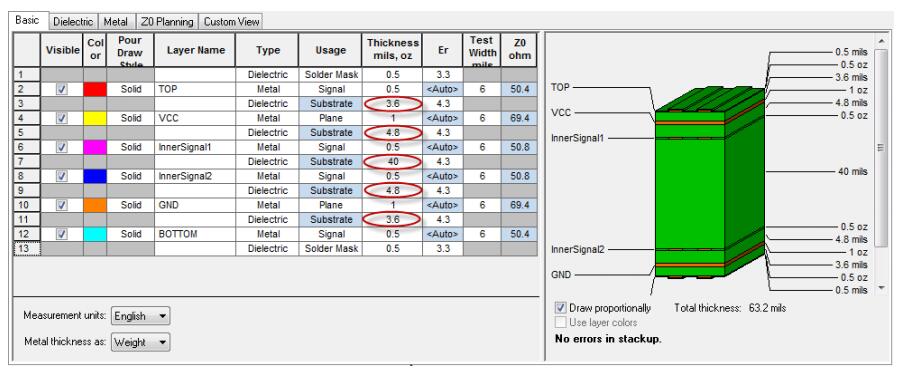

错误三:PDN设计只看电容数量不看阻抗

电源完整性问题,说到底就是PDN(Power Delivery Network)阻抗问题。很多工程师觉得多放几个去耦电容就万事大吉,结果阻抗曲线一拉出来,到处是尖峰,简直不忍直视。

问题出在哪?电容的谐振频率没选对、不同电容并联产生反谐振、布局不合理导致走线电感过大……随便一个都能让阻抗爆表。

AI芯片和先进封装普及后,PDN设计更是难上加难。HBM内存的工作电流动不动几十安培,供电网络的任何一点波动都可能让芯片跑飞。去年某大厂的AI训练卡,就是因为PDN设计没做好,导致批量返修,损失惨重。

去耦电容不是越多越好,而是要对症下药。先算目标阻抗,再选谐振频率合适的电容,最后才是布局优化。

图2:PDN阻抗分析与谐振点识别

错误四:直角走线无所谓

在低速设计中,直角走线确实没什么影响。但一旦跑到高速,毫米波甚至几Gbps的速率,直角拐角就是个定时炸弹。

直角拐角会导致额外的寄生电容,大约增加3-5fF。这个数字看起来很小,但在高频下会让阻抗突变,引发信号反射。反射大了,眼图就闭合了。

更要命的是,这种问题在时域仿真里可能不明显,因为仿真软件的模型精度不够。但实板一测,问题就暴露了。很多工程师吃这个亏,就是仿真没做准。

正确做法是用45度斜角或者圆弧走线,拐角长度要大于等于2倍线宽。差分对更要对称,拐角处要同时转弯,否则会产生skew。

错误五:过孔Stub不当回事

多层板设计中,过孔是必不可少的。但很多人不关心过孔的Stub长度,觉得埋孔藏起来就没事了。

实际上,Stub就像一根天线。信号在传输过程中,部分能量会被Stub反射回来,在眼图上形成"鬼影",严重压缩眼图开口。

在16Gbps以上的高速链路里,Stub的影响就被放大到无法忽视的地步。做过112G PAM4仿真就知道,过孔Stub超过8mil,整个通道的眼图就很难看了。

高速信号走线的Stub要尽量控制在10mil以内,超过这个值就必须做背钻(Back Drill)。在112Gbps PAM4的高速背板上,Stub的影响更是被放大到极致。成本虽然高一点,但总比返工强。

图3:错误设计 vs 正确设计对比

正确的仿真姿势

说了这么多错误用法,顺便讲讲正确姿势:

仿真前先明确信号速率和仿真频段,不要偷懒省范围

时域频域结合分析,互为验证,一个都不能少

眼图参数要全看,不能只盯眼高眼宽

PDN仿真要关注阻抗曲线,避开谐振点

高速走线全程优化,拐角、过孔一个不放过

仿真模型要跟器件厂商要准的,不能用默认参数糊弄

说到底,仿真是个严谨的活儿,不是跑个软件出张图就完事了。要懂得仿真结果的含义,要能看懂曲线的趋势,要能从数据里找出问题所在。

-

仿真

+关注

关注

55文章

4532浏览量

138647 -

信号完整性

+关注

关注

68文章

1494浏览量

98230 -

时域仿真

+关注

关注

0文章

3浏览量

4665

原文标题:信号完整性仿真:90%的工程师都在这5个地方翻车

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电源的信号完整性仿真中 Sigrity电容模型应用与管理指导

信号完整性仿真中容易犯的几个错误

信号完整性仿真中容易犯的几个错误

评论