ICS951462:ATi RS/RD690 系统的可编程系统时钟芯片

在电子设备的设计中,系统时钟的稳定性和精确性对于设备的性能和可靠性起着至关重要的作用。今天我们要探讨的主角——ICS951462,是一款专门为基于 ATI RS/RD690 的系统设计的可编程系统时钟芯片,它能提供所需的各种时钟,为系统的稳定运行提供有力支持。

文件下载:951462AGLFT.pdf

1. 推荐应用与输出特性

ICS951462 主要应用于使用 AMD K8 处理器和 SB600 南桥的 ATI RS/RD690 系统。它具有丰富的输出特性,包括 2 对 CPU 时钟、8 对 SRC 时钟、4 对 ATIG 时钟,还有 1 个 66MHz 的 HyperTransport 时钟种子、2 个 48MHz 的 USB 时钟以及 3 个 14.318MHz 的参考时钟。这些多样化的输出可以满足系统不同组件的时钟需求,为设备的高效运行提供保障。

2. 关键规格亮点

2.1 低抖动性能

ICS951462 在时钟抖动方面表现出色。其中,CPU 输出的周期到周期抖动小于 85ps,SRC 输出和 ATIG 输出的周期到周期抖动均小于 125ps。低抖动意味着时钟信号的稳定性更高,能够减少系统中的信号干扰和错误,提高系统的可靠性和性能。例如,在处理器的高速数据传输过程中,低抖动的时钟能够确保数据的准确传输,避免数据丢失或错误。

2.2 高精度频率

这款芯片在 CPU、SRC 和 ATIG 时钟上实现了 ±300ppm 的频率精度。高精度的频率可以保证系统中各个组件的时钟同步,避免因时钟偏差导致的设备故障或性能下降。在多处理器系统中,精确的时钟同步能够确保处理器之间的协调工作,提高整个系统的处理效率。

3. 功能与特性优势

3.1 可编程时钟请求引脚

ICS951462 设有 3 个可编程的时钟请求引脚,用于控制 SRC 和 ATIG 时钟。这些引脚可以通过编程实现灵活的时钟配置,满足不同系统的个性化需求。例如,在某些特定的应用场景中,可以根据系统的负载情况动态调整时钟频率,以达到节能和提高性能的目的。

3.2 频率可编程与扩频功能

ATIGCLK 时钟的频率是可编程的,工程师可以根据实际需求进行调整。同时,芯片还具备扩频功能,能够有效降低电磁干扰(EMI)。在电子设备日益小型化和集成化的今天,电磁干扰问题越来越突出,扩频功能可以减少设备对其他电子设备的干扰,提高设备的电磁兼容性。

3.3 输出禁用与高精度电容

芯片的输出可以通过 SMBus 进行禁用,这为系统的调试和维护提供了便利。此外,外部晶体负载电容的使用可以确保最大的频率精度,进一步提高时钟信号的稳定性。

4. 引脚配置与功能

ICS951462 采用 64 - TSSOP 封装,拥有众多引脚,每个引脚都有其特定的功能。

4.1 电源引脚

包括 VDD 和 GND 引脚,为不同的时钟输出和芯片内部电路提供电源。例如,VDD48 为 48MHz 输出提供 3.3V 电源,VDDSRC 为 SRC 时钟提供 3.3V 电源等。合理的电源引脚配置可以确保芯片各个部分的正常工作,避免因电源问题导致的性能下降。

4.2 时钟输出引脚

如 48MHz_0 和 48MHz_1 输出 48MHz 时钟,SRCCLKT 和 SRCCLKC 输出差分 SRC 时钟等。这些时钟输出引脚的设计能够满足系统中不同组件对时钟信号的需求,保证系统的正常运行。

4.3 控制引脚

像 SMBCLK 和 SMBDAT 是 SMBus 的时钟和数据引脚,用于与控制器进行通信,实现对芯片的编程和控制。RESET_IN# 是实时活动低输入引脚,当该引脚被触发时,SMBus 将被重置为上电默认状态。这些控制引脚的存在使得芯片的配置和管理更加灵活方便。

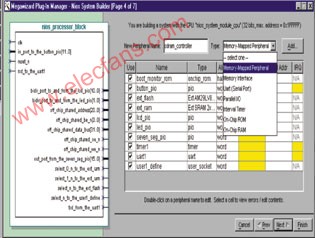

5. SMBus 通信与寄存器配置

ICS951462 通过 SMBus 接口实现对设备的全面控制。在进行读写操作时,需要遵循特定的通信协议。

5.1 写操作流程

- 控制器发送起始位。

- 发送写地址 D2 (H),芯片进行确认。

- 发送起始字节位置 N,芯片确认。

- 发送数据字节数 X,芯片确认。

- 依次发送从字节 N 到字节 N + X - 1 的数据,芯片逐个字节确认。

- 控制器发送停止位。

5.2 读操作流程

- 控制器发送起始位。

- 发送写地址 D2 (H),芯片确认。

- 发送起始字节位置 N,芯片确认。

- 控制器再次发送起始位。

- 发送读地址 D3 (H),芯片确认。

- 芯片发送数据字节数 X,然后依次发送从起始字节 N 到 N + X - 1 的数据。

- 控制器对每个字节进行确认,最后发送不确认位和停止位。

此外,芯片还有多个寄存器用于配置不同的功能,如 Spread Spectrum Enable 和 CPU Frequency Select Register 用于控制扩频和 CPU 频率选择,Output Control Register 用于控制各个时钟输出的启用和禁用等。通过合理配置这些寄存器,可以实现芯片的个性化功能。

6. 电气特性与性能指标

ICS951462 在不同的时钟输出上都有严格的电气特性要求。

6.1 K8 推挽差分对

在 K8 推挽差分对输出方面,上升沿和下降沿速率在 2 - 10V/ns 之间,差分电压在 0.4 - 2.3V 之间,周期到周期抖动小于 85ps 等。这些特性确保了 K8 处理器时钟信号的稳定性和准确性,为处理器的正常工作提供了保障。

6.2 HTTCLK 时钟

HTTCLK 时钟的长期精度在 ±300ppm 范围内,33.33MHz 输出的时钟周期在 29.9910 - 30.0090ns 之间,66.67MHz 输出的时钟周期在 14.9955 - 15.0045ns 之间等。高精度的时钟周期和长期精度能够保证 HyperTransport 总线的高速稳定运行。

6.3 SRC/ATIG 0.7V 电流模式差分对

SRC/ATIG 0.7V 电流模式差分对的电压高在 660 - 850mV 之间,电压低在 -150 - 150mV 之间,长期精度在 ±300ppm 范围内等。这些特性使得 SRC 和 ATIG 时钟能够满足系统中相关组件的需求。

6.4 USB - 48MHz 和 REF - 14.318MHz 时钟

USB - 48MHz 时钟的长期精度在 ±100ppm 范围内,REF - 14.318MHz 时钟的长期精度在 ±300ppm 范围内。高精度的时钟可以确保 USB 设备和参考时钟的稳定工作,提高系统的兼容性和可靠性。

7. 设计注意事项与建议

7.1 RESET_IN# 引脚操作

RESET_IN# 引脚的操作需要特别注意。当该引脚从高电平变为低电平时,所有输出(除了 REF[2:0] 时钟)将停止工作。REF 时钟会在两个时钟周期后断电并重新上电,SMBus 也会重新加载。整个过程中,时钟恢复到正确频率且无毛刺的时间不超过 2.5ms,而时钟停止无毛刺的时间为 3μs。需要注意的是,当该引脚从低电平变为高电平时,对时钟没有影响。在实际设计中,要合理使用该引脚进行系统的复位操作,避免因误操作导致系统故障。

7.2 SRC 路由信息

在进行 SRC 时钟的路由设计时,要遵循一定的规则。例如,L1、L2、L3 长度应分别不超过 0.5 英寸、0.2 英寸、0.2 英寸,且应采用非耦合 50 欧姆走线。L4 长度在不同的路由方式(耦合微带线和耦合带状线)下也有不同的要求,同时 Rs 和 Rt 的阻值分别为 33 欧姆和 49.9 欧姆。合理的路由设计可以减少信号干扰和衰减,提高时钟信号的质量。

7.3 共享引脚操作

ICS951462 上的输入/输出(I/O)引脚具有双重信号功能。在初始上电时,它们作为输入引脚,将逻辑电平存储到内部数据锁存器中。上电复位结束后,这些引脚变为输出引脚,为外部负载提供时钟信号。为了对这些引脚进行编程,需要连接一个 10K 电阻到 VDD 或 GND。编程电阻应靠近串联端接电阻放置,而串联端接电阻应更靠近驱动器。这样的设计可以确保在不同的工作模式下,引脚能够正常工作,同时减少信号干扰。

综上所述,ICS951462 是一款功能强大、性能出色的可编程系统时钟芯片。它通过丰富的输出特性、高精度的时钟信号、灵活的编程功能以及严格的电气特性要求,为基于 ATI RS/RD690 的系统提供了稳定可靠的时钟解决方案。在实际设计中,工程师需要充分了解芯片的各项特性和设计注意事项,根据具体的应用需求进行合理的配置和设计,以发挥芯片的最佳性能。大家在使用这款芯片的过程中,有没有遇到过一些独特的问题或者有一些创新的应用呢?欢迎一起交流讨论!

发布评论请先 登录

怎么利用FPGA设计可编程电压源系统?

可编程系统芯片的设计构架

可编程系统级芯片提供了最大设计的灵活性

在系统可编程模拟电路的原理与应用

采用FPGA的可编程电压源系统原理及设计

可编程SoC(SoPC),什么是可编程SoC(SoPC)

新型系统级可编程芯片设计方案

可编程直流电源监控系统设计

ICS951462:ATi RS/RD690 系统的可编程系统时钟芯片

ICS951462:ATi RS/RD690 系统的可编程系统时钟芯片

评论