探索LMK5C22212AS1:高性能网络同步器的卓越之选

在当今高速发展的无线通信和基础设施领域,对于高性能网络同步器和抖动清理器的需求愈发迫切。LMK5C22212AS1作为一款具有卓越性能的器件,为满足这些严格需求提供了强大的解决方案。今天,我们就来深入剖析这款器件,看看它究竟有哪些独特之处。

文件下载:lmk5c22212as1.pdf

一、器件概述

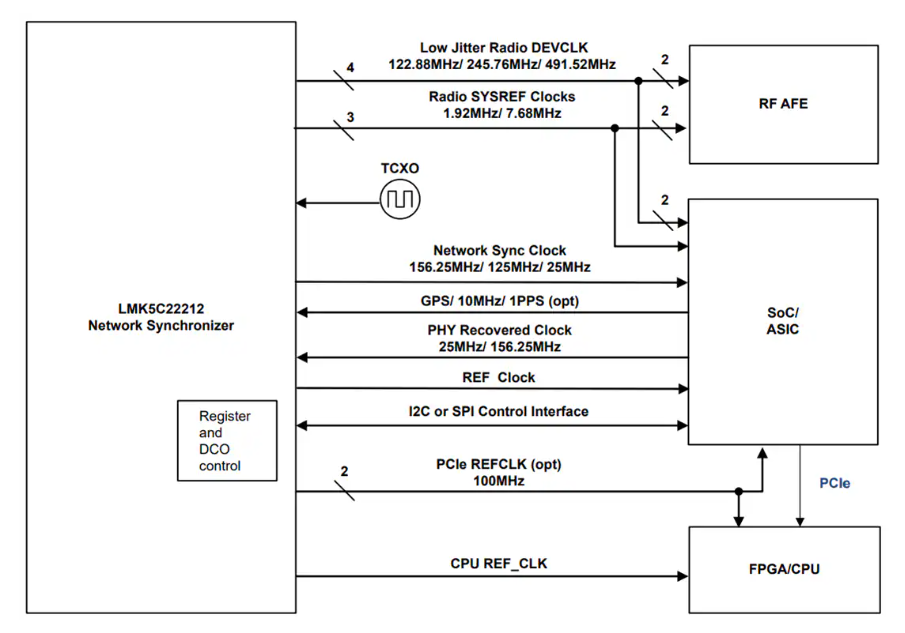

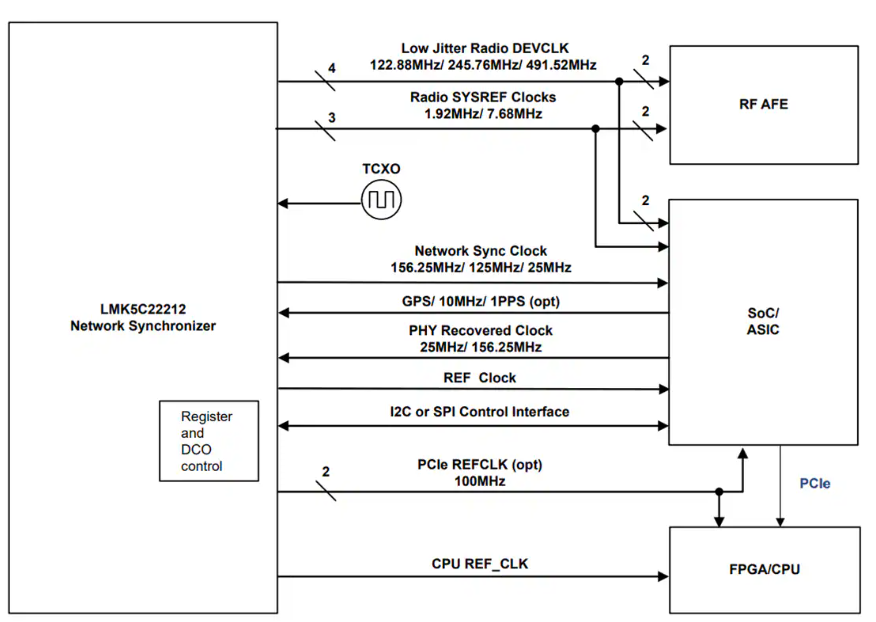

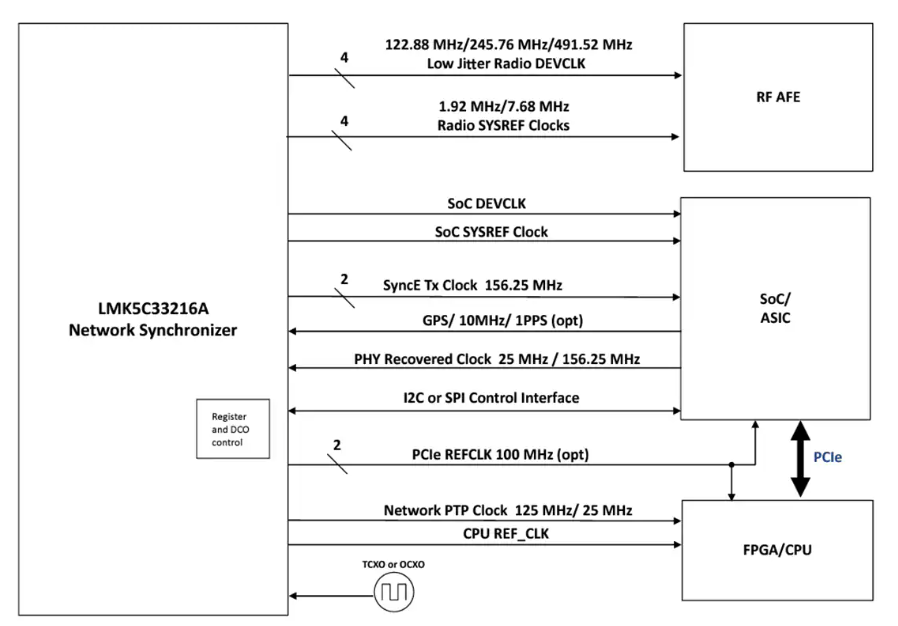

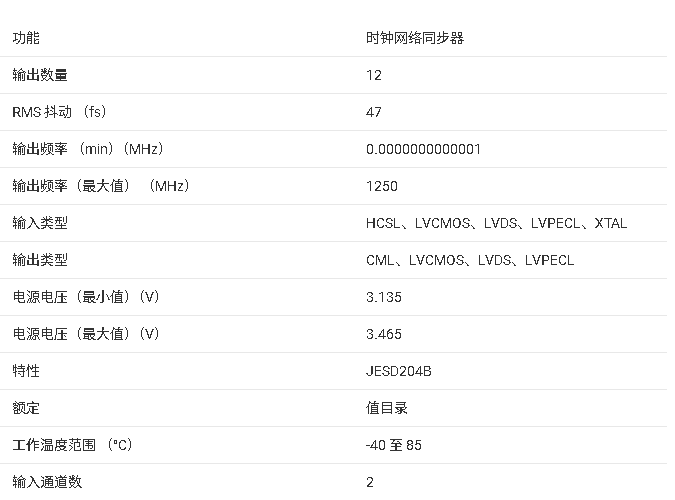

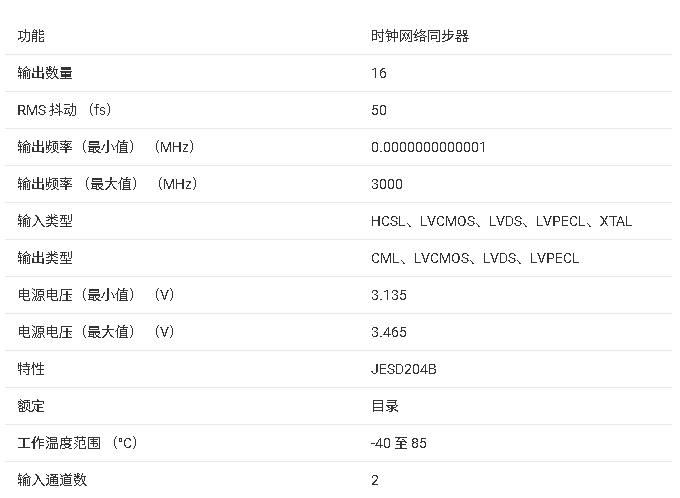

LMK5C22212AS1是一款专门为无线通信和基础设施应用设计的高性能网络同步器和抖动清理器。它集成了2个数字锁相环(DPLL)和2个模拟锁相环(APLL),拥有12个输出时钟,能够提供超低抖动的时钟信号,满足各种复杂应用的需求。

二、核心特性剖析

(一)超低抖动性能

该器件采用基于BAW VCO的技术,实现了超低抖动的时钟输出。在491.52MHz时,典型RMS抖动仅为40fs,最大为57fs;在245.76MHz时,典型RMS抖动为50fs,最大为62fs。如此低的抖动性能,能够有效保证时钟信号的稳定性和准确性,为系统的可靠运行提供坚实基础。

(二)高性能锁相环设计

2个高性能的DPLL和2个APLL的组合,为系统提供了强大的锁相能力。DPLL的可编程环路滤波器带宽范围从1mHz到4kHz,DCO频率调整步长小于1ppt,能够实现精确的频率控制。同时,2个差分或单端DPLL输入,支持1Hz(1PPS)到800MHz的输入频率,为不同的输入信号提供了灵活的选择。

(三)丰富的输出配置

LMK5C22212AS1拥有12个差分输出,支持可编程的HSDS、AC - LVPECL、LVDS和HSCL格式。在特定配置下,最多可提供16个频率输出,输出频率范围从1Hz(1PPS)到1250MHz,并且输出摆幅和共模电压均可编程。这种丰富的输出配置,能够满足不同系统对时钟信号的多样化需求。

(四)其他重要特性

该器件还支持数字保持和无缝切换功能,确保在参考信号丢失或切换时,系统能够平稳过渡,不产生明显的抖动和干扰。此外,它还兼容PCIe Gen 1到6,支持I2C或3 - wire/4 - wire SPI通信接口,方便与其他设备进行连接和控制。

三、广泛的应用场景

LMK5C22212AS1的应用场景十分广泛,涵盖了4G和5G无线网络、小基站、SyncE、SONET/SDH、IEEE - 1588 PTP等领域。在4G和5G无线网络中,它可用于有源天线系统(AAS)、mMIMO、宏远程无线电单元(RRU)等设备,为系统提供稳定可靠的时钟信号。在小基站中,能够实现精确的时钟同步,提高通信质量。同时,它还可用于抖动清理、漂移衰减和参考时钟生成,为112G/224G PAM4 SerDes等高速数据传输提供支持。

四、功能模块详解

(一)PLL架构

LMK5C22212AS1的PLL架构由DPLL和APLL组成。DPLL包含时间 - 数字转换器(TDC)、数字环路滤波器(DLF)和可编程40位分数反馈(FB)分频器,能够实现精确的相位控制。APLL则由参考(R)分频器、相位 - 频率检测器(PFD)、环路滤波器(LF)、分数反馈(N)分频器和VCO组成,用于锁定VCO频率。这种架构设计使得器件能够在不同的工作模式下,实现稳定的频率合成和相位锁定。

(二)输入输出模块

- 振荡器输入(XO):XO输入作为分数 - N APLLs的参考时钟,支持多种输入类型和配置。通过可编程的输入片上终端和AC耦合输入偏置配置,能够适应不同的时钟源。

- 参考输入:参考输入(IN0和IN1)可接受差分或单端时钟,每个输入都有独立的监测和验证功能。支持自动和手动输入选择模式,能够根据优先级和参考信号监测标准自动选择最佳输入。

- 输出模块:输出时钟分布模块包括输出复用器、输出分频器和可编程差分输出驱动器。输出复用器能够灵活选择频率源,输出分频器支持同步功能,可实现多个输出时钟的相位对齐。不同的输出通道支持多种输出格式,如差分输出的HSDS、HCSL,以及单端输出的LVCMOS等。

(三)其他功能模块

器件还具有时钟监测、调谐字历史监测、零延迟模式(ZDM)、时间间隔计数器(TEC)等功能模块。时钟监测模块能够实时监测输入时钟的频率、缺失脉冲、短脉冲等参数,确保输入信号的有效性。调谐字历史监测功能能够在进入保持模式时,根据历史平均频率确定初始输出频率,减少频率和相位干扰。ZDM模式可实现输入和输出之间的确定相位关系,TEC功能则允许用户精确测量两个事件之间的时间间隔。

五、设计与应用建议

(一)设计要点

- 电源设计:要注意电源轨的排序、电源供应的斜坡速率以及混合供应域的问题。确保所有VDD和VDDO电源在单调上升至3.135V时,满足器件的启动要求。对于非单调或缓慢的电源上升情况,可通过延迟PD#引脚的上升来延迟VCO校准。

- 时钟输入和输出接口:使用合适的源或负载终端来匹配输入和输出时钟走线的阻抗,减少信号反射和干扰。对于未使用的时钟输入和输出,可通过寄存器控制使其处于浮动和断电状态,以降低功耗。

- 布局设计:隔离输入、XO/OCXO/TCXO和输出时钟,避免与相邻的不同频率时钟和其他动态信号相互干扰。合理放置旁路电容器,确保与VDD和VDDO引脚的连接尽可能短,以减少电源噪声。

(二)应用流程

在实际应用中,可按照以下步骤进行设计:

- 配置选择:根据系统需求,选择合适的启动配置选项,如ROM启动、ROM + EEPROM启动等。

- 通信接口选择:通过GPIO1引脚选择SPI或I2C通信接口,并连接到主机设备进行编程和控制。

- XO输入配置:选择合适的XO频率和时钟源,确保其满足系统对频率稳定性和准确性的要求。

- PLL和输出配置:使用TICS Pro编程软件配置PLL和输出参数,包括输入时钟、输出频率、DPLL环路带宽等。

- 监测和中断配置:配置参考输入监测选项和DPLL锁定检测功能,设置状态输出和中断标志,以便及时监测系统状态。

六、总结

LMK5C22212AS1凭借其超低抖动性能、丰富的功能特性和灵活的配置选项,成为无线通信和基础设施领域的理想选择。在实际设计和应用过程中,电子工程师们需要充分了解器件的特性和功能,结合具体的系统需求,合理进行设计和配置,以充分发挥其性能优势,为系统的稳定运行提供有力保障。

希望通过本文的介绍,能让大家对LMK5C22212AS1有更深入的了解,在实际工作中能够更好地运用这款器件。如果你在使用过程中有任何问题或经验,欢迎在评论区分享交流。

-

无线通信

+关注

关注

58文章

5065浏览量

147016 -

网络同步器

+关注

关注

0文章

35浏览量

3027

发布评论请先 登录

探索LMK5C22212AS1:高性能网络同步器的卓越之选

探索LMK5C22212AS1:高性能网络同步器的卓越之选

评论