摘要

静电放电(ESD)是电子制造业(含PCBA装联、整机组装、半导体、封测、电子模组件等)中不可忽视的“隐形杀手”,每年给全球半导体产业造成高达数十亿美元的损失。本文旨在系统性地阐述电子制造业实现全过程ESD防护的实践经验。内容涵盖从新产品设计阶段的源头防护,到实验室验证、试产与量产线的过程控制,再到包装运输及售后失效分析的闭环管理。通过构建“设计-制造-储运-售后”的全生命周期ESD防护体系,电子制造业可显著提升产品良率与可靠性,为应对日益复杂的静电挑战提供一套可操作的解决方案。

1.引言

随着电子器件向微小化、高频化、高集成度方向发展,其对静电的敏感性急剧增加。一次短暂的静电放电事件,就足以导致器件性能退化甚至永久性损坏。ESD防护绝非仅是生产线上佩戴手腕带那么简单,它是一个贯穿产品整个生命周期、涉及整个供应链协同的系统性工程。本文将结合行业标准(如IEC 61340-5-1、GB/T 37977.51、GB/T 31841、IEC 61000-4-2、ANSI/ESD S20.20)与二十多年的实战经验,为电子制造业的ESD工程师提供一份从理论到实践的完整指南。

2.新产品ESD防护设计:源头控制是关键

“设计决定本质”,优秀的ESD防护始于产品研发阶段。在电路板(PCBA)和产品结构设计之初,就必须将ESD防护作为核心考量。

2.1器件选型与保护元件应用

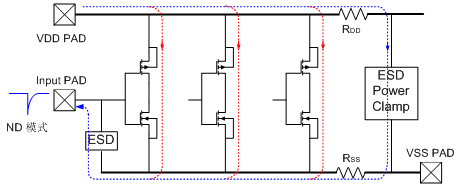

2.1.1选用高抗扰度器件:优先选择内置ESD保护结构(如TVS Clamp)的IC,或明确标示了较高HBM(人体模型)/CDM(带电器件模型)等级(如HBM≥2kV,CDM≥500V)的器件。

2.1.2外置保护元件的选型原则:在高速数据线(USB,HDMI)、电源接口、按键等ESD侵入点,必须合理布局外置ESD保护器件,如TVS二极管。

2.1.3电压匹配:TVS的击穿电压应略高于信号最高工作电压,但其钳位电压必须低于被保护器件的最大耐受电压。

2.1.4低寄生电容:对于高速信号线(如USB 3.0、HDMI),应选择超低电容(如<1pF)的TVS二极管,以避免信号完整性劣化。

2.1.5多级防护策略:对于特别敏感或高风险的端口,可采用“粗保护(如压敏电阻)+细保护(低电容TVS)”的多级防护体系,以分散和吸收静电能量。

2.2电路与PCB布局设计

2.2.1低阻抗接地路径:为ESD电流提供一条宽而短的泄放路径至大地或系统地(GND)。ESD保护器件应尽可能靠近端口放置,其接地引脚到主地平面的走线要短而粗。

2.2.2隔离与分割:对敏感模拟电路、射频电路与数字I/O端口进行合理的电源和地平面分割,必要时使用磁珠或0Ω电阻进行连接,防止ESD噪声耦合。

2.2.3结构设计协同:产品外壳设计应避免形成“缝隙天线”,金属外壳应确保与PCB地良好连接(多点连接为佳)。对于非导电外壳,可在内部关键电路区域增加接地屏蔽层。

3.新产品ESD实验室测试:IEC 61000-4-2标准验证

设计完成后,必须通过国际通用的IEC 61000-4-2标准进行ESD抗扰度测试,以验证产品的实际ESD防护能力。

3.1测试等级:标准规定了从接触放电2kV/4kV/6kV/8kV到空气放电2kV/4kV/8kV/15kV等多个测试等级。产品规格应明确其需要通过的目标等级(通常消费类为接触±4kV,空气±8kV;工业类要求更高)。

3.2测试方法:

3.2.1接触放电:测试枪头直接接触设备可触及的导电部件/部位。

3.2.2空气放电:测试枪头接近设备缝隙、开口或绝缘表面进行放电。

3.3失效判据:测试中及测试后,设备功能应满足产品标准规定的性能判据(如Class B:功能或性能暂时丧失,但能自行恢复;Class A:无性能降级)。

3.4测试要点:测试需在标准规定的接地参考平面(GRP)上进行,实验室环境(温湿度)需受控。测试应覆盖所有用户可接触点,并进行正负极性测试。最新的IEC 61000-4-2标准(2023版)对测试设备和程序有更明确的要求,ESD工程师应关注其更新内容。

4.试产线的ESD设计与防护:搭建可控的制造环境

试产阶段是验证设计、磨合工艺、建立ESD管控体系的关键时期。

4.1建立静电防护区(EPA):划定明确的EPA区域,所有ESD敏感件(ESDS)的操作必须在此区域内进行。EPA区入口应设置人员接地标志和ESD门禁闸机系统(如鞋/腕带测试仪)。

4.2接地系统建设:建立统一的“等电位连接”系统(ESD Grounding System)。包括:

4.2.1防静电地板/地垫(表面和系统电阻10^4 - 10^9Ω)。

4.2.2工作台面通过台垫接地(表面和系统电阻10^4 - 10^9Ω)。

4.2.3所有设备(烙铁、贴片机、回流焊等)外壳必须接入ESD地。

4.2.4电离器(离子风扇/离子棒)用于中和绝缘体(如塑料外壳、PCB基材)上的电荷。

4.3人员培训与规范:所有进入EPA区的人员必须接受ESD基础知识培训,并严格执行规范:佩戴并有效连接腕带、穿防静电服/鞋、避免不必要的摩擦和快速动作。

5.量产线的ESD防护:体系化与可持续运行

量产线的ESD防护需要在试产线基础上进行规模化和体系化扩展,并实现可持续的监控。

5.1体系认证与标准化:推动工厂建立并认证符合GB/T 37977.51的ESD防护体系。该体系文件化地规定了人员培训、设备接地、EPA管理、审核检查等所有ESD防护要求。

5.2实时监测与自动化:在关键工位(如SMT贴装、手工焊接、测试)部署实时连续监测系统,自动监控人员腕带、工作台接地点的有效性,一旦失效立即报警。

5.3定期检查与测量:建立周期性检查制度,使用表面电阻测试仪、静电压表、充电平板测试仪等工具,定期测量地线电阻、台垫/地板电阻、电离器平衡电压和衰减时间等关键参数。

5.4物料与耗材管理:确保所有与产品接触的容器、工具、包装均为ESD防护材质,并定期检测其有效性。

6. ESD包装与运输:产品离开工厂后的保护

产品出厂后,在仓储、运输和客户手中仍面临ESD风险,必须依靠合格的包装来防护。

6.1包装材料的选择:根据防护等级要求,选择合适类型的包装材料:

6.1.1导电材料(表面电阻 <1x10e4Ω):如金属屏蔽袋、导电泡棉,提供法拉第笼效应,屏蔽外部静电场。

6.1.2静电耗散材料(表面电阻1x10e4 ~ 1x10e11Ω):如粉红色防静电袋、防静电泡沫,用于内部缓冲,使电荷缓慢泄放。

6.1.3绝缘材料(表面电阻 ≥1x10e11Ω):应避免使用,因其易产生并积累电荷。

6.2包装规范:参考国家标准《敏感电子元器件循环包装技术要求》等规范。对于高价值器件,推荐使用“内层导电泡棉缓冲+中层防静电袋+外层屏蔽袋”的多层包装结构。

6.3包装生命周期管理:防静电包装材料会因反复使用、折叠、污染而老化失效。必须建立包装的使用次数追踪和定期检测制度。数据显示,重复使用超过5次的防静电袋,其失效率可能从0.5%飙升至2-5%。

7.售后ESD失效分析与改进:闭环质量提升

当市场返回失效品,怀疑是ESD损伤时,需启动专业的失效分析(FA)流程,并将结果反馈至前端,形成改进闭环。

7.1失效现象收集:详细记录失效发生时的环境、操作动作、失效模式(如完全死机、功能异常、参数漂移)。

7.2电性失效分析:使用曲线追踪仪(Curve Tracer)对疑似受损引脚进行I-V特性测试,寻找开路、短路或漏电增大的证据。

7.3物理失效分析:

7.3.1无损分析:X射线(X-Ray)检查内部连线;声学扫描显微镜(SAT)检查分层。

7.3.2有损分析:开封(Decap)后,使用发射显微镜(EMMI)或红外热成像(IR)定位热点,最后通过聚焦离子束(FIB)切片和扫描电子显微镜(SEM)观察具体的物理损伤点(如金属熔融、硅熔坑)。

7.4失效模型判定与改进:根据损伤特征判断失效模式属于HBM(热损伤为主)还是CDM(电场击穿为主)。将分析结论反馈至:

7.4.1设计部门:加强特定端口的ESD防护设计或调整布局。

7.4.2生产部门:检查相关工位的接地、电离设备或操作规范。

7.4.3客服/市场部门:更新产品使用手册,增加ESD警告提示。

8.结论

电子制造业(含PCBA装联、整机组装、半导体、封测、电子模组件等)的ESD防护是一项永无止境的系统工程,它融合了电子/电工技术、材料、管理和文化。其核心在于转变观念:从“被动补救”转向“主动预防”,从“局部管控”转向“全流程协同”。通过在新产品设计阶段植入防护基因,在制造过程中构建可靠的ESD控制体系,在流通环节实施严格的包装管理,并在售后阶段进行深度的失效分析以驱动持续改进,企业才能构建起真正坚固的ESD防护长城。这不仅是提升产品质量和可靠性的必要投资,更是企业在激烈市场竞争中赢得信任、保障利润的基石。

**参考文献**

1.GBT 37977.51静电学 第5-1部分 电子器件的静电防护通用要求

2.GB.T31841-2015电工电子设备机械结构电磁屏蔽和静电放电防护设计指南

3.IEC 61340-5-1-2024保护电子器件/组件免受静电放电损坏的一般要求

4.多层级ESD防护体系构建:MDDTVS二极管如何与其他元件协同作战,2025-05-09

5.IEC 61000-4-2:2023,电磁兼容(EMC)– 第4-2部分:试验和测量技术–静电放电抗扰度试验.

6.工业生产线ESD控管与ESD防制标准实现(ANSI/ESD S20.20),工研院产业学习网

7.器件级静电放电人体模型(HBM)和带电器件模型(CDM)的测试规范与实施流程.

8.敏感电子元器件循环包装技术要求,T/SDWL 0004-2024,2024-07-10

-

ESD

+关注

关注

50文章

2424浏览量

180418 -

电子制造

+关注

关注

1文章

308浏览量

25023

发布评论请先 登录

浅析ESD 防护与ESD 防护器件

基于EMC的ESD防护设计分析

芯片IC可靠性测试、ESD测试、FA失效分析

在工作中如何做好ESD防护 资深工程师经验分享

为大家分享一下如何做好网站服务器安全防护

如何做好通信总线的隔离防护

【华秋干货铺】静电威胁无处不在,电子元件的静电防护很重要

MDDESD静电放电对电子元器件的影响:从损坏机制到防护策略

如何做好电子制造工厂的ESD防护—从设计到售后失效分析的全流程策略

如何做好电子制造工厂的ESD防护—从设计到售后失效分析的全流程策略

评论