前 言

本文为TD-FD工程开发的指引文档,提供工程编译、程序加载等开发流程说明。

开发环境

Windows开发环境:Windows10 64bit

开发工具:TD_5.9.1_DR1_2025.1_NL、FD_2025.1_SP1

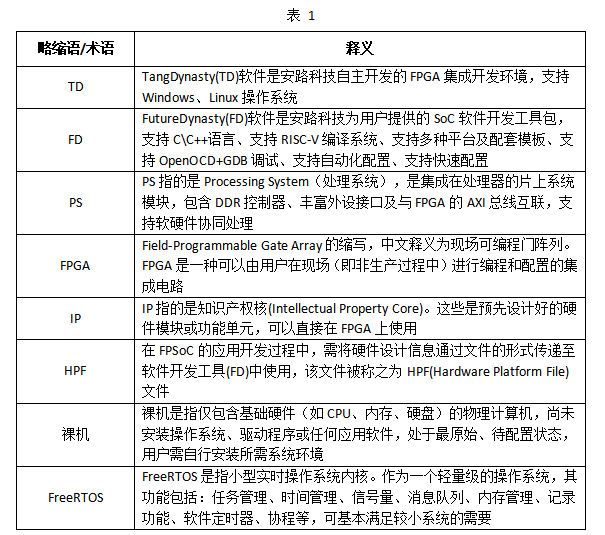

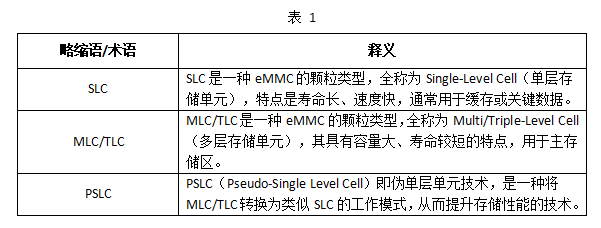

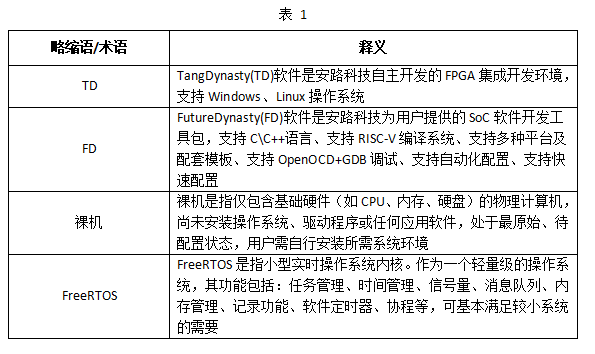

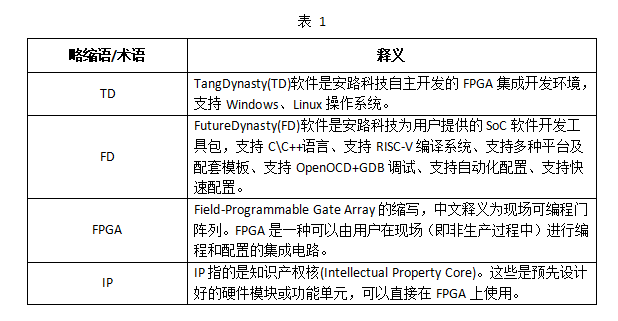

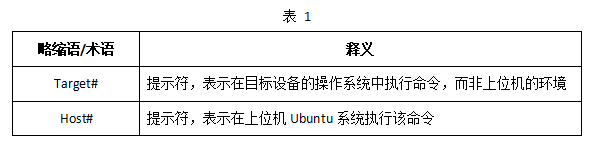

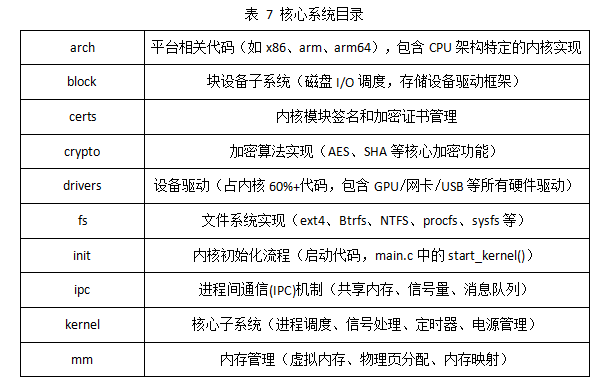

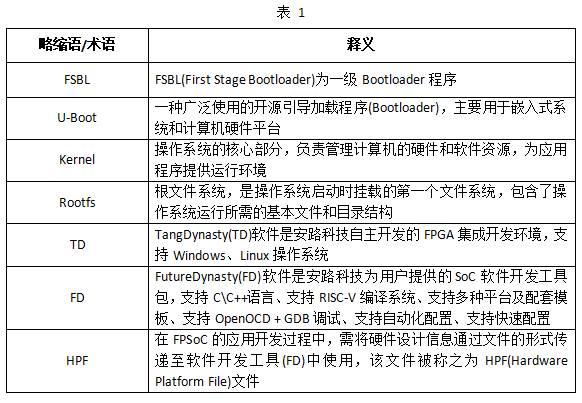

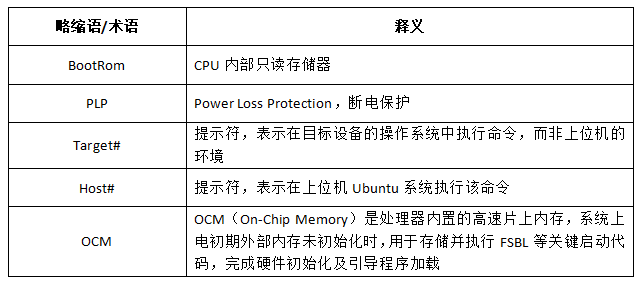

术语表

为便于阅读,下表对文档出现的关键术语进行解释;对于广泛认同释义的术语,在此不做注释。

注意事项

(1)请先按照《开发环境搭建》文档安装TD、FD等软件以及进行JTAG驱动安装,使用下载器(厂家:安路科技,型号:AL-LINK-FT-V1.0)连接评估板JTAG接口至PC端USB接口。

(2)请先将评估板启动方式选择拨码开关设置为000(1~3),此档位为JTAG模式,再将评估板上电。

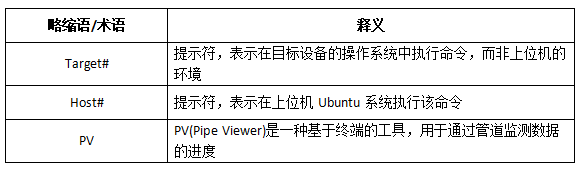

1TD工程的程序加载、创建与编译

1.1 程序加载

1.1.1通过下载器加载

本章节以产品资料“4-软件资料DemoFPGA-demosFPGA-HDL-demos”目录下的led_flash案例为例,演示通过下载器加载程序的操作方法。此案例的功能是控制评估底板PL端的LED3进行闪烁。

在此之前,请将对应案例目录拷贝至Windows非中文路径下并解压案例目录下的project.zip压缩包。

备注:Windows路径有长度限制,路径太长将会导致工程打开出错。

在TD软件菜单栏中依次点击"Tools -> Debug Server Setting"。

图 1

图 1

在弹出的对话框中,勾选"AL-LTHK-FT(Locsl Host)","Local Port"设置为5555,"JTAG CLK Freg"选择3MHz,"Cable Select 0"选择FT94VM980,点击"Apply and Close"。

图 2

图 2

将评估板上电启动。在菜单栏中依次点击"Tools -> Download"。

图 3

图 3

在弹出的对话框中,软件会自动识别"0:DR1M90",若未自动识别可点击"Refresh"。然后点击"Add"添加镜像。

图 4

图 4

选择led_flash_dr1m90.bit镜像,然后点击“打开(O)”。

图 5

图 5

添加镜像完成后,点击"Run"。

图 6

图 6

程序加载完成后,评估底板LED3将会进行闪烁。

图 7

图 7

1.1.2通过PS端加载

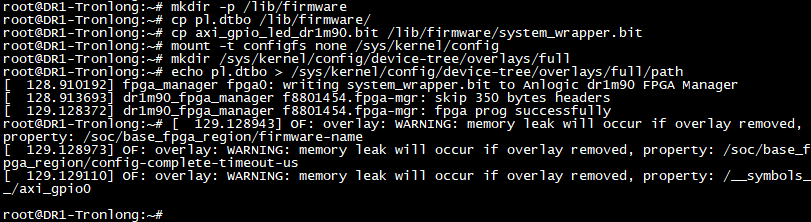

本小节以产品资料“4-软件资料DemoFPGA-demosAll-Programmable-SoC-demos”目录下的axi_gpio_led案例为例,演示通过PS(Linux系统)加载PL工程的方法。

将dtbo动态设备树镜像文件和PL工程编译生成的.bit镜像文件拷贝至评估板文件系统的"/lib/firmware/"目录下(若该目录不存在,请新建)。其中.bit镜像文件位于“4-软件资料DemoFPGA-demosAll-Programmable-SoC-demosaxi_gpio_ledhwbin”目录下。将PL端可执行文件重命名为system_wrapper.bit,然后执行如下命令加载PL端镜像。

Target# mkdir -p /lib/firmware

Target# cp pl.dtbo /lib/firmware/

Target# cp axi_gpio_led_dr1m90.bit /lib/firmware/system_wrapper.bit

Target# mount -t configfs none /sys/kernel/config

Target# mkdir /sys/kernel/config/device-tree/overlays/full //创建full目录,可根据实际情况修改

Target# echo pl.dtbo > /sys/kernel/config/device-tree/overlays/full/path //dtbo文件名称请根据实际情况修改

图 8

图 8

如需重新加载dtbo动态设备树镜像文件,请执行如下命令先删除full目录,再重新创建full目录加载dtbo。

Target# rmdir /sys/kernel/config/device-tree/overlays/full

Target# mkdir /sys/kernel/config/device-tree/overlays/full

Target# echo pl.dtbo > /sys/kernel/config/device-tree/overlays/full/path

图 9

图 9

查看"/sys/class/gpio/"目录下生成的gpiochip322节点,地址为0x80100000,与axi_gpio_led案例给AXI GPIO IP分配的地址一致。

Target# ls /sys/class/gpio/gpiochip* -l

图 10

图 10

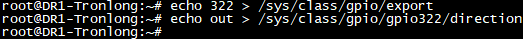

生成gpio322节点,配置gpio322为output。

Target# echo 322 > /sys/class/gpio/export

Target# echo out > /sys/class/gpio/gpio322/direction

图 11

图 11

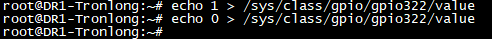

通过gpio322控制底板LED3亮灭。

Target# echo 1 > /sys/class/gpio/gpio322/value

Target# echo 0 > /sys/class/gpio/gpio322/value

图 12

图 12

1.2 PL端动态设备树编译

本小节以产品资料“4-软件资料DemoFPGA-demosAll-Programmable-SoC-demos”目录下的axi_gpio_led案例为例,演示PL端功能相关的动态设备树的编译方法。

axi_gpio_led案例的动态设备树文件pl.dtsi位于“4-软件资料DemoFPGA-demosAll-Programmable-SoC-demosaxi_gpio_ledswlinux_systemsrc”目录下,其内容如下。

/dts-v1/;

/plugin/;

/ {

fragment@0 {

target-path = "/soc/base_fpga_region";

#address-cells = <0x2>;

#size-cells = <0x2>;

__overlay__ {

#address-cells = <0x2>;

#size-cells = <0x2>;

firmware-name = "system_wrapper.bit";

config-complete-timeout-us = <3000000000>;

};

};

fragment@1 {

target-path = "/soc";

__overlay__ {

#address-cells = <0x2>;

#size-cells = <0x2>;

axi_gpio0: gpio@80100000{

/* AXI_GPIO: AXI_GPIO_0 */

status = "okay";

reg = <0x0 0x80100000 0x0 0x1000>;

compatible = "anlogic,axi-gpio-1.00.a";

#gpio-cells = <2>;

#interrupt-cells = <0x2>;

gpio-controller;

anlogic,interrupt-present = <0x1>;

anlogic,all-inputs = <0x0>;

anlogic,all-outputs = <0x0>;

anlogic,dout-default = <0x00000000>;

anlogic,gpio-width = <0x1>;

anlogic,gpio2-width = <0x20>;

anlogic,tri-default = <0xFFFFFFFF>;

anlogic,is-dual = <0x0>;

};

};

};

};

请将其拷贝至Ubuntu工作目录,并在此目录执行如下命令,使用dtc工具编译动态设备树源文件。编译完成后,将在当前目录下生成dtbo动态设备树镜像文件。

Host# dtc -v

Host# dtc -q -@ -O dtb -o pl.dtbo pl.dtsi

图 13

图 13

1.3TD工程创建与编译

本章节主要演示TD工程创建与编译方法。如无需重新编译或创建工程,请忽略本章节内容。

1.3.1创建TD工程

打开TD软件,在菜单栏中依次点击"Project -> New Project..."。

图 14

图 14

在弹出的对话框中,根据实际情况设置Project Name(工程名)和Project Path(工程存放路径),"Device Family"选择"DR1","Device Name"选择"DR1M90GEG484","Device Speed"选择"-2",点击"OK"创建工程。

图 15

图 15

图 16

图 16

在菜单栏中依次点击"Source -> New Source..."。

图 17

图 17

在弹出的对话框中,根据实际情况设置File Name(文件名)和Location(源码存放路径),"File Type"选择"Verilog",勾选"Add To Project",点击"OK"。

图 18

图 18

图 19

图 19

打开"led_flash.v"文件,在代码编辑区编写代码并保存。

图 20

图 20

鼠标右键点击"FLAG Flow"中的"Syn Opt -> Read Design",点击"Run"。

图 21

图 21

在弹窗中点击"OK"。

图 22

图 22

然后双击"FLAG Flow"中的"IO Constraint",打开管脚分配界面。

图 23

图 23

从底板原理图可知,LED3引脚为R15,电压1.8V,故设置"Location"为"R15","IOStandard"为"LVCMOS18",并点击保存。

图 24 用户指示灯原理图

图 24 用户指示灯原理图

图 25

图 25

在弹窗选择约束文件类型,此处以选择"Single Line"为例,然后点击"OK"。

图 26

图 26

请自定义约束文件的路径和名称,然后点击“保存”。

图 27

图 27

在弹出的界面中点击"Yes",将约束文件添加到工程。

图 28

图 28

至此,已完成约束文件配置,双击打开"led_flash.adc"文件,可看到约束文件内容。

图 29

图 29

1.3.2导入TD工程

打开TD软件,在菜单栏中依次点击"Project -> Open Project..."。

图 30

图 30

选择需要导入的工程所在目录下的工程文件,点击“打开”。

图 31

图 31

在弹出的界面中点击"OK"。

图 32

图 32

即可完成导入。

图 33

图 33

1.3.3编译TD工程

鼠标右键点击"FLAG Flow"中的"Phy Opt -> Generate Bitstream",点击"Run All"。

图 34

图 34

编译完成后,在工程"xxx_Runsbest_result"目录下将会生成.bit镜像文件。

图 35

图 35

图 36

图 36

由于篇幅过长等原因,部分内容均不逐一展示,如需获取完整版详细资料,请关注创龙科技微信公众号或官网,或者评论区留言,感谢您的支持!

审核编辑 黄宇

-

Linux

+关注

关注

88文章

11810浏览量

219513 -

评估板

+关注

关注

1文章

1034浏览量

31320

发布评论请先 登录

DR1 系列评估板 eMMC 健康管理案例开发手册:信息查询与寿命监控

DR1 系列评估板 PS 端裸机与 FreeRTOS 开发案例手册

DR1 评估板 PL 端 FPGA 开发完全指南:基础案例与 ADC 采集模块详解(一)

DR1M90 开源 IgH EtherCAT 主站案例:伺服电机正反转实时控制方案

基于 DR1M90 的 Linux-RT 内核开发:从编译配置到 GPIO / 按键应用实现(1)

基于安路DR1M90 FPSoC的Linux系统全流程开发指南(4)

基于安路DR1M90 FPSoC 的Linux 系统全流程开发指南(3)

基于安路DR1M90 FPSoC 的Linux 系统全流程开发指南(1)

一步步完成安路飞龙 DR1M90 Linux 系统固化:启动卡制作 + eMMC 固化

安路DR1M90评估板:从基础外设到通信模块测试指南

DR1M90 评估板 TD-FD 工程与 Linux 多场景应用开发指南

DR1M90 评估板 TD-FD 工程与 Linux 多场景应用开发指南

评论