DP83561-SP:高辐射环境下的千兆以太网PHY解决方案

在高辐射的航天环境中,电子设备的可靠性和稳定性面临着巨大的挑战。德州仪器(TI)的DP83561-SP千兆位以太网PHY专为应对这一挑战而设计,为高辐射航天环境提供了可靠的通信解决方案。本文将深入探讨DP83561-SP的特性、应用、详细功能以及设计要点。

文件下载:dp83561-sp.pdf

一、DP83561-SP特性概览

DP83561-SP具有一系列令人瞩目的特性,使其在恶劣环境中脱颖而出。

1.1 辐射性能卓越

它属于QML V类(QMLV)、RHA(抗辐射加固)产品,军用温度范围为 -55°C至125°C。辐射性能方面,高达 TID = 300krad (Si),对LET的抗扰度达到121MeV - cm²/mg,有效抵御辐射对设备的影响。

1.2 SEFI监测与校正

集成了单粒子功能中断(SEFI)监测套件,可对IEEE PCS状态机、ECC配置寄存器、PLL锁定以及片上温度进行监测。一旦监测到事件,会通过中断引脚发出信号。同时,配置寄存器受ECC保护,还支持引脚可配置自动SEFI恢复,有效应对SEFI事件。

1.3 以太网协议兼容

完全兼容IEEE 802.3的10BASE - T、100BASE - TX以及1000BASE - Te规范,低RGMII延迟($TX < 90ns$,$RX < 290ns$)符合时间敏感网络标准,为不同速率的以太网通信提供支持。

1.4 接口与电源灵活

支持RGMII、MII等MAC接口,集成MDI终端电阻器,可编程RGMII终端阻抗。电源方面,支持2.5V、1.8V、1.1V供电,I/O电压可选1.8V、2.5V和3.3V,还提供25MHz或125MHz同步时钟输出。

二、应用领域广泛

DP83561-SP适用于多种航天应用场景,包括命令数据和处理(CD&H)通信负载、雷达成像有效载荷、光学成像有效载荷、激光通信有效载荷以及科学勘探有效载荷等,为这些关键应用提供稳定可靠的通信支持。

三、详细功能解析

3.1 以太网模式支持

- 1000BASE - T:支持该标准,在1000M模式下使用四个MDI通道通信,可工作在自动协商模式,通过寄存器或引脚设置进行配置。

- 100BASE - TX:支持该标准,100M模式下使用两个MDI通道,可自动协商或强制模式工作,使用强制模式时需从寄存器0x1E启用Robust Auto - MDIX功能。

- 10BASE - Te:同样支持该标准,100M模式下使用两个MDI通道,可自动协商或强制模式工作,通过寄存器或引脚设置配置。

3.2 MAC接口特性

- RGMII:设计用于减少MAC和PHY互连所需的引脚数量,数据路径和控制信号经过复用,使用时钟的上升和下降沿。为满足不同MAC的时序要求,设计PCB时需考虑TX信号的控制阻抗、路由长度和信号完整性,同时可通过寄存器配置时钟偏移和延迟模式。

- MII:适用于100M和10M速度,使用时需确保PHY以相应速度连接,通过自动协商解决MDI速度时,建议通过寄存器0x9关闭千兆速度广告。

3.3 自动协商功能

所有1000BASE - T PHY都需支持自动协商,DP83561-SP的自动协商功能具有三个主要目的:协商速度和双工选择、解决主从配置以及解决暂停或非对称暂停问题。通过交换快速链路脉冲(FLP)实现配置信息的交换,确保选择最高性能的协议。

3.4 辐射性能保障

- 总电离剂量(TID):作为RHA QML Class V产品,TDR水平达到300 krad(Si),按MIL - STD - 883进行晶圆级测试和鉴定。

- 单事件效应(SEE):根据EIA/JEDEC标准进行单事件效应表征,未观察到单事件闩锁(SEL)。

- 单事件功能中断(SEFI)监测套件:提供一套监测器,检测设备关键区域的SEFI事件并纠正故障,包括PCS状态机监测、配置寄存器监测、温度监测和PLL锁定监测。

3.5 其他功能特性

- WoL(Wake - on - LAN)数据包检测:可检测特定帧并通过寄存器状态变化、GPIO指示或中断标志通知连接的MAC,支持多种WoL帧类型。

- IEEE 1588帧起始检测:支持在接收和发送路径的SFD(帧起始定界符)处提供指示脉冲,可通过寄存器调整脉冲时序,提高数据包时间戳的准确性。

- 电缆诊断:采用时域反射计(TDR)技术,可检测电缆的开路、短路、阻抗不匹配等问题,测量精度可达±1m。

- 时钟输出:可通过CLK_OUT引脚输出内部时钟,时钟源可通过寄存器配置。

四、设计要点与建议

4.1 电源供应

DP83561-SP支持两电源和三电源配置,每种配置都有相应的电源排序要求。在布局时,需在VDD引脚附近放置1 - μF和0.1 - μF的去耦电容,确保电源稳定。

4.2 布局设计

- 信号迹线:PCB迹线应尽量短,避免长迹线对信号质量的影响。信号迹线的阻抗应保持恒定,差分对的迹线长度应匹配,减少延迟差异和共模噪声。

- 返回路径:信号迹线下方应有连续的接地或直流电源平面作为返回路径,避免平面分割对信号质量和EMI的影响。

- 变压器布局:变压器下方不应有金属层,防止变压器注入噪声影响系统性能。

- 金属浇注:非信号和电源的金属浇注应接地,避免浮置金属产生问题。

- PCB层堆叠:为满足信号完整性和性能要求,建议使用6层PCB,也可根据系统需求选择其他配置。

4.3 时钟输入

输入参考时钟要求在所有功能模式下相同。若使用晶体源,建议使用25 - MHz、负载电容为15 - pF至40 - pF的并联晶体谐振器;若使用外部时钟振荡器,应直接连接到XI,XO浮空。

4.4 磁学要求

在铜以太网接口应用中,需要磁隔离。磁学元件需满足一定的电气规格,如匝数比、插入损耗、回波损耗等。

五、总结

DP83561-SP作为一款专为高辐射航天环境设计的千兆以太网PHY,凭借其卓越的辐射性能、丰富的功能特性以及灵活的接口和电源配置,为航天通信应用提供了可靠的解决方案。在设计过程中,遵循相应的布局和电源供应建议,能够充分发挥DP83561-SP的性能优势,确保系统的稳定性和可靠性。各位工程师在实际应用中,可根据具体需求深入研究和配置,以实现最佳的设计效果。你在使用DP83561-SP过程中遇到过哪些问题呢?欢迎在评论区分享交流。

发布评论请先 登录

Microchip推出全新VSC8574RT PHY器件 进一步扩大耐辐射千兆以太网PHY产品阵容

简谈基于FPGA的千兆以太网

工业温度级双端口千兆位以太网性能评估包括BOM及层图

AR8031-AL1A--千兆以太网收发器方案资料

国产以太网百兆千兆PHY芯片RPC8211F替换瑞昱

Microchip推出全新VSC8574RT PHY器件进一步扩大耐辐射千兆以太网PHY产品阵容

【世说芯品】Microchip推出全新VSC8574RT PHY器件进一步扩大耐辐射千兆以太网PHY产品阵容

【世说芯品】Microchip推出全新VSC8574RT PHY器件进一步扩大耐辐射千兆以太网PHY产品阵容

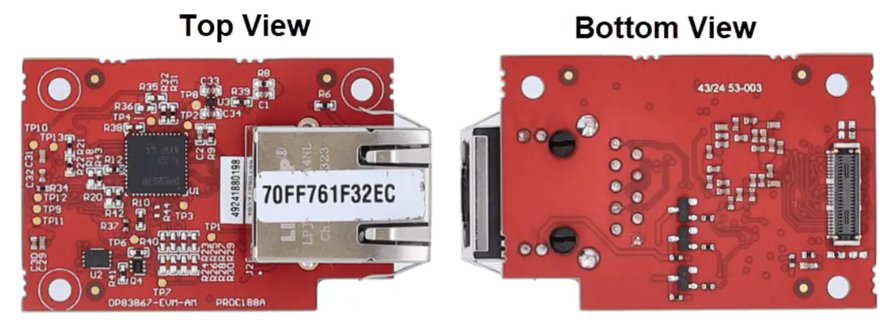

Texas Instruments DP83867-EVM-AM以太网PHY附加板数据手册

DP83561-SP:高辐射环境下的千兆以太网PHY解决方案

DP83561-SP:高辐射环境下的千兆以太网PHY解决方案

评论