技术发展到今天的信息时代,数据的存储和传输在嵌入式系统有了越来越重要的地位。而USB是目前设计成熟、应用广泛且使用极为简捷的技术,USB传输是一种高效方便的数据传输方式。基于上述原因,本文重点论述基于USB的海量存储(USB Mass Storage)设备功能在ARM嵌入式系统中设计和应用。使用该设备功能,上位机可以像读写普通U盘一样对于系统采集并存储在FLASH中的数据进行读写。

1、 硬件方案

1.1 器件简介

S3C44B0X是SAMSUNG公司出品的基于ARM7TDMI内核的RISC型微处理器,8 kB指令和数据共享的缓存,主频可达66 MHz,可以运行16位的Thumb指令和32位的ARM指令,且接口丰富,具有通用性。

K9F2808U0C是SAMSUNG公司生产的一款Nand型闪存芯片,容量为16 MB,读写速度快,数据保存时间长,可擦写10万次,在嵌入式系统中有着广泛的应用,主要是负责数据存储。

PDIUSBDl2是PHILIPS公司生产的带有并行总线和局部DMA传输能力的全速USB接口芯片,符合USB1.1版规范,可以与任何外部MCU/MPU实现并行接口,传输速度可达2 MB/s。该USB芯片有1个控制端点和2个普通端点。

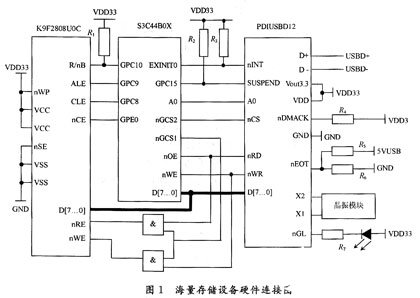

1.2 硬件连接图

硬件连接如图1所示。在该系统中,FLASH芯片K9F2808U0C负责嵌入式系统中的数据存储;处理器S3C44B0X执行底层固件代码;USB接口芯片PDIUS-BDl2负责设备与上位机的通讯。这样系统采集并存储在闪存芯片中的数据便可以通过USB接口传输到上位机。

2、 软件实现

要实现实验系统与上位机的USB通讯,首先要正确设计PDIUSBD12的底层固件程序。而要实现系统的海量存储设备功能,还要有FLASH的读写操作代码和实现海量存储设备类规范的代码。下面从这3个方面来分析。软件开发环境为ARM公司的ADS1.2,USB监控和测试软件为BUS Hound。

2.1 PDIUSBD12固件编程

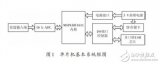

PDIUSBDl2固件结构和数据流向如图2所示。结构图中的硬件提取层是固件中的最底层代码,负责对处理器与PDIUSBDl2相连接的I/O口进行操作,以通知PDI-USBD12接下来处理器将对其进行命令操作或是数据操作。而命令接口层是基于硬件提取层的一套对PDIUS-BDl2进行操作的子程序,可以方便上层程序的编写。

当PDIUSBD12向处理器发出中断请求时,处理器读取中断寄存器,根据中断源调用相应的中断服务处理程序,中断服务处理程序设置相应的事件标志,如果有数据传输并作相应的数据处理。根据USB协议[4],控制端点0用来负责设备的枚举,如获取设备各种描述符、设置地址、获取海量存储设备的逻辑单元数目和复位设备等操作。这些操作是通过中断和主循环共同完成的。这里端点1未用到,可以忽略其中断。端点2是主端点,用作Bulk-Only传输。在端点2的中断处理程序中实现Bulk-Only传输及命令解析和执行。

其中,中断服务处理程序与主循环通过一个名为ControlData的结构体变量进行通讯。主循环初始化I/O口、事件标志bUSBFlags、建立包数据缓冲区、定时器和中断,重新连接USB总线后进入一个无限循环,当该循环轮询到某事件标志被置位时便进行相应的处理。特别是在设备枚举中当建立标志被置位时,根据设备请求的类型域ControlData,DeviceRequest,bmRequestType来确定是标准设备请求、厂商设备请求还是类型设备请求,再根据请求类型进行相应的调用。

2.2 K9F2808U0C读写操作

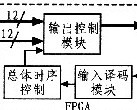

K9F2808U0C共有1 024块,每块32页,每页528 B,其中512 B用于存放数据,另外16 B用于存放信息,如块的好坏标记、块逻辑地址和ECC校验和等。FLASH读写有其自身的特点,读写都以页为单位,可以随机读,但无法随机写,写操作前必须把写单元所在的块擦除。因此,对于该闪存的读操作可以采取直接读取来处理;而对于写操作,则通过设置块 缓冲来解决,以减轻系统的任务和对FLASH的擦除次数。写操作的基本思想是:设置一个块缓冲区,待写数据先写入缓冲区对应的页地址,当缓冲区中待写数据的页地址到达31或者页地址未满31但传输已经结束时,先将目标块中待写页以外的有关数据保存到缓冲区对应的页地址,然后擦除整块,最后将缓冲区的数据拷贝到该块。写操作流程如图3所示。

2.3 海量存储规范实现

海量存储设备必须符合海量存储设备类规范,该规范包括4个独立的子类规范,本设计中用到其中的2个子类规范:一是USB Mass Storage Class Bulk-Only Transport规范[5];二是USB Mass Storage Class UFI Command规范。前者定义了数据/命令/状态在USB总线上的传输方法,Bulk-Only传输规范仅仅使用Bulk端点传送数据/命令/状态。后者定义了对存储介质的操作命令,UFI命令规范基于SCSI-2和SFF-8070i命令集。这里根据SCSI-2规范[6]针对该类设备的操作命令规范,总共编写了9个命令执行函数,见下文。

海量存储规范的实现有2个地方要注意:一是设备描述符、配置描述符、接口描述符和端点描述符要正确设置,主机是通过控制端点(端点0)获取这一些描述符的;二是BULK端点(端点2)的中断处理,其中的BULK OUT中断处理较BULK IN复杂,由于篇幅所限,下面只讨论BULK OUT的中断处理。

BULK OUT的中断处理要对主机发送的CBW(Com-mand Block Wrapper)和数据进行解析和处理。伪代码结构如下:

其中pSCSI是传递给读写函数的有关读写地址和数据传输长度等参数的结构体。数据的处理在读写函数中进行。Write( )函数的流程如图3。读函数以页为单位,一次可以读取连续的若干页,在此不再列出其流程图。其他函数可根据SCSI-2命令规范来编写。

3、结 语

经测试,通过USB总线主机能够稳定的读写设备中的FLASH,读数据的速度可达600 kB/s,写数据的速度可达400 kB/s。该设备功能使用方便,性能稳定,已在具体项目中有实际应用,根据硬件情况稍做修改便可以应用到其他嵌入式系统中。

责任编辑:gt

-

FlaSh

+关注

关注

10文章

1715浏览量

154710 -

usb

+关注

关注

60文章

8372浏览量

281732 -

数据采集

+关注

关注

40文章

7815浏览量

119856

发布评论请先 登录

基于单片机的高精度海量数据采集与存储系统

基于U盘的单片机海量存储方案

求:基于FPGA的数据采集存储系统的sch原理图

常见的几种不同的高速数据采集存储系统介绍

基于SAR系统的高速数据采集和存储系统

基于DSP的视频采集存储系统设计

基于SATA硬盘和FPGA的高速数据采集存储系统

基于USB海量存储设备实现FLASH数据采集和存储系统的设计

基于USB海量存储设备实现FLASH数据采集和存储系统的设计

评论