引言:本文在H.264码率控制机制的基础上,提出了一种基于平均绝对差(MAD)比率的跳帧算法。该算法将图像的MAD比率和缓冲器占用量作为跳帧判别标准,为运动剧烈的图像保留缓冲器空间。实验结果表明,本算法一方面可以有效地降低缓冲器的占用量和节省编码时间,从而在硬件方面表现为降低对缓冲器大小等方面的要求,达到降低成本的目的;另一方面,可以保证图像序列连续性和提高图像质量。

大多数视频压缩技术和标准产生的比特率都是可变的,为了能够在恒定比特率的通信信道和网络中传输,需要在码率控制中引入一个缓冲区机制,先将压缩后的码流存入缓冲区,然后以恒定码率输出。因此,码率控制的任务就是在保证缓冲器不产生上溢和下溢的前提下,通过调整一些编码参数(如量化参数)来使编码比特率达到期望值。

跳帧策略是码率控制算法中防止缓冲器上溢的手段。以往的跳帧算法往往确定某一个固定的限值(通常为80%)[1],当缓冲器的占用量到达这个限值时,不考虑下一帧的任何情况就把它跳过。这种跳帧算法的缺陷有两点:当缓冲器占用量达到80%时盲目地跳过下一帧,有可能错过运动剧烈的图像而导致译码后图像序列质量的下降;当缓冲器占用量未达到80%,但却很接近80%时,如果下一帧图像运动比较剧烈的话,较多的编码比特数就会导致缓冲器发生严重的上溢。

本文提出了基于MAD比率的跳帧判断准则,将当前缓冲器的占用量与每一帧图像的运动剧烈程度结合起来,对缓冲器的占用量设定几个阈值,并且用MAD比率来对每幅图像的运动剧烈程度进行标识。对于某个MAD比率的图像来说,当缓冲器占用量达到跳帧判别准则中规定的阈值时,即将该帧跳过。这样就可以通过跳过一些运动平缓的图像,而为运动剧烈的图像保留缓冲器空间,从而保证图像序列的连续性,提高图像质量。

码率控制算法

帧层的码率控制算法

帧层的码率控制分为两个阶段:第一阶段为每一个P帧计算一个目标比特数,第二阶段持续地更新率失真模型的各个参数并且进行跳帧控制。

假设只有一组图像(GOP),并且图像序列的编码顺序是第一帧为I帧,后面为连续的P帧。假设N表示组图中所有帧的数目,nj表示组图中的第j帧,Bc(nj)表示编码第j帧图像后缓冲器实际的占用量,A(nj)表示编码第j帧时实际产生的比特数,Bs表示缓冲器大小,Tbl(nj)表示第j帧被编码后缓冲器的目标值,Rr表示剩余比特数,Nr表示组图中剩余的帧数。因此,第j+1帧图像被编码后缓冲器的实际占用量Bc(nj+1)可以表示为[2][3]:

假设第一个P帧的量化参数等于组图的量化参数,所以有:

其它P帧被编码后缓冲器的目标值由下式给出:

因此,考虑缓冲器占用量而得到的目标比特数Tbuff可以表示为:

其中gama是个常量,它的值通常为0.75。

考虑剩余比特数而得到的目标比特数Tr可以表示为:

所以,最后的目标比特数T可以通过Tbuff和Tr的加权和得到:

试验中β=0.5[2]。

宏块层的码率控制

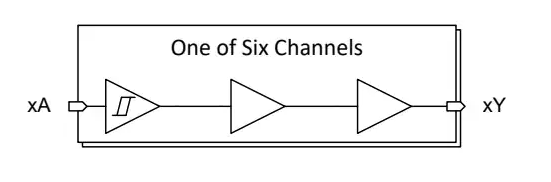

在宏块层,根据每一个宏块的MAD来给每一个宏块分配比特数并且求出量化参数。宏块层的码率控制分为三个步骤:首先为每一个宏块分配比特数;其次根据目标比特数计算出量化参数;最后在对每一个宏块编码后,进行参数的预测。

a.比特数的分配

假设Nm表示一帧中宏块的个数,Ave_MAD表示一帧图像中各个宏块的MAD的平均值,MAD[i][j]表示第i帧中第j个宏块的MAD。因此第i帧中第j个宏块所分配的目标比特数b[i][j]可表示为:

b.计算各个宏块的量化参数

率失真函数是许多码率控制算法的核心,它将量化参数Q与编码比特数R联系起来,其关系式为:

其中S表示宏块的编码复杂度,X1和X2是率失真模型参数。Q值较小时,分配较多的编码比特数;Q值较大时,则分配较少的编码比特数。

c.模型参数的预测

在对每一个帧进行编码后,都要根据前面n帧的编码结果对模型参数(X1、X2)进行更新。由上式可以得出:

最小均方误差可以表示为:

该等式成立的条件是:(a)n>1,(b)所有的n个Q值不完全相同。

基于MAD比率的跳帧算法

在恒定比特率应用中,编码器和传输信道间的缓冲器起了十分重要的作用。编码器应该使缓冲器的占用量保持在50%左右。如果缓冲器发生上溢,则会损失一些数据。相反,如果缓冲器的占用量过低就会浪费带宽。当缓冲器的值很高时,避免上溢的方法就是跳过一个完整的帧。

由以往的经验可以知道,大多数的跳帧过程都是由于缓冲器上溢引起的。与缓冲器的目标值即缓冲器大小的一半相比较,实际中缓冲器发生上溢的可能性远远大于发生下溢的可能性。缓冲器的占用量低于缓冲器大小25%的情况是非常少见的。因此,有必要把缓冲器的占用量控制在50%左右,以保证缓冲器的占用量有足够的上升空间。

下面详细介绍一下基于MAD比率的跳帧算法:

假设图像序列的编码顺序为第一帧为I帧,后面是连续的P帧,ω1、ω2、ω3表示缓冲器占用百分比;ξ1、ξ2、ξ3表示图像的运动剧烈程度,它等于当前帧图像的MAD预测值与整个组图中所有已编码P帧图像的平均MAD的比值(见下面的公式)。

基于MAD比率的跳帧算法的思想是尽量跳过运动平缓的帧而保存运动剧烈的帧。对于运动平缓的图像而言,缓冲器的占用量不用达到80%,而只要达到一个预先设定的限值时就将它跳过。运动越剧烈,对应的限值就越高。运动的剧烈程度ξ(i)用下式表示:

其中,MADPi表示第i帧图像的MAD预测值,MADAi表示第i帧图像的MAD实际值。

当ξ(i)小于ξ1时,只要缓冲器的占用量达到ω1,就将该帧跳过;当ξ(i)小于ξ2时,只要缓冲器的占用量达到ω2,就将该帧跳过;当ξ(i)小于ξ3时,只要缓冲器的占用量达到ω3,就将该帧跳过;当缓冲器的占用量达到80%时,无论下一帧图像运动剧烈与否,都将它跳过。

由于I帧和前面几个P帧对于运动补偿的估计比较重要,跳过这些帧容易影响到后面的帧,因此,本文的跳帧算法从第三个P帧,即第四帧开始;而对前三帧的处理方法是:对I帧不采取跳帧,对第一和第二个P帧只有当缓冲器的占用量达到80%时才跳过。

对于需要跳过的帧将不进行编码,而是用上一帧图像来代替。

图1为基于MAD比率的跳帧算法流程图。其中Q表示量化参数;N表示帧编号。

试验结果

本节根据第三部分基于MAD比率跳帧算法的思路,将该新型跳帧算法的实验结果与传统跳帧算法的试验结果相比较。

实验采用JM9.6的实验平台,实验环境是MicosoftVisualC++6.0。官方网站

http://iphome.hhi.de/suehring.tml中下载到JM的各个版本的程序。实验中所使用的计算机的CPU为Pentium41.5G;内存大小为256M。

采用的图像序列为Mobile和Tempete,二者均为CIF格式。图像序列的编码顺序为IPP...IPP...,每隔30个P帧有一个I帧。

下面从缓冲器占用量、编码时间、运动估计时间和SNR四个方面给出本文的跳帧算法与以往算法的对比实验结果。

缓冲器占用量的比较

图2和图3表示对Tempete序列和Mobile序列每一帧进行编码后缓冲器中的比特数。图中,横坐标表示编码帧数目,纵坐标表示缓冲器占用量;实线表示的是使用原始的跳帧算法时缓冲器占用量的曲线图,*线表示的是采用基于MAD比率的跳帧算法后缓冲器占用量的曲线图。从图2和图3可以看出,在第0、30、60和90帧处,缓冲器占用量急剧

上升,这是由于在这四处均为I帧,编码比特数比较大,缓冲器的输入远远大于输出。对于每个I帧后的P帧,由于编码比特数比较小,缓冲器的输入小于输出,所以缓冲器的占用量逐渐减少。图2和图3均表明:基于MAD比率的跳帧算法可以降低缓冲器的占用量、避免了缓冲器发生上溢。

编码时间、运动估计时间和SNR的比较

表1和表2给出对Tempete序列和Mobile序列编码,传统跳帧算法与基于MAD比率的跳帧算法在编码时间、运动估计时间和SNR三个方面性能的比较。

从表1和表2可以看出,基于MAD比率的跳帧算法可以较大幅度地缩短编码时间和运动估计时间。在Tempete序列中,编码时间的改进量高达12.73%。在Mobile序列中,运动估计时间的改进量达到了8.58%。

此外,基于MAD比率的跳帧算法使得Y、U和V三个分量的SNR值均有所提高。由于在解码过程中是用前面一个已经编码的帧来代替跳过的帧,所以对于一个运动比较剧烈的帧而言,若按照传统跳帧算法将其跳过的话,将会影响到解码端图像恢复的连续性,从而造成图像质量的下降。而本文提出的跳帧算法其实质就是通过放弃运动平缓的帧,为运动剧烈的帧保留缓存空间。从而提高了整个图像序列的SNR值。

参考文献:

[1]MinqiangJiang,NamLing.OnEnhancingH.264/AVCVideoRateControlbyPSNR-BasedFramecomplexityEstimation.IEEETransactionsonConsumerElectronics,V.51,No.1,February

2005:P281-286.

[2]NamryeSon,YoonjeongShin,GueesangLee.ANovelRateControlSchemeforH.264VideoCodingusingAdaptiveQuantizationParameter.ProceddingsofSPIE.2004,V.5600:P70-77.

[3]景华,何芸.一种低复杂度码率控制究.计算机工程与应用.2003,V(02):P116-122.

[4]ThomasMeierandKingN.Ngan.ImprovedsingleVOratecontrolforconstantbit-rateapplicationsusingMPEG-4.ProcessingofSPIE.2000,V.4067:P64-75.

[5]MingiangJiang,XiaoquanYi,NamLing.Improve-

dFrame-LayerRateControlforH.264usingMADratio.Proceedingsofthe2004InternationalSymposium.

May2004,V.3:P813-816.

:

-

缓冲器

+关注

关注

6文章

2215浏览量

48673 -

Mobile

+关注

关注

0文章

518浏览量

27059 -

SNR

+关注

关注

3文章

197浏览量

25443

发布评论请先 登录

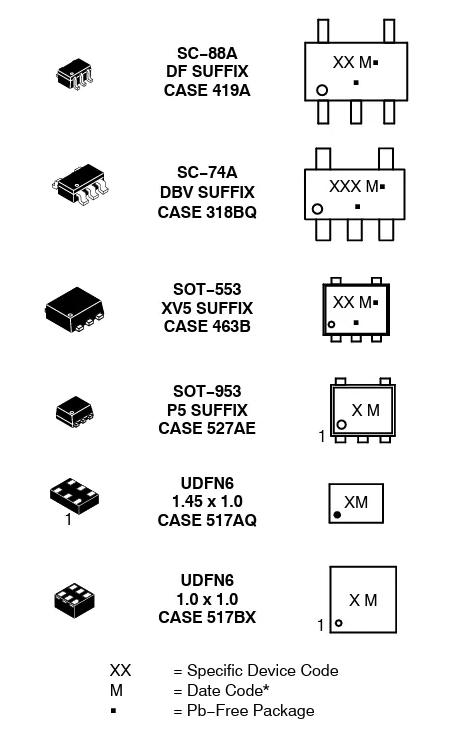

NL17SZ07非反相开漏缓冲器技术解析与应用指南

国产时钟缓冲器:技术革新与市场竞争

时钟缓冲器的应用场景及如何选择合适的时钟缓冲器?

浙江赛思电子时钟缓冲器的应用条件

Texas Instruments SN74ACT17六路缓冲器数据手册

时钟缓冲器在现代化建设中的作用

74ALVCH16827 20位缓冲器/线路驱动器规格书

缓冲器占用量的详细比较

缓冲器占用量的详细比较

评论