倾佳电子基于B3M040065R碳化硅MOSFET的电机集成伺服驱动器(IMD)系统设计白皮书

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

I. 引言:集成化SiC伺服驱动的机遇与挑战

A. 行业趋势:从电柜到集成

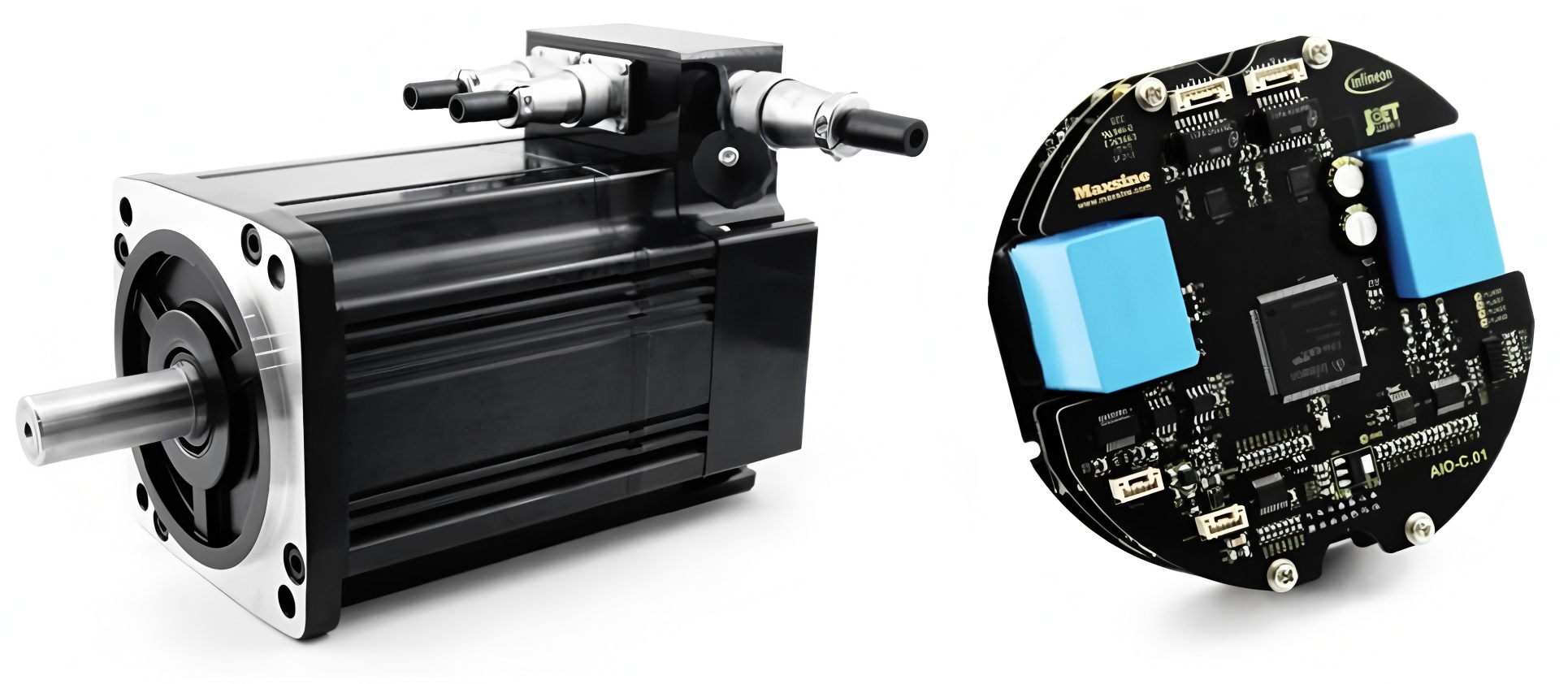

伺服驱动(Servo Drives)技术正经历一场深刻的架构演进,即从传统的、安装在控制电柜中的驱动器,转向“电机集成化驱动器”(Integrated Motor Drive, IMD)。这一趋势的核心驱动力在于其显著的系统级优势:

系统简化与成本降低:IMD架构消除了驱动器与电机之间昂贵的、笨重的动力和编码器电缆。这不仅大幅降低了材料和安装成本,还简化了机器的整体设计与调试 。

空间效率:通过将驱动器集成到电机外壳(例如后端盖)中,释放了宝贵的控制电柜空间,使得机器的整体占地面积更小,布局更灵活 。

性能与EMC改善:消除了长电缆这一高效的“辐射天线”,从根本上降低了系统的电磁干扰(EMI)问题 。同时,驱动器与电机参数的紧密耦合,消除了电缆寄生参数对控制环路的影响,使得更高性能的电机控制成为可能 。

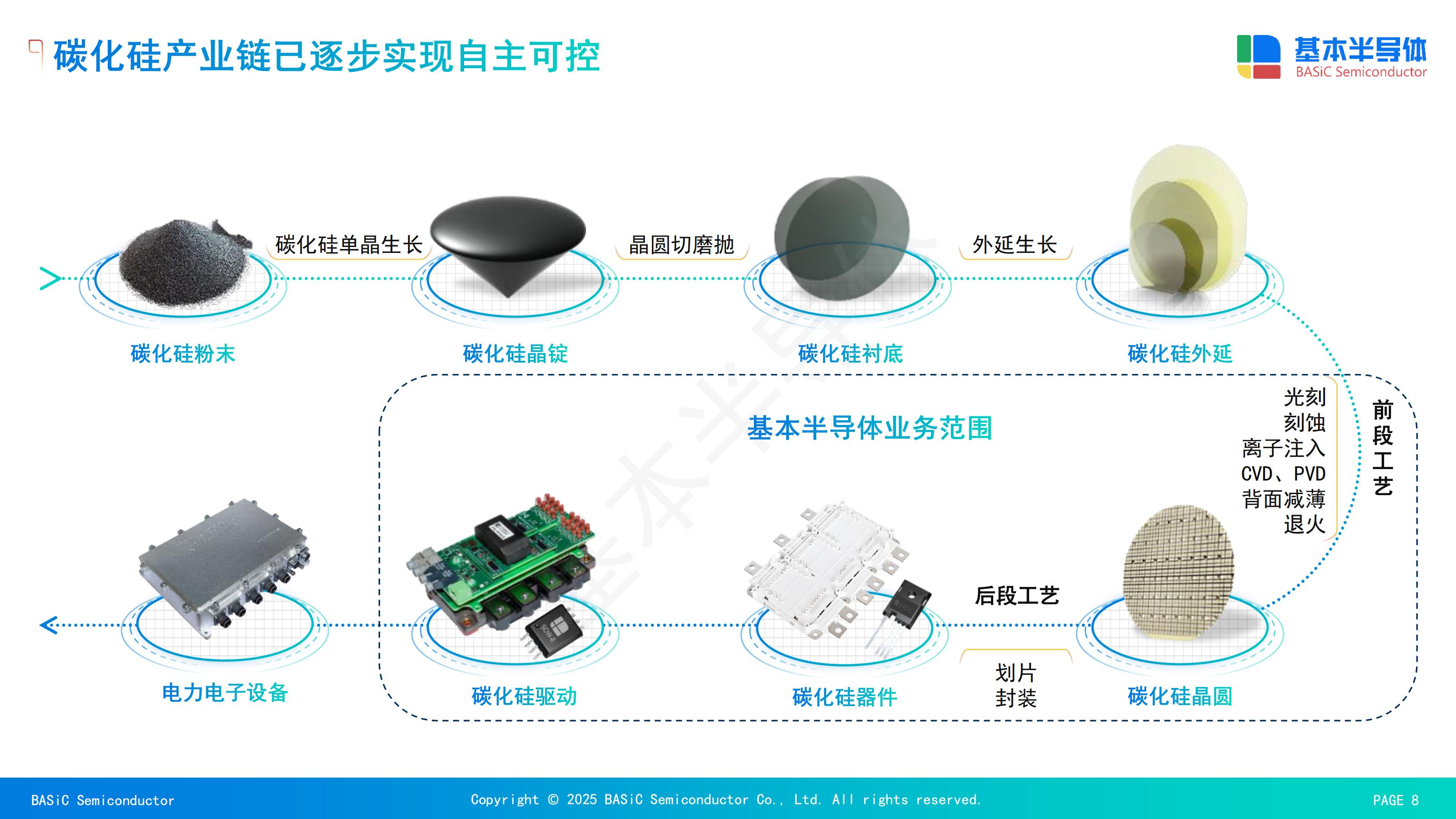

B. 碳化硅(SiC)的角色:实现集成的关键技术

在传统硅(Si)技术下,高功率的IMD难以实现。硅基IGBT的开关损耗和热密度限制了其在高温、紧凑空间内的应用。而以B3M040065R为代表的宽禁带半导体(WBG)碳化硅(SiC)MOSFET,是实现高功率密度IMD的关键技术:

极高效率:B3M040065R具有极低的导通电阻($R_{DS(on)}$)和开关能量($E_{on}/E_{off}$)。这意味着在输出相同功率时,其自身产生的热量(损耗)远低于IGBT,使得在有限的电机壳体空间内进行散热成为可能 。

高功率密度:SiC的低开关损耗允许驱动器运行在更高的开关频率($f_{sw}$),例如远超20 kHz的超声波频段。这使得直流支撑电容(DC-Link)和EMI滤波器等无源器件的体积和重量得以大幅减小,这是在IMD严苛空间限制下实现封装的先决条件 。

卓越的耐温性:B3M040065R的最高工作结温($T_j$)可达175°C ,远高于硅器件。这使其在必须承受电机自身发热(来自绕组和轴承)的严苛高温环境中,具有更高的运行裕量和可靠性 。

C. 核心挑战概述

尽管B3M040065R提供了实现IMD的物理基础,但这种集成也带来了前所未有的、相互交织的工程挑战。本报告将系统性地分析并提供基于B3M040065R特性的设计对策,以解决三大核心挑战:

热力-机械集成(Thermo-Mechanical):驱动器电子器件(PCB)必须在高振动环境中(电机运行产生)可靠运行 。同时,驱动器自身产生的数十瓦热量,必须与电机产生的热量一起,通过电机壳体这一共享的、有限的散热路径进行管理 。

电磁兼容性(EMI/EMC):SiC极高的开关速度($dv/dt$)会产生强烈的电磁噪声 。在紧凑的金属外壳内,必须防止功率级的噪声耦合到同一外壳内高度敏感的微控制器(MCU)和传感电路上 。

高频PCB布局(Layout):B3M040065R的SiC性能(低损耗、快速度)不是自动获得的,它极度依赖于PCB布局。错误的布局将导致巨大的寄生电感,从而产生致命的电压过冲、开关损耗剧增和控制振荡,使其性能退化甚至损坏 。

本白皮书旨在为伺服系统研发工程师提供一份详尽的技术蓝图,指导如何利用B3M040065R SiC MOSFET应对上述挑战,成功设计一款高性能、高可靠性的电机集成伺服驱动器。

II. 核心器件分析:B3M040065R的设计约束 (Design Constraints)

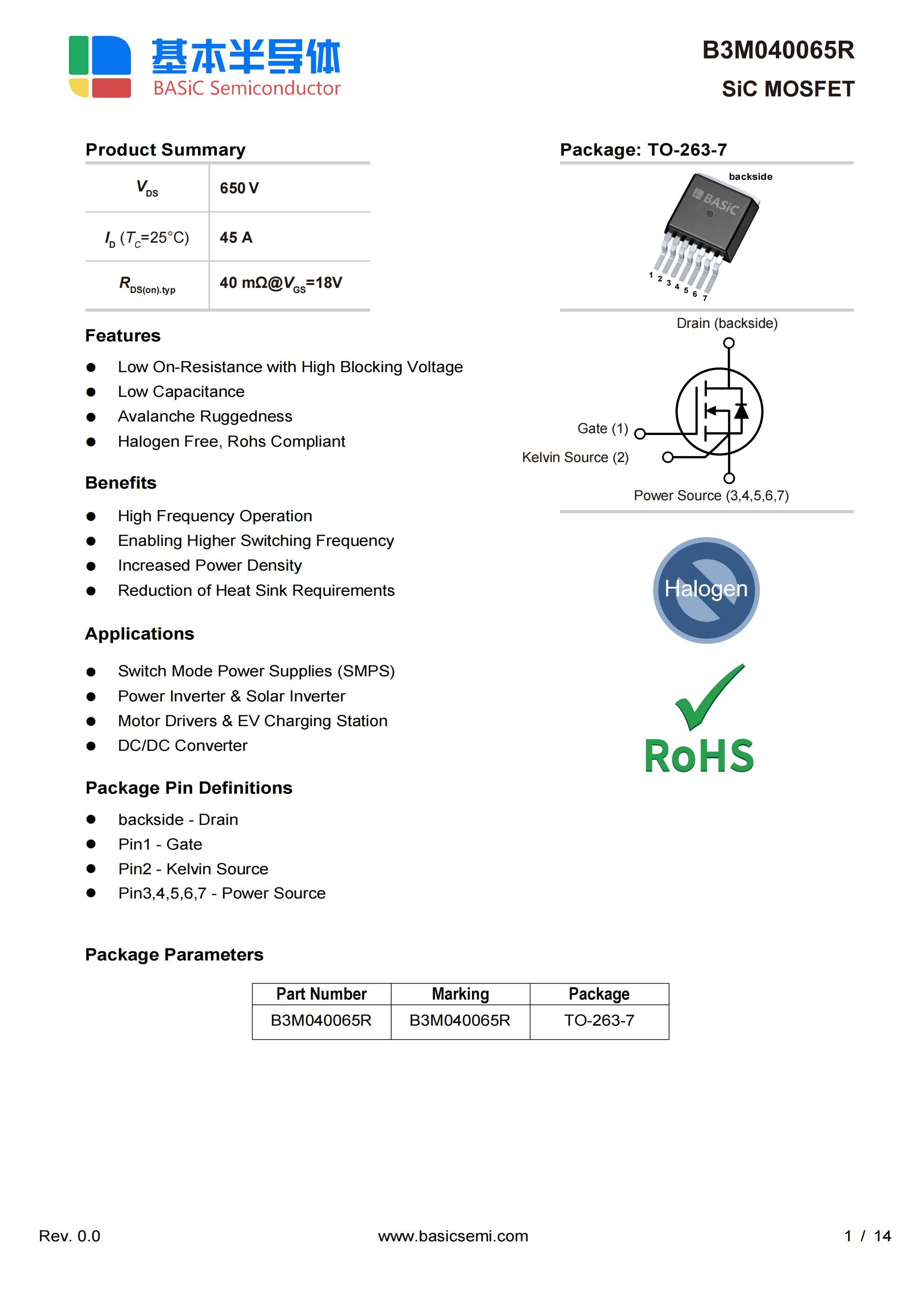

所有系统设计决策必须源于对核心功率器件B3M040065R数据手册 5 的深度解读。本节将提炼其关键参数,并推导出它们对IMD设计的刚性约束。

A. 关键设计参数表

表格 2.1:B3M040065R 关键设计参数表

| 参数 | 测试条件 | 数值 | 来源 | 设计意义与约束 |

|---|---|---|---|---|

| $V_{DSmax}$ | $V_{GS}=0V$ | 650 V | 5, p.2 | 直流母线电压($V_{DC}$)的绝对上限。 |

| $V_{GSop}$ | 推荐栅压 | -5 V / +18 V | 5 | 刚性约束。必须采用双极性驱动(-5V/+18V)以实现最佳性能和可靠性。 |

| $R_{DS(on).typ}$ | $V_{GS}=18V, I_D=20A, T_j=25^{circ}C$ | 40 m$Omega$ | 5 | 误导性参数。在IMD高温环境中无参考价值。 |

| $R_{DS(on).typ}$ | $V_{GS}=18V, I_D=20A, T_j=175^{circ}C$ | 55 m$Omega$ | 5 | 关键设计参数。所有导通损耗和热设计的必须以此值为基准。 |

| $R_{th(jc)}$ | 结到壳热阻 | 0.65 K/W | 5 | 器件内部热阻极低。散热瓶颈将出现在器件外部($R_{th(cs)}$)。 |

| $Q_G$ | 总栅极电荷 | $V_{GS}=-5/+18V, I_D=20A, V_{DS}=400V$ | 60 nC | 5 |

| $E_{on}$ (体二极管) | $I_D=20A, T_j=175^{circ}C, R_G=10Omega$ | 93 $mu$J | 5 | 极高。包含体二极管的高反向恢复电荷($Q_{rr}$)。 |

| $E_{off}$ (体二极管) | $I_D=20A, T_j=175^{circ}C, R_G=10Omega$ | 33 $mu$J | 5 | - |

| $E_{on}$ (外接SBD) | $I_D=20A, T_j=175^{circ}C, R_G=10Omega$ | 56 $mu$J | 5, p.4 | 关键设计决策。显著低于使用体二极管的值。 |

| $E_{off}$ (外接SBD) | $I_D=20A, T_j=175^{circ}C, R_G=10Omega$ | 36 $mu$J | 5, p.4 | - |

| 封装 | - | TO-263-7 | 5, p.1 | 表面贴装,背面为Drain。热量必须通过PCB传导。 |

| 特殊引脚 | Pin 2 | 开尔文源极 (Kelvin Source) | 5, p.1 | 布局关键。必须用于栅极驱动返回路径以实现SiC的高速性能 。 |

B. 核心参数推导的深度洞察与设计决策

1. 高温$R_{DS(on)}$的主导地位与热失控风险

B3M040065R的数据清晰地显示了其 $R_{DS(on)}$ 具有显著的正温度系数:在$T_j=175^{circ}C$时的值(55 m$Omega$)比较$T_j=25^{circ}C$时的值(40 m$Omega$)高出37.5% 。

在IMD设计中,驱动器的工作环境温度($T_{ambient}$)极高,它由电机壳体温度决定,轻松超过85°C 2。因此,B3M040065R的结温($T_j$)将长期在高温区稳态运行。

这引入了一个潜在的**热力学正反馈(热失控)**循环:

电机运行发热,导致IMD的环境温度升高 。

B3M040065R的 $T_j$ 升高。

$R_{DS(on)}$ 随 $T_j$ 升高而增加(从40 m$Omega$ 逼近 55 m$Omega$) 。

导通损耗 $P_{cond} = I_D^2 times R_{DS(on)}$ 随 $R_{DS(on)}$ 增加而增加。

驱动器自身发热增加,进一步推高 $T_j$。

设计决策 2.1:所有功率损耗和热力学计算(见第五、六章)必须基于 $T_j=175^{circ}C$ 时的 $R_{DS(on)}$ (55 m$Omega$) 作为基准,并在此基础上留出足够的安全裕量。任何基于25°C(40 m$Omega$)数据的设计在IMD应用中都注定会因热量估算不足而失败。

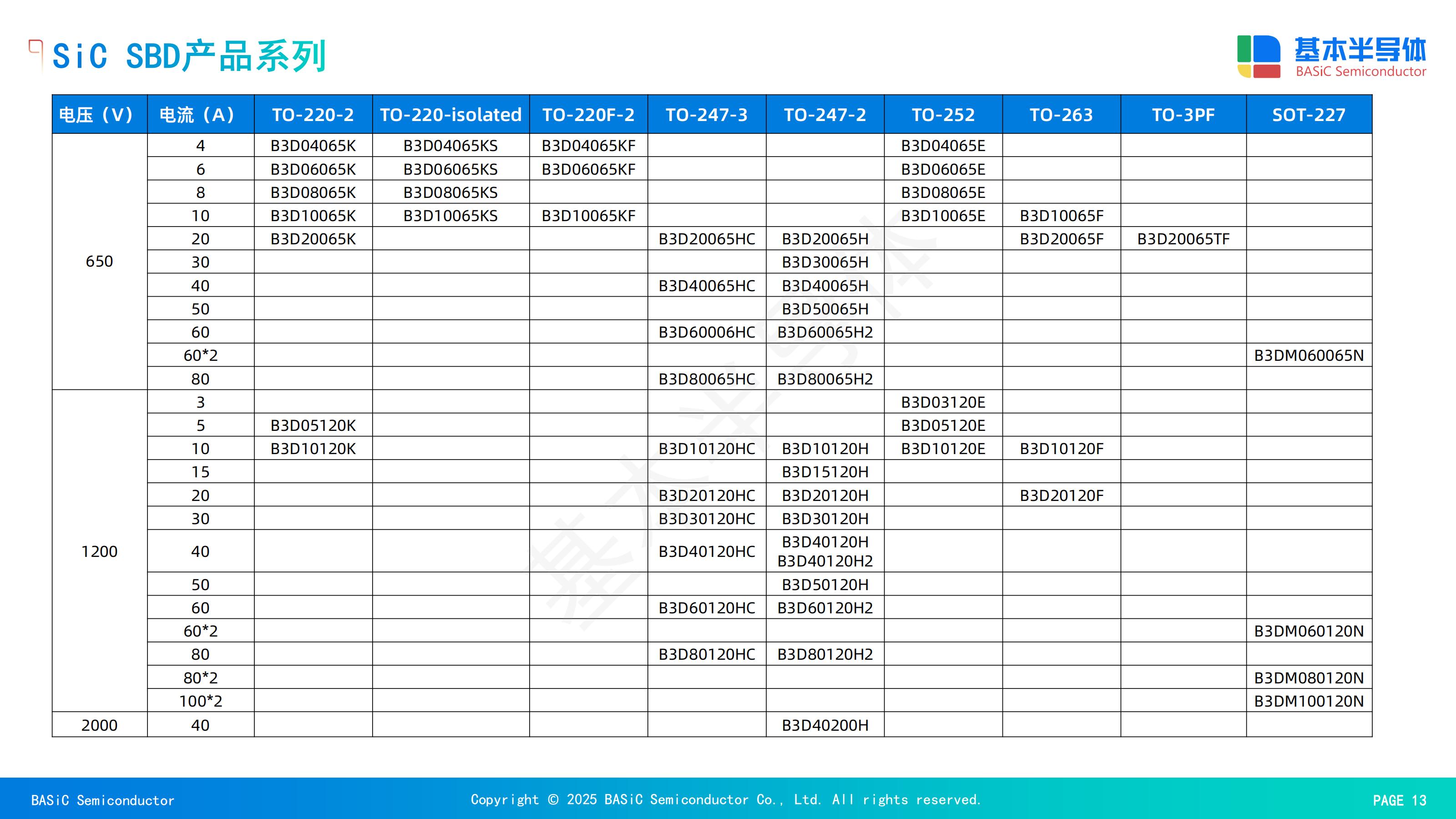

2. “残酷的权衡”:体二极管 (Body Diode) 与外部续流 (SBD)

B3M040065R数据手册在第4页 5 和 5 中提供了一个至关重要的对比:在175°C、20A、400V条件下,开通损耗($E_{on}$)的对比:

使用体二极管续流(FWD=Body Diode):$E_{on} = 93~ mu J$

使用外部SiC SBD续流(FWD=SIC SBD):$E_{on} = 56~ mu J$

$E_{on}$ 包含了续流二极管的反向恢复能量($E_{rr}$)5。B3M040065R的体二极管在175°C时具有高达 235 nC 的反向恢复电荷($Q_{rr}$)5,这导致了巨大的 $E_{rr}$ 损耗。而外部SiC SBD的 $Q_{rr}$ 几乎为零。

这意味着,如果为了节省空间而使用体二极管,开通损耗将暴增66%($93mu J / 56mu J - 1$)。由于总开关损耗 $P_{sw} = (E_{on} + E_{off}) times f_{sw}$,这将在高开关频率($f_{sw}$)下产生巨大的额外热负荷。

IMD的核心约束是空间 ,在三相逆变器中增加六颗外部SBD(每颗B3M040065R配一颗)会显著增加PCB面积和复杂性。然而,对于热受限的IMD应用,热负荷是首要敌人。

设计决策 2.2:必须做出权衡。为了实现高性能伺服(要求高$f_{sw}$)并确保热设计的可行性,必须选择为每个B3M040065R配备一个外部SiC SBD。本设计必须在极其有限的空间内容纳12个功率器件(6x MOSFET, 6x SBD),以换取热负荷的大幅降低。

3. 栅极驱动的刚性需求:-5V / +18V 双极性驱动

B3M040065R的推荐栅极操作电压($V_{GSop}$)为 -5V / +18V 。这不是一个建议,而是刚性需求:

+18V 开通:必须使用+18V(或更高,但不超过22V )以确保MOSFET完全导通,实现数据手册中标称的最低 $R_{DS(on)}$(例如175°C下的55 m$Omega$)。使用+15V将导致 $R_{DS(on)}$ 显著升高 ,从而增加导通损耗。

-5V 关断:必须使用-5V负偏压进行关断。B3M040065R具有极快的开关瞬变($dv/dt$5。在半桥拓扑中,当一个MOSFET(例如下管)开通时,另一个(上管)的漏源极(Drain-Source)会经历高 $dv/dt$。这个 $dv/dt$ 会通过米勒电容($C_{rss} = 7~pF$ 5)产生感应电流($I_{miller} = C_{rss} times dv/dt$)。该电流流经栅极电阻,可能在栅极上产生超过 $V_{GS(th)}$(典型值2.7V 5)的正电压,导致“寄生导通”(Parasitic Turn-on),进而引发上下管直通(Shoot-through)的灾难性故障。采用-5V的负偏压可提供额外的5V安全裕量,确保栅极电压始终保持在 $V_{GS(th)}$ 以下,有效防止寄生导通。

设计决策 2.3:栅极驱动器(见第四章)必须是隔离的,并且必须为其提供一个能稳定输出-5V和+18V的双极性(Bipolar)偏置电源 。

III. 系统架构与拓扑(Architecture and Topology)

A. 功率拓扑结构

基于设计目标,功率级采用标准的三相电压源逆变器(VSI)拓扑(三相半桥)。根据第二章(设计决策2.2)的结论,每个半桥由一个B3M040065R SiC MOSFET和一个反并联(Anti-parallel)的外部SiC SBD(续流二极管)构成。

B. 物理架构:分离与堆叠

在IMD的紧凑空间内,电磁兼容性(EMC)是决定设计成败的关键。B3M040065R的高速开关(高 $dv/dt$)是一个强大的噪声源 12,而伺服控制系统依赖于高精度的模拟信号(如电流反馈 21)和高稳定性的MCU 。

将高噪声的功率开关(B3M040065R)和高敏感的控制电路(MCU)放置在同一块PCB上,会导致灾难性的噪声耦合,使精确的伺服控制不可能实现 。

设计决策 3.1:必须采用“关注点分离”(Separation of Concerns)的物理架构。本设计将采用双PCB或三PCB的堆叠架构。

PCB 1:功率板(Power Stage Board - PSB):

组件:6x B3M040065R 5,6x SiC SBDs,6x 隔离栅极驱动器IC(见第四章),DC-Link电容(见第八章),以及所有隔离传感器(电流、电压、温度)的“热端”(Hot Side)。

设计焦点:最小化寄生电感(见第四章),最大化热传导(见第六章)。

PCB 2:控制板(Control Board - CB):

组件:主控制器MCU(见第八章),通信接口(例如EtherCAT/CAN 29),编码器接口 ,传感器(的“冷端”),以及为整个系统(包括PSB的隔离电源)供电的辅助电源。

设计焦点:信号完整性,EMI防护 。

(可选) PCB 3:接口板(Interface Board):如 19 中所述,可以增加一个底板,专门用于处理DC-Link电源和电机相线的重型连接器和传感。

C. 板间接口与隔离传感

PSB(热端)和CB(冷端)的物理分离,意味着它们之间的所有通信都必须是隔离的。

控制路径 (CB -> PSB):6路隔离的PWM信号(通过栅极驱动器IC实现)。

反馈路径 (PSB -> CB):

电流传感:必须采用隔离方案。传统的低侧分流电阻方案会污染功率地和控制地,在IMD中不可接受。

推荐方案:使用隔离式放大器(如TI的AMC1301 27)配合高精度的分流电阻(Shunt),或使用霍尔效应(Hall-effect)电流传感器。

电压传感:必须使用隔离式放大器(如AMC1301)来监测DC-Link总线电压。

温度传感:绝对必要。必须在B3M040065R的PCB焊盘附近放置NTC热敏电阻,并通过隔离放大器(如AMC1311 28)或隔离的数字协议将信号传回MCU。这是实现过热保护、功率降额和Rds(on)补偿的基础。

PSB和CB之间的连接器必须是高可靠性、耐振动、且具有高隔离度的板对板连接器。

IV. 功率级PCB布局:SiC性能的基石 (The Critical Layout)

本章是整个设计的核心。B3M040065R的SiC性能(低损耗、高速度)完全依赖于PCB布局的质量。错误的布局将导致器件性能灾难性下降或因过压而损坏。

A. B3M040065R的开尔文源极(Kelvin Source)黄金法则

B3M040065R在TO-263-7封装中提供了两个独立的源极连接:Pin 2(开尔文源极)和Pins 3-7(功率源极)。正确使用这是释放其性能的第一法则 。

问题所在:在开关瞬态(Turn-on/off)期间,巨大的电流变化率($di/dt$)流过功率源极(Pins 3-7)及其PCB走线和键合丝。这段路径上存在不可避免的“共源电感”(Common Source Inductance, $L_{csi}$)15。这个$L_{csi}$会产生一个反向电压 $V_{csi} = L_{csi} times di/dt$。

错误的做法:如果将栅极驱动器的返回路径(GND)连接到功率源极(Pins 3-7),则实际的栅极-源极电压将变为 $V_{gs(actual)} = V_{driver} - V_{csi}$。这个 $V_{csi}$ 电压会对抗栅极驱动信号,极大地减慢开关速度(增加开关损耗 $E_{on}/E_{off}$),并引起严重的栅极振荡。

黄金法则(设计法则 4.1):

栅极驱动环路(Gate Loop)的返回路径必须且只能连接到Pin 2 (开尔文源极)。

功率环路(Power Loop)的返回路径必须连接到Pins 3-7 (功率源极)。

Pin 2和Pins 3-7绝不能在靠近器件封装的地方短路 。它们只应在DC-Link电容的负端或星形接地点处汇合。

违反此法则将使B3M040065R的SiC性能完全失效,使其表现得像一个缓慢的、高损耗的IGBT。

B. 栅极驱动环路(Gate Loop)布局

目标是最小化栅极环路寄生电感($L_{g_loop}$)。该环路路径为:栅极驱动器IC (OUT) -> 栅极电阻 ($R_G$) -> B3M040065R Pin 1 (Gate) -> B3M040065R Pin 2 (Kelvin Source) -> 栅极驱动器IC (GND)。

设计法则 4.2(布局策略):

IC放置:栅极驱动器IC(见本章C节)应尽可能靠近B3M040065R。

$R_G$ 放置:栅极电阻 $R_G$ 应放置在紧贴 Pin 1 (Gate) 的地方,以有效抑制栅极振荡。

分层布线:必须采用多层PCB(至少4层)。强烈推荐采用 30 中(图6)的布局策略:

L1 (Top Layer):放置驱动器IC、 $R_G$ 和B3M040065R。走线从 $R_G$ 到 Pin 。

L2 (Inner Layer 1):放置一个专用的返回平面(GND Plane),该平面通过过孔连接到Pin 2 (Kelvin Source)。

环路面积:栅极环路的面积被L1(走线)和L2(平面)之间的垂直距离(即PCB介质厚度)所定义,从而实现最小环路电感 16。

去耦:驱动器IC的VCC/VEE(+18V / -5V)去耦电容必须紧贴IC的电源引脚。

C. 栅极驱动器(Gate Driver)IC选型

根据设计决策2.3,驱动器IC必须满足以下要求:

隔离:必须是隔离型驱动器,以处理半桥的浮动高侧(High-side)电压 。

Vgs范围:必须支持-5V / +18V的双极性供电,并具有专为SiC优化的UVLO(欠压锁定)阈值(例如UVLO V_on > 15V)。

CMTI:必须具有极高的共模瞬变抗扰度(CMTI),典型值应 > 100 V/ns,以抵抗SiC的高$dv/dt$ 。

米勒钳位(Miller Clamp):必须具备此功能 ,以在关断期间主动将栅极钳位到负轨(-5V),为防止寄生导通提供第二重保护。

表格 4.1:推荐的SiC隔离栅极驱动器IC

| 型号 | 制造商 | Vgs范围 (推荐) | CMTI (Typ) | 关键特性 | 来源 |

|---|---|---|---|---|---|

| STGAP2SiCS | STMicro | 高达 26V | > 100 V/ns | 专为SiC优化(UVLO=15.5V), 米勒钳位 | |

| 1ED314xMU12F | Infineon | -10V / +18V | > 300 kV/$mu$s | 极高CMTI, DESAT保护, 米勒钳位 | |

| UCC21530 | TI | 5V - 25V | > 100 V/ns | 4A/6A峰值电流, 可配置, TIDA-00366中使用 | |

| 1EDB7275F | Infineon | (EiceDRIVER) | 300 V/ns | 单通道, 3kVrms隔离 |

D. 功率环路(Power Loop)布局

功率环路(DC-Link电容 -> 上管 -> 下管 -> 电容)的寄生电感($L_{loop}$)是B3M040065R的头号杀手。在关断(Turn-off)期间, $L_{loop}$ 上的电压过冲 $V_{overshoot} = L_{loop} times di/dt$ 会叠加到V_DC总线上。

设计法则 4.3(垂直环路):必须采用垂直功率环路布局,以实现最小化的 $L_{loop}$。一份针对TO-263-7封装的布局研究 30 提供了直接的仿真对比:

水平环路(Horizontal Loop - 驱动器和电容在同一层):$L_{loop} approx 19~nH$。

垂直环路(Vertical Loop - 利用内层作为返回路径):$L_{loop} approx 5.7~nH$。

垂直环路的寄生电感降低了70%,这为B3M040065R提供了巨大的安全裕量,并允许其更快地开关(更高的$di/dt$),从而降低开关损耗 $E_{off}$ 。

设计法则 4.4(4层板布局):

L1 (Top Layer):放置B3M040065R、SBDs以及本地的高频去耦电容(C0G MLCC - 见第八章)。

L2 (Inner Layer 1):作为DC-Link的GND/负极平面。

L3 (Inner Layer 2):作为DC-Link的V+/正极平面。

L4 (Bottom Layer):放置大容量DC-Link电容(如果使用)和与电机壳体的热连接。

电流路径:L3 (V+) -> L1 (MLCC) -> L1 (B3M040065R Drain) ->... (开关节点)... -> L1 (下管 B3M040065R Power Source) -> L1 (MLCC) -> L2 (GND)。环路面积被L1和L2之间的PCB厚度所限制,电感最小 。

V. 性能建模:损耗、效率与开关频率($f_{sw}$)的权衡

本节将建立一个基于B3M040065R数据表的功率损耗模型,以确定IMD设计的最佳开关频率($f_{sw}$)。

A. 功率损耗模型(三相逆变器)

总损耗 $P_{total} = P_{cond} + P_{sw} + P_{gate} + P_{aux}$。

1. 传导损耗(Conduction Losses, $P_{cond}$)

传导损耗由MOSFET的 $R_{DS(on)}$ 和SBD的正向压降 $V_F$ 决定。

$P_{cond} approx 6 times I_{rms_phase}^2 times R_{DS(on)}(T_j) times Duty_Cycle_{MOSFET} + 6 times (V_{F_SBD} times I_{avg_SBD} + dots)$

(注:精确计算需使用SVPWM的解析方程 37)

关键输入:$R_{DS(on)}(T_j=175^circ C) = 55~mOmega$ 5。

2. 开关损耗(Switching Losses, $P_{sw}$)

开关损耗与 $f_{sw}$ 成正比。

$P_{sw} = 6 times (E_{on_SBD} + E_{off_SBD}) times f_{sw} times (frac{V_{bus_actual}}{V_{bus_test}}) times (frac{I_{D_actual}}{I_{D_test}})$

关键输入 5:

$E_{on_SBD} = 56~mu J$

$E_{off_SBD} = 36~mu J$

$E_{total_cycle} = 92~mu J$

3. 栅极驱动损耗(Gate Drive Losses, $P_{gate}$)

驱动6个MOSFET的栅极所需的能量,也与 $f_{sw}$ 成正比 。

$P_{gate_total} = 6 times Q_G times (V_{GS_on} - V_{GS_off}) times f_{sw}$

关键输入:$Q_G = 60~nC$ 5, $Delta V = (18V - (-5V)) = 23V$。

$P_{gate_total} = 6 times 60nC times 23V times f_{sw} = 8.28 times 10^{-6} times f_{sw}$

B. 开关频率($f_{sw}$)的优化与权衡

$f_{sw}$ 是伺服性能、热量和EMI之间的核心权衡点:

伺服性能(Pro):高 $f_{sw}$(>20kHz)是高性能伺服的理想选择。它提供了高电流环路带宽(实现高动态响应)、低转矩脉动(平稳性),并消除了人耳可听见的噪音(>20kHz)3。

热量(Con):$P_{sw}$ 和 $P_{gate}$ 与 $f_{sw}$ 成正比。在热受限的IMD中,每一瓦的热量都必须被计入 。

EMI(Con):高 $f_{sw}$(及其谐波)会加剧EMI问题 。

无源器件(Pro):高 $f_{sw}$ 允许使用更小、更轻的DC-Link电容和EMI滤波器,这对于IMD的空间至关重要 。

设计决策 5.1:

排除 < 16 kHz:虽然8-16kHz在传统驱动器中很常见 ,但这会产生伺服应用无法接受的噪音和转矩脉动。

排除 > 50 kHz:这将导致开关损耗($P_{sw}$)主导总损耗,使得在IMD的热约束下无法实现散热 3。

推荐 $f_{sw}$ 范围:16 kHz - 32 kHz。这个范围是伺服性能(高带宽、超声波)和热管理($P_{sw}$ 可控)之间的最佳折衷 。

C. 预期损耗预算表

为了量化这一权衡,下表估算了B3M040065R三相逆变器在不同 $f_{sw}$ 下的损耗。

假设条件:Tj=175°C, V_DC=400V, I_phase_rms=20A (SVPWM, M=1.0, PF=0.9), $P_{cond}$ 估算为 20W 左右, $P_{sw}$ 基于20A/400V的 $E_{total}$ (92µJ) 进行线性外推。

表格 5.1:B3M040065R三相逆变器预期损耗预算

| 开关频率 (fsw) | Pcond (6x MOSFET) | Psw (6x MOSFET) | Pgate (6x Drivers) | Ptotal_loss (估算) | Psw 占总损耗比例 |

|---|---|---|---|---|---|

| 16 kHz | ~20 W | 8.8 W | 0.13 W | ~29 W | ~30% |

| 32 kHz | ~20 W | 17.7 W | 0.26 W | ~38 W | ~47% |

| 50 kHz | ~20 W | 27.6 W | 0.41 W | ~48 W | ~58% |

| 100 kHz | ~20 W | 55.2 W | 0.83 W | ~76 W | ~73% |

设计决策 5.2(基于表格):

32 kHz 是临界点:在32kHz时,开关损耗 (17.7W) 开始接近并赶上导通损耗 (~20W)。

50 kHz 是不可行的:在50kHz时,开关损耗 (27.6W) 主导了总损耗(占比~58%)。总热量 (48W) 对于一个紧凑的IMD来说散热极其困难。

设计目标:本设计将以32 kHz43 为目标 $f_{sw}$。这提供了卓越的伺服性能(超声波频段),同时将热负荷控制在可管理的水平。

热设计目标:热管理系统(见第六章)必须能够可靠地散发约 38W 的热量。

VI. 核心挑战(一):热力-机械集成设计 (Thermo-Mechanical)

本章解决IMD最核心的物理挑战:在高温和高振动的电机壳体环境中,将第五章计算出的38W功率损耗安全、可靠地散发出去。

A. 散热策略:以电机壳体为核心散热器

IMD的核心策略是将驱动器PCB(特别是PSB)安装在电机端盖或定子表面,利用电机壳体作为主散热器 2。

热量传递的路径(热阻网络模型 )为:

$T_j rightarrow R_{th(jc)} rightarrow T_{case} rightarrow R_{th(cs)} rightarrow T_{sink} rightarrow R_{th(sa)} rightarrow T_{ambient}$

$T_j$: B3M040065R 结温 (目标 < 175°C)。

$R_{th(jc)}$: 结到壳热阻(已知 =0.65 K/W)。

$R_{th(cs)}$:关键瓶颈。这是从B3M040065R外壳(背面Drain)-> PCB -> TIM/灌封胶 -> 电机壳体(Sink)的热阻。

$T_{sink}$: 电机壳体温度(可能已高达85°C)。

B3M040065R是TO-263-7表面贴装器件 5,其散热片(Drain)在背面。热量必须从B3M040065R的背面Drain -> 焊接到PCB的铜焊盘 -> 通过PCB的热通孔(Thermal Vias) -> 传递到PCB的另一面 -> 再传递到电机壳体。

设计法则 6.1:PCB的B3M040065R焊盘下方必须密集填充热通孔(Thermal Vias)。PCB本身应使用高导热率的基板(例如,75提到的Tlam导热PCB系统)或厚铜层(>2oz),以最小化PCB自身的热阻。

B. 机械可靠性:振动与热膨胀(CTE)失配

IMD设计面临两大机械威胁:

振动:电机运行伴随的持续机械振动和冲击,会对PCB焊点、电容器引线和IC封装造成疲劳损伤 。

CTE失配(热膨胀系数):这是一个更隐蔽但更致命的威胁。

PCB (FR4) CTE $approx 14-17$ ppm/°C。

电机壳体(通常为铸铝)CTE $approx 23$ ppm/°C 17。

当系统从室温(25°C)运行到高温(例如125°C,$Delta T=100^circ C$),铝制外壳的膨胀远大于PCB。

如果PCB被刚性地(例如,用螺钉和硬质TIM垫片)固定到外壳上,这种差异化的膨胀将对B3T_D065R的焊点施加巨大的剪切应力,最终导致焊点疲劳和开裂 。

C. 解决方案:导热灌封胶(Potting)——“一石三鸟”之计

传统的散热垫片(Gap Pad 49)或导热膏(Grease)无法同时解决上述所有问题。

设计决策 6.2:必须采用柔性导热灌封胶(Thermally Conductive Potting Compound)对整个功率板(PSB)进行灌封 。

这是一种“一石三鸟”的解决方案,可同时解决热量、振动和CTE失配:

抗振动(解决挑战1):灌封胶(通常是硅基或环氧基)将所有组件(电容、IC、B3M040065R)牢固地固定在PCB上,形成一个坚固的、防潮的整体,使其免受机械振动和冲击的影响 。

解耦CTE(解决挑战2):选择柔性(低模量)的硅基导热灌封胶 。这种材料(例如Shore A )可以作为应力缓冲层,吸收PCB(FR4)和电机壳体(铝)之间的热膨胀差异,从而保护B3M040065R的焊点免受剪切应力。

3D散热(解决散热):导热灌封胶 填充了所有空隙,并提供 2.0 W/mK 54 至 4.0 W/mK 52 的导热率。它不仅将热量从PCB底部传导到外壳,还从B3M040065R、SBDs和DC-Link电容的顶部和侧面提取热量,并将其传导到外壳的侧壁。这创建了一个“3D全方位散热”路径,远优于传统TIM的“2D单面散热” 。

表格 6.1:热界面材料(TIM)与导热灌封胶对比

| 方案 | 导热率 (W/mK) | CTE失配处理 | 振动处理 | 散热路径 | 来源 |

|---|---|---|---|---|---|

| 导热垫片 (Gap Pad) | 1.0 - 7.5 | 良好(柔性) | 差(组件仍可能振动) | 2D(PCB底部 -> 外壳) | |

| 导热灌封胶 (Potting) | 2.0 - 4.0 | 优秀(柔性硅胶) | 优秀(完全封装) | 3D(全方位 -> 外壳) |

VII. 核心挑战(二):EMI/EMC 抑制策略

A. IMD中的EMI特性:一个反转的问题

在传统设计中,EMI的主要问题是驱动器(在电柜中)通过长电机电缆辐射噪声,电缆充当了高效的天线 。

而在IMD设计中,B3M040065R的高$dv/dt$ 12 被完全封闭在导电的电机外壳内。金属外壳本身就是一个理想的EMI屏蔽(法拉第笼)。

因此,辐射EMI(Radiated EMI)问题在很大程度上被解决了。问题反转为:

内部耦合:如何防止EMI(来自功率板PSB)污染同一外壳内的敏感控制板(CB)。

传导EMI:如何防止EMI通过DC电源线传导回电网 。

B. PCB布局层面的EMI抑制(PSB功率板)

抑制EMI的最佳方法是在源头(即PCB布局)上解决它。

接地(Grounding):采用 中提到的多层接地平面和接地拼接过孔(stitching vias)。如第四章所述,PSB不应有“一个”接地层,而是有多个严格隔离、并在指定点汇合的参考地(驱动地、功率地、模拟地)。

阻抗平衡:采用 中提到的对称布线(symmetric routing)。使高侧和低侧的走线尽可能镜像对称,利用反向电流环路产生的磁场对消 。

$dv/dt$节点最小化:将具有高$dv/dt$的节点(即B3M040065R的Drain(背面)和SBD阳极之间的连接,即“开关节点”Switch Node)的PCB覆铜面积减至最小。这个节点是共模(CM)噪声的最大来源 。

C. 控制板(CB)的EMI防护

控制板(CB)必须被视为一个“受害者”,需要被严密保护 。

物理隔离:与PSB保持最大物理距离(例如,在堆叠的两端)。

分区(Partitioning):在CB上,严格划分“脏”区域(接收来自PSB的隔离信号的接口)和“干净”区域(MCU、时钟、模拟电路)。

屏蔽(Shielding):在CB上使用本地金属屏蔽罩 覆盖MCU和时钟电路。

滤波(Filtering):所有进入CB的I/O和电源线都必须经过EMI滤波器(如磁珠、TVS)。

D. 外部接口EMI滤波器

必须在DC电源线进入电机壳体的位置设计一个高性能的共模(CM)和差模(DM)EMI滤波器 。由于SiC的$f_{sw}$(32kHz)及其高$dv/dt$,EMI噪声将扩展到MHz甚至几十MHz的频率范围 。该滤波器必须是针对SiC优化的宽带滤波器 。

VIII. 关键外围组件选型(耐高温与高振动)

A. 125°C工作等级:非易失性设计规则

IMD设计的环境温度($T_{ambient}$)由电机壳体决定,可能高达85°C甚至更高 。一个85°C额定的工业级MCU在85°C的环境中,一旦通电,其自身功耗产生的温升将使其结温立即超过其额定值。

设计法则 8.1:本设计中使用的所有半导体和关键无源器件(MCU、驱动器、LDO、传感器、电容),必须具有125°C的最低工作温度额定值(例如AEC-Q100 Grade 1或更高)。

B. DC-Link 电容器:MLCC替代薄膜电容

DC-Link电容是IMD中除SiC外的最大、最关键、也是最脆弱的组件 。

选项1(排除):高温薄膜电容(Film Capacitors)。

优点: 良好的自愈性,高纹波电流能力 。

缺点: 125°C是其绝对上限 。体积庞大,难以集成 。在高振动下,其引线和焊点是主要的机械故障点 68。

选项2(推荐):C0G高温MLCC(多层陶瓷电容)。

优点:

耐高温:C0G MLCC可在150°C甚至260°C下运行 。

低ESL/ESR:频率特性远优于薄膜电容,是吸收SiC高频纹波的理想选择 。

尺寸/布局:体积微小 ,可以实现分布式DC-Link。

可靠性:SMT器件,重量轻,具有极高的抗振动性 。

缺点: 需要大量并联以达到所需的总电容($mu$F级别)。

设计决策 8.2(分布式MLCC):放弃传统的大体积薄膜电容。本设计将采用基于C0G MLCC的分布式DC-Link总线。将数十个高压(1000V)C0G MLCC 70 阵列式地放置在PSB的L1和L4层,紧邻B3M040065R和SBD。

这是一个协同解决方案:

电气(第四章):它们构成了垂直功率环路 30 的一部分,提供了最低的 $L_{loop}$。

机械(第六章):它们是SMT器件,将被导热胶完全灌封,具有完美的抗振动性。

热力(第八章):它们极耐高温 ,解决了IMD中的关键寿命问题 。

D. 寿命评估

铝电解电容的寿命极度依赖温度(10°C法则 71),在IMD的高温环境中其寿命将急剧缩短。

设计法则 8.3:本设计完全禁止使用铝电解电容。所有辅助电源(例如从V_DC产生+18V/-5V的电源)也必须使用MLCC或固态电容。可靠性模型将基于MLCC的老化曲线 69 和Arrhenius模型(适用于半导体)71,以高温(例如105°C $T_{ambient}$)下的振动和热循环曲线为输入。

IX. 综合设计建议与执行摘要

基于对B3M040065R器件特性和电机集成(IMD)严苛环境的深入分析,本报告提出以下“八大黄金法则”,这是成功设计一款高可靠性、高性能IMD伺服驱动器的必要条件。

A. 总结设计法则(Golden Rules)

器件选型:必须围绕B3M040065R 5 +外部SiC SBD(续流二极管)构建功率级。严禁使用B3M040065R的体二极管进行续流,以避免因高$Q_{rr}$ (235 nC @ 175°C) 5 导致的热负荷($E_{on}$ 增加66% )失控。

架构:必须采用双PCB堆叠(或多PCB)架构。将高噪声的功率板(PSB)和高敏感的控制板(CB)物理分离 。所有板间信号必须隔离 27。

栅极驱动:必须使用-5V / +18V双极性供电 。栅极驱动器IC必须是隔离的,具有高CMTI(>100V/ns )和米勒钳位(Miller Clamp)功能 24,并为SiC优化UVLO阈值。

布局:必须严格遵守开尔文源极(Pin 2)规则用于栅极驱动返回 。必须采用多层PCB($geq$4L)和垂直功率环路布局,将功率环路寄生电感($L_{loop}$)控制在 < 10nH,以防止650V的B3M040065R发生过压损坏 。

热力-机械:必须采用柔性导热硅胶灌封(导热率 > 2 W/mK 54)。这是同时解决散热、抗振动 和CTE热膨胀失配 的唯一可行方案。

DC-Link:必须使用分布式的高温(150°C)C0G MLCC阵列 。严禁使用薄膜电容(体积、振动)或铝电解电容(高温寿命)。

组件等级:所有组件(MCU、驱动器、传感器、电容)必须额定在125°C或更高 18。85°C的工业级组件在IMD应用中无效。

开关频率:$f_{sw}$ 应设置在16 kHz - 32 kHz之间 43。这平衡了伺服性能(高带宽、超声波)和热负荷(在32kHz时约38W)[见表格 5.1]。

B. 最终物料清单(BOM)亮点

表格 9.1:关键BOM组件(125°C IMD设计)

| 组件类别 | 选型 | 关键规格 | 来源 |

|---|---|---|---|

| 功率MOSFET | 6x Basic B3M040065R | 650V / 55m$Omega$ @ 175°C / TO-263-7 | |

| 续流二极管 | 6x SiC SBD | 650V / 30A (匹配) | (设计决策 2.2) |

| 栅极驱动器 | 6x STGAP2SiCS | 125°C / >100V/ns CMTI / 米勒钳位 | |

| DC-Link电容 | N x C0G MLCC | 1000V / 150°C / SMT / 低ESL | |

| 控制器MCU | 1x dsPIC33 (HT系列) | 150°C/ Motor Control DSP / CAN | |

| 隔离传感 | 4x AMC13xx | 增强隔离 / 125°C / 电流&电压传感 | |

| 封装材料 | 1x 导热灌封胶 | 硅基 / >2 W/mK / 柔性 (Shore A < 70) |

C. 结论

深圳市倾佳电子有限公司(简称“倾佳电子”)是聚焦新能源与电力电子变革的核心推动者:

倾佳电子成立于2018年,总部位于深圳福田区,定位于功率半导体与新能源汽车连接器的专业分销商,业务聚焦三大方向:

新能源:覆盖光伏、储能、充电基础设施;

交通电动化:服务新能源汽车三电系统(电控、电池、电机)及高压平台升级;

数字化转型:支持AI算力电源、数据中心等新型电力电子应用。

公司以“推动国产SiC替代进口、加速能源低碳转型”为使命,响应国家“双碳”政策(碳达峰、碳中和),致力于降低电力电子系统能耗。

需求SiC碳化硅MOSFET单管及功率模块,配套驱动板及驱动IC,请添加倾佳电子杨茜微芯(壹叁贰 陆陆陆陆 叁叁壹叁)

通过严格遵循上述基于B3M040065R特性推导出的设计法则,设计一款高度可靠、高性能、并完全集成在电机壳体内的伺服驱动器在工程上是完全可行的。其核心挑战已从传统的“电气”设计转向了“热力-机械”和“EMI”的多物理场(Multi-Physics)耦合与集成问题。成功的关键在于通过采用SiC SBD、125°C组件、C0G MLCC DC-Link和柔性导热灌封等技术,在设计阶段即系统性地解决热量、振动和寄生参数这三大制约因素。

审核编辑 黄宇

-

伺服驱动器

+关注

关注

22文章

548浏览量

33300 -

碳化硅

+关注

关注

25文章

3303浏览量

51705

发布评论请先 登录

倾佳电子市场报告:国产SiC碳化硅功率器件在全碳化硅户用储能领域的战略突破

倾佳电子T型三电平逆变器应用综合分析:B3M010C075Z与B3M013C120Z碳化硅MOSFET黄金组合的性能与价值

倾佳电子SiC厨房革命:B3M042140Z MOSFET取代RC-IGBT在电磁炉应用中的技术与商业分析

深度分析650V国产碳化硅MOSFET的产品力及替代高压GaN器件的潜力

倾佳电子基于B3M040065R碳化硅MOSFET的电机集成伺服驱动器(IMD)系统设计白皮书

倾佳电子基于B3M040065R碳化硅MOSFET的电机集成伺服驱动器(IMD)系统设计白皮书

评论