英国剑桥和德国希尔登市——2018年8月

UltraSoC日前宣布:公司已与SEGGER达成合作伙伴关系,以在UltraSoC集成化的系统级芯片(SoC)监测和分析环境中为J-Link调试探针提供支持。SEGGER的J-Link探针是业界最广泛使用的调试探针之一,支持包括RISC-V以及当前和过往代系的ARM内核在内的常用处理器平台的调试。此次的双方合作,使SoC开发人员能够通过UltraSoC灵活的片上监测和分析基础设施在调试时通过同一界面轻松地访问J-Link。

UltraSoC致力于让设计人员的工作变得更便捷:通过提供一种开放的、易于熟悉的且与内核架构供应商无关的环境,以满足每位工程师在处理器架构、开发工具和硬件方面的偏好。通过支持其框架内最广泛的平台和工具,UltraSoC为更多的设计人员开启了其嵌入式分析平台优势的大门,可以缩短开发时间、加快调试过程、降低风险和成本。

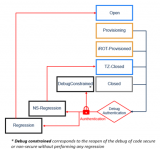

对SEGGER J-Link探针全面支持的集成意味着探针配置和调试监控可以在单一环境下进行,在使用UltraSoC的嵌入式分析功能的时候,设计师们将能够在设计流程中和随后的现场中深入了解CPU的运行情况,以作为更广泛的系统设计的一部分。

UltraSoC首席执行官Rupert Baines评论道:“像所有的工程师一样,芯片设计人员也希望能够为所从事的工作选择最好的工具。在UltraSoC,我们致力于与业内一流的硬件和软件提供商合作,来确保我们共同的客户可以将其生产能力和创新潜力最大化。作为我们行业中的领军企业之一,与SEGGER的合作完全符合我们的战略。随着我们越来越多的客户使用开源RISC-V平台,对灵活性和开放性的需求显著增加。这个行业正在发生变化,现在整个生态系统内的协作比以往任何时候都更为重要。”

SEGGER销售与市场营销总监Harald Schober补充道:“我们很高兴能够与UltraSoC一起携手合作——我们共同致力于提供最好的工具,来支持那些采用核心专利和开源CPU架构的设计师。我们两家公司已经共享了客户,期望这一合作将在RISC-V及其它平台上也能够快速成功。在UltraSoC环境中支持对SEGGER J-Link功能的访问是非常有意义的。”

SEGGER是为嵌入式系统提供软件、硬件和开发工具的业界领先供应商之一,公司为开发人员在整个开发流程中提供价格合理的、高质量的、灵活的、易于使用的工具和中间件组件。公司于2004年将J-Link引入到ARM市场,并成为为ARM开发人员提供行业标准调试探针的供应商。由于其易于使用,运行快速且可靠,J-Link系列的探针保持着行业领导者地位,同时可为设计人员提供一种可扩展的、价格合理的且功能齐全的解决方案。

SEGGER一直在不断地扩大其支持的内核架构的范围,包括其最近增加了对RISC-V的支持。在大多数情况下,同时在多平台操作,J-Link仅需要一个微小的软件/固件更新:当切换到一个不同的支持CPU产品系列或工具链时,没必要购买一份全新的J-Link探针或一个新的授权。所有的J-Link型号都是完全兼容的,提供无限制的免费升级,且用户在升级到更高端型号的时候可以即插即用。

关于SEGGER

SEGGER Microcontroller是为嵌入式系统提供软件、硬件和开发工具的全系列供应商。公司提供的支持覆盖整个开发流程,其中都提供价格合理、高质量、灵活且易于使用的工具和组件。SEGGER为安全通信及数据和产品安全提供解决方案,从而满足快速演进的物联网(IoT)的需要。公司由Rolf Segger于1992年成立,是一家稳步发展的私人公司。SEGGER的总部位于德国,在美国办公室设在波士顿地区以及硅谷,并在各大洲均有分销商,可在全球范围内提供全系列产品。更多信息,请访问:www.segger.com

关于UltraSoC

UltraSoC是一家为系统级芯片(SoC)提供内部分析及监测技术的先锋企业,正是这些SoC驱动了当今各种电子产品的创新。产品设计人员可以使用UltraSoC的嵌入式分析技术为产品增加先进的网络安全、功能安全以及性能微调功能;与此同时该技术还能帮助企业更好地应对不断升级的系统复杂性难题以及日益严苛的缩短上市时间需求。UltraSoC的技术以半导体知识产权(semiconductor IP)和软件的形式提供给客户,最终应用覆盖了消费电子、计算和通信等行业。

-

嵌入式

+关注

关注

5186文章

20143浏览量

328666 -

RISC-V

+关注

关注

48文章

2792浏览量

51856 -

UltraSoC

+关注

关注

0文章

40浏览量

18303

原文标题:UltraSoC为嵌入式调试和分析环境添加SEGGER的J-Link调试探针

文章出处:【微信号:Technomics,微信公众号:华兴万邦技术经济学】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

RISC-V 的平台思维和生态思维

【微五科技CF5010RBT60开发板试用体验】开发环境搭建之——使用J-Link调试

RISC-V和ARM有何区别?

SEGGER J-Link调试器支持Allegro微控制器

RISC-V架构CPU的RAS解决方案

如何将MCUXpresso和MCU LINK_PRO置于J-Link仿真模式?

芯来科技携手芯芒科技发布RISC-V CPU系统仿真平台

如何通过J-Link实现STM32H5控制调试端口

SEGGER J-Link和Flasher工具支持意法半导体汽车微控制器

Arm与RISC-V架构的优劣势比较

如何通过J-Link向目标系统供电

RISC-V架构及MRS开发环境回顾

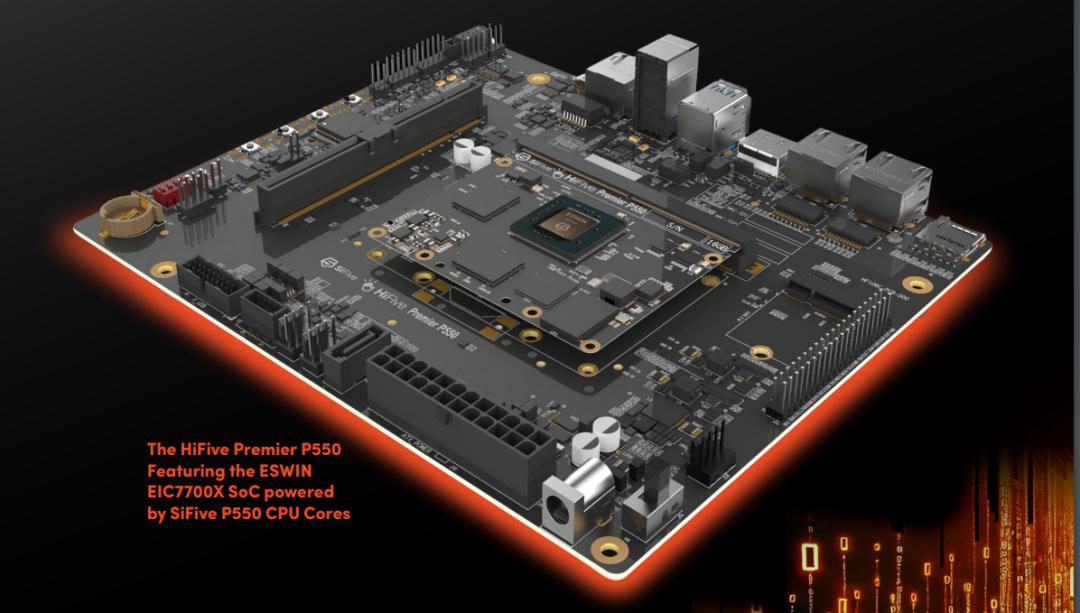

SiFive 推出高性能 Risc-V CPU 开发板 HiFive Premier P550

J-Link探针支持RISC-V、ARM和其它CPU平台

J-Link探针支持RISC-V、ARM和其它CPU平台

评论