在 RISC-V 架构的普及浪潮中,嵌入式领域的成功早已众人皆知,但高性能计算(HPC)始终是其难以突破的 “高地”。算能SOPHON SG2044的出现打破了僵局。国际权威技术媒体发布的深度评测《Is RISC-V ready for High Performance Computing?》,更以严苛标准对SG2044展开全维度性能验证,横向量测对比其前代产品SG2042及主流x86/ARM架构。

双关键升级破局 HPC 瓶颈

SG2044 的性能飞跃,源于对前代SG2042 的架构创新 ——RVV v1.0 向量指令集支持与增强型内存子系统,这也是 HPC 场景最核心的技术需求。

RVV v1.0:让 RISC-V 向量计算 “能用、好用”

不同于 SG2042 仅支持 RVV v0.7.1,SG2044 的 C920v2 核心直接兼容 RVV v1.0 标准,可直接使用 GCC 15.2、LLVM 等主流编译器实现自动向量化。

这意味着,开发者无需再为适配 RISC-V 向量计算修改代码,直接沿用主流 HPC 软件栈即可发挥 SG2044 的算力优势,大幅降低了 RISC-V 进入 HPC 领域的门槛。

片上高速内存 赋能HPC场景

SG2042 的内存 subsystem ,在 SG2044 上被彻底重构。内存控制器从 4 个增至 32 个,内存通道从 4 条扩至 32 条,同时升级至 LPDDR5X-8533 内存,带来了颠覆性的内存性能:

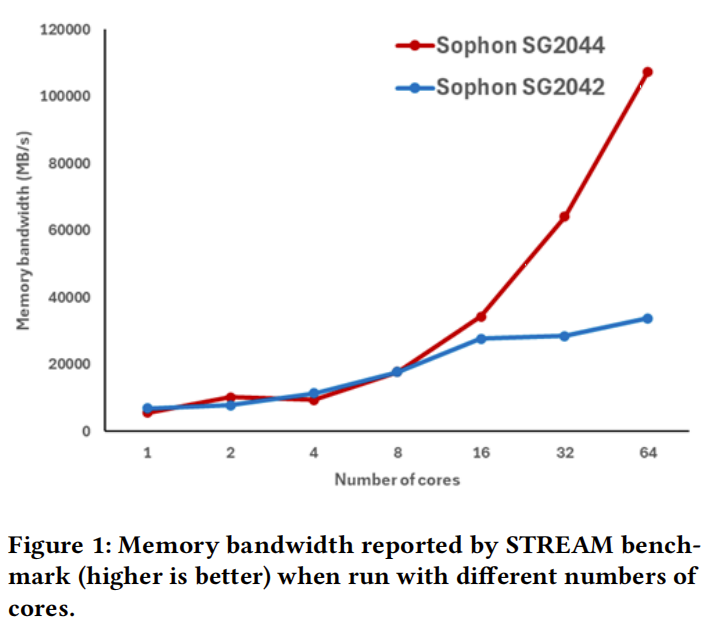

- 内存带宽方面,SG2044 在 64 核时通过 STREAM 基准实现超 3 倍于 SG2042 的带宽,且核心数越多,优势越明显(8 核内两者带宽相近,64 核时 SG2044 彻底拉开差距);

- 内存延迟从 SG2042 的 98ns 降至 68ns,降幅达 35%,在CG(共轭梯度)基准(不规则内存访问)中,64 核性能达 7728.80 Mop/s,较 SG2042 的 3508.95 Mop/s 提升 2.2 倍;

更关键的是,SG2044 所有核心处于单一 NUMA 区域,避免了多 NUMA 节点间的数据传输延迟,在数据密集型 HPC 场景中,降低了内存瓶颈导致的性能损耗。

“周边配置”大升级

除了核心升级,SG2044 还补全了 HPC 所需的“周边配置”:

- 核心频率 2.6GHz(测试值,SG2042 是 2GHz);

- 支持 PCIe Gen5(SG2042 是 Gen4),能接更快的显卡、存储;

- 2025 年中已经集成到 Linux 6.16 主线内核,系统兼容性拉满。

多核算力突破性跃升:HPC 基准测试数据提升

论文选择了NAS Parallel Benchmark(NPB),这是超算领域的“标准考卷”,包含 8 个测试项:5 个“内核”(基础算法)+3 个“伪应用”(模拟真实科学计算),并基于此进行实测验证:

力压其他 RISC-V CPU(单核心对比)

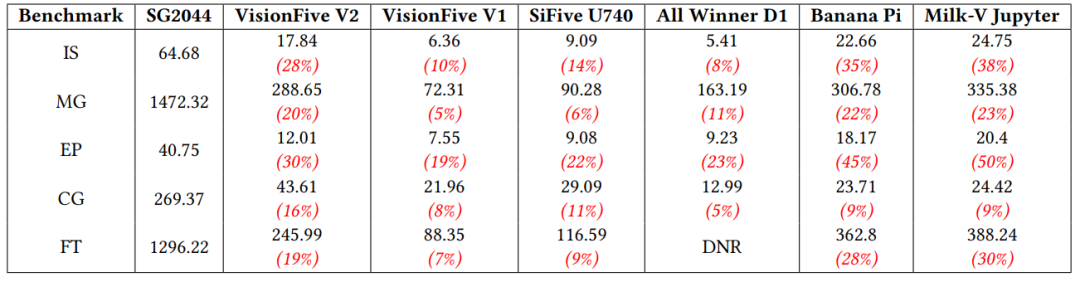

单核条件下,论文对比了目前主流的 RISC-V CPU(比如 VisionFive V2、Banana Pi 等),以 NPB 的 5 个内核进行测试,结果如下:

SG2044 的 C920v2 核心,单核性能全面碾压目前主流的 RISC-V CPU。即使是同样支持 RVV v1.0 的 Banana Pi K1,也只能达到 SG2044 性能的 35%-50%。

大幅超越SG2042(多核是关键)

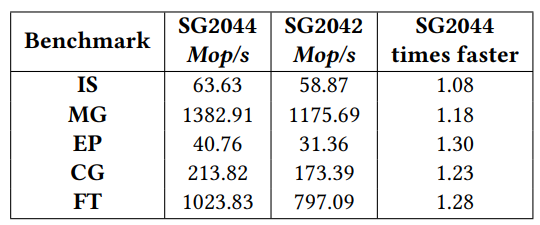

1. 单核心:提升有限,计算密集型更受益

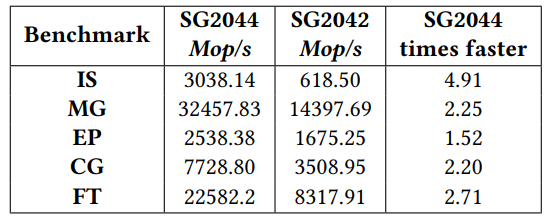

单核下,SG2044 最多只比 SG2042 快 30%(EP 基准),内存敏感型任务提升微弱——这说明 SG2044 的升级重点不在“单核”,而在“多核”。2. 64 核:内存敏感型任务直接起飞

在内存延迟敏感型的 IS(整数排序)基准中,SG2044 64 核性能达 3038.14 Mop/s,而 SG2042 为 618.50 Mop/s,前者是后者的 4.91 倍,大幅提升了 SG2042 在多核心下性能;即便是对计算效率要求极高的FT(快速傅里叶变换)基准,SG2044 64 核性能也达 22582.2 Mop/s,较 SG2042 的 8317.91 Mop/s 提升 2.71 倍。

对标 x86/ARM:64 核满负载,RISC-V实现性能突破

过去,RISC-V HPC 芯片面对 x86、ARM 总是 “单核心差距大,多核心追不上”,但 SG2044 用实测数据打破了这一局面。

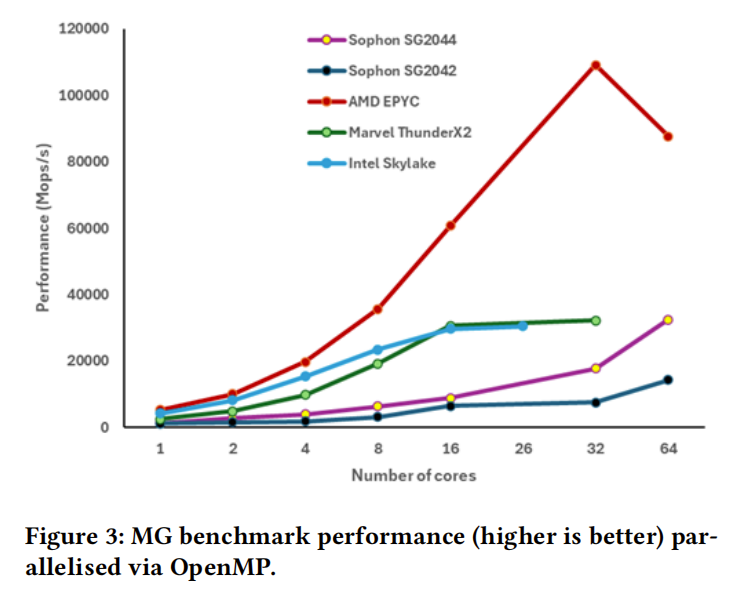

通过与 HPC 领域主流芯片的对比(AMD EPYC 7742、Intel Xeon Platinum 8170、Marvell ThunderX2): 在MG(内存带宽敏感)基准中,SG2044 64 核性能达 32457.83 Mop/s,虽不及 AMD EPYC 的 10 万级 Mop/s,但已与 26 核 Intel Skylake(约 3 万 Mop/s)、32 核 Marvell ThunderX2(约 2.8 万 Mop/s)基本持平,远超 SG2042 的 14397.69 Mop/s;

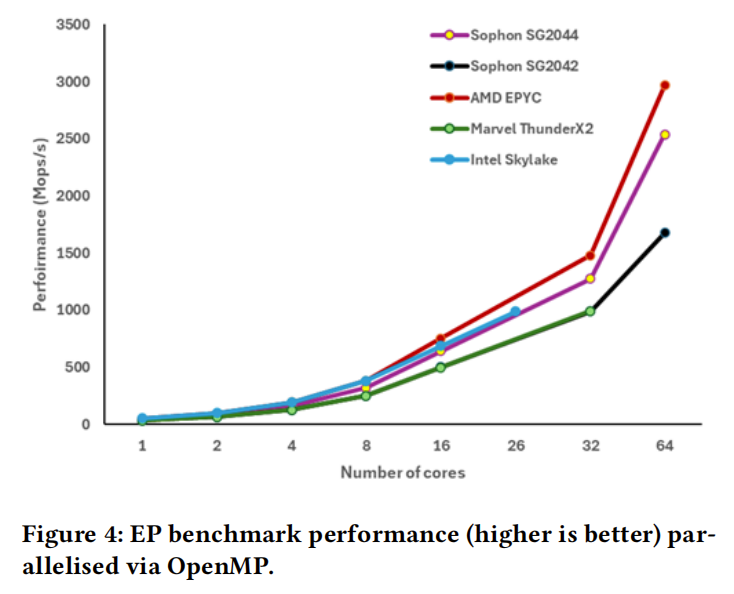

在EP(纯计算)基准中,SG2044 单核心性能与 Intel Skylake 差距仅 30%,64 核时性能达 2538.38 Mop/s,较 SG2042 提升 52%,且核心数超过 26 核后,性能曲线与 AMD EPYC 基本平行,展现出优秀的多核扩展性;

即便是复杂的BT/LU/SP 伪应用(模拟真实 HPC 流体力学、数值模拟场景),SG2044 在 64 核时也实现了对 SG2042 的 2 倍以上性能提升,其中 BT 基准性能是 SG2042 的 2.22 倍,SP 基准是 2.08 倍。

更值得关注的是,SG2044 的定位是“ 服务器级处理器”,而非顶级超算芯片,但在价格更低、功耗更优的前提下,能在 64 核满负载场景下追平入门级 x86/ARM HPC 芯片,已足以证明 RISC-V 在 HPC 领域的性价比优势。

RISC-V 架构的发展为处理器领域带来了新的活力,算能 SG2044 的意义不仅是一款高性能芯片,更在于它验证了 RISC-V 的技术潜力 —— 通过解决“向量计算兼容性” 和 “内存带宽”两大核心痛点,RISC-V 终于能从嵌入式领域走向 HPC 这一 “高端战场”。

-

嵌入式

+关注

关注

5209文章

20677浏览量

337187 -

HPC

+关注

关注

0文章

350浏览量

25077 -

RISC-V

+关注

关注

49文章

2952浏览量

53565

发布评论请先 登录

OrangePi RV2 深度技术评测:RISC-V AI融合架构的先行者

RISC-V不支持 Nx吗?

探索RISC-V在机器人领域的潜力

强强联手!爱丁堡大学与算能破局:RISC-V进军高性能计算,SG2044多核性能飙涨近5倍

【Milk-V Duo S 开发板免费体验】RISC-V核心NCNN基准测试

【Milk-V Duo S 开发板免费体验】RISC-V核性能测试

全球Silicon 100:中国高性能RISC-V力量强势入围

2025新思科技RISC-V科技日活动圆满结束

时擎科技亮相2025 RISC-V中国峰会,深度解析高性能RISC-V SoC技术挑战与创新

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

RISC-V 发展态势与红帽系统适配进展

孟建熠:攀登 RISC-V 高性能高峰,打造标杆产品

RISC-V International CEO:RISC-V 应用全面开花,2031 年渗透率将达 25.7%

匠芯创D133CBS RISC-V KunLun Pi V1.0开发板开发资料

ROCm 6.2.4 成功移植至 SG2044: 大模型部署速率飙升,RISC-V + AI 新纪元!代码已经开源,一起来试试!

RISC-V HPC新标杆Sophon SG2044深度评估:支持RVV v1.0适配GCC 15.2,多核性能潜力巨大!

RISC-V HPC新标杆Sophon SG2044深度评估:支持RVV v1.0适配GCC 15.2,多核性能潜力巨大!

评论