JTAG链

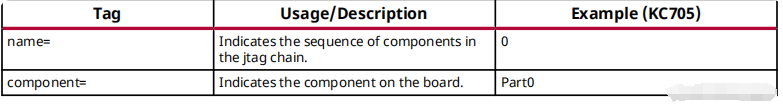

这列出了定义板上可用的不同JTAG链。每个链都列在下面

<jtag_chain>标记指定具有name=属性的链的名称。

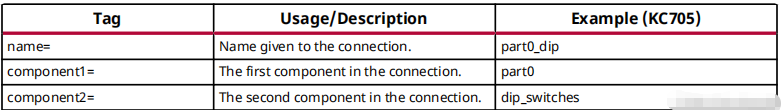

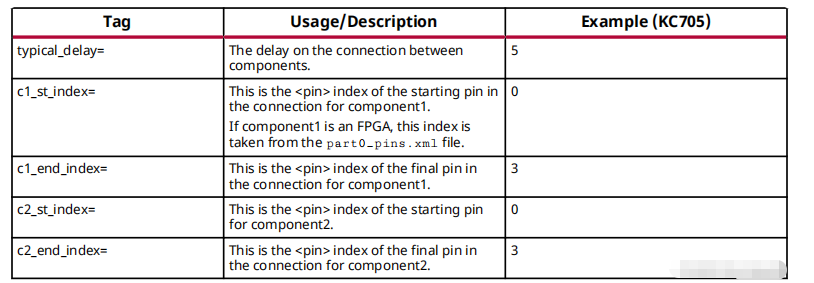

连接

c1_end_index="3" c2_st_index="0" c2_end_index="3"/>

<connection>可以具有以下属性:

IP关联规则

提示:

ip_interface="mgt_clk">

ip_interface="phy_rst_n">

version="*"

ip_interface="gtrefclk_in">

IP关联规则

重要!目前只支持一个名为“default”的规则,因此只能有一对

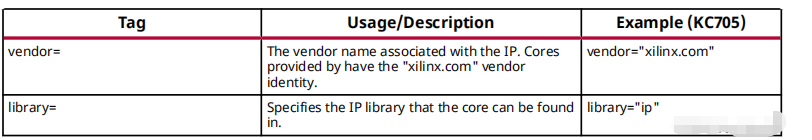

IP

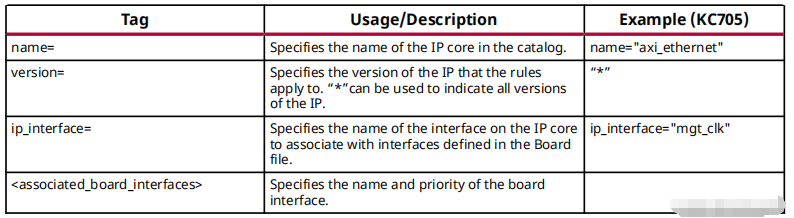

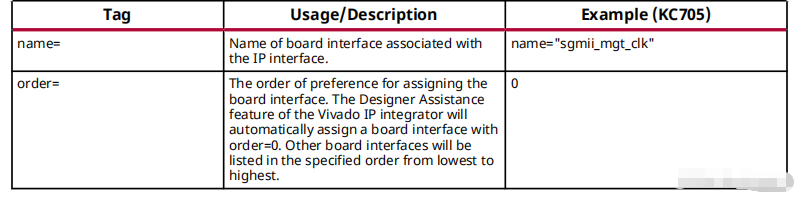

<ip>标记定义了相关规则所应用的ip和接口。<ip>标签标识IP的供应商、库、名称和版本(VLNV),以及上的特定接口IP。

ip_interface="mgt_clk">

提示:

-

接口

+关注

关注

33文章

9623浏览量

157726 -

JTAG

+关注

关注

6文章

417浏览量

75315 -

Vivado

+关注

关注

19文章

860浏览量

71462

原文标题:vivado JTAG链、连接、IP关联规则

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

构建多电压JTAG链的技巧

连接到目标上的远程jtag硬件服务器时无法连接Vivado 2015.3的原因?

如何调试JTAG链与非xilinx器件?

基于回收技术的关联规则研究

基于用户兴趣导向的关联规则数据挖掘

基于Vivado将verilog代码封装成IP的步骤

两种关联规则挖掘算法的介绍及其主要步骤的分析

关联规则推荐算法分析及评估

基于MapReduce的并行关联规则挖掘算法

vivado JTAG链、连接、IP关联规则介绍

vivado JTAG链、连接、IP关联规则介绍

评论