第一章********核心板简介

[]()1.1产品简介

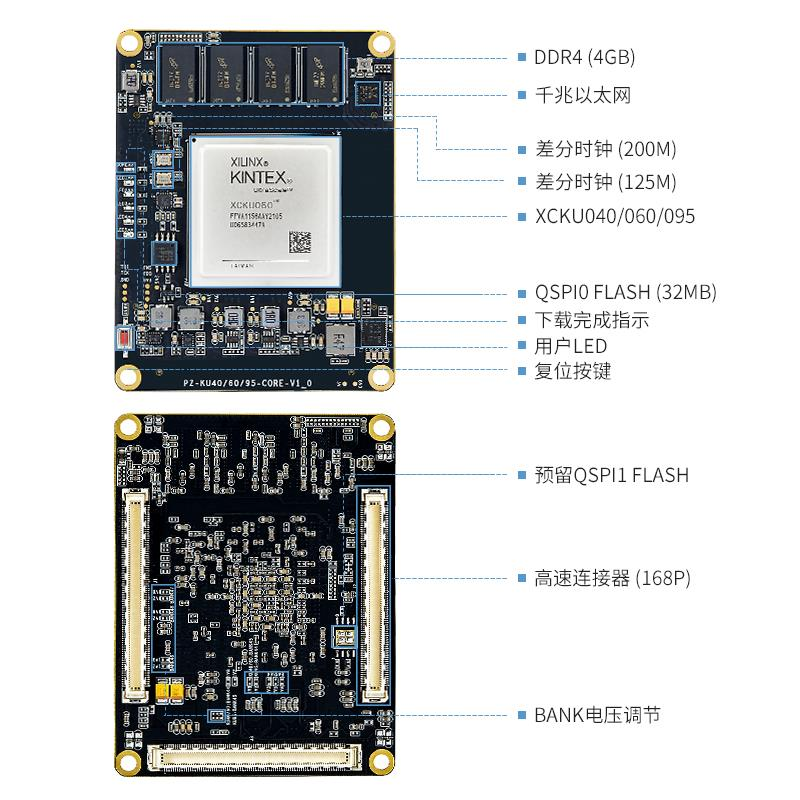

PZ-KU40/60/95 核心板采用 XILINX 公司 KintexUltraScale 系列 的 XCKU040-2FFVA1156I/XCKU060-2FFVA1156I/XCKU095-2FFVA1156I 作为主控制器,核心板采用 3 个 0.5mm 间距 168P 高速连接器与母板 连接,核心板四个脚放置了 4 个 3.5mm 固定孔,此孔可以与底板通过 螺丝紧固,确保了在强烈震动的环境下稳定运行。

KU 系列核心板做了长时间的高低温测试,指标均达到工业级标 准,满足-40—85℃场景应用。

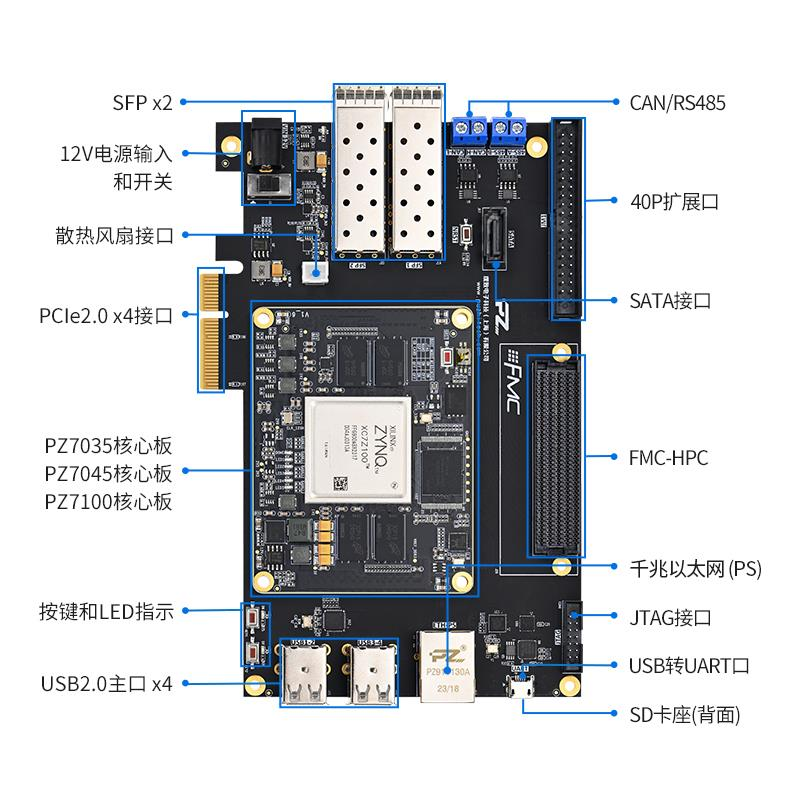

另外,与 KU 系列核心板配套的开发板,我们提供了丰富的外设 接口以及详细的例程源码,大大缩短了用户的学习时间加快产品上市。

[]()1.2********产品规格

如下表列出了 KU 系列核心板对应的参数以及外设指标

| 璞致 Kintex Ultrascale 040/060/095 核心板规格 |

|---|

| 主控制器 |

| Logic Cells(K) |

| LUT |

| Flip-Flops |

| BLOCK ROM |

| DSP Slices |

| DDR4 |

| QSPI FLASH |

| 启动方式 |

| 千兆以太网 |

| 用户 LED |

| 复位按键 |

| GTH 接口 |

| 扩展 IO 数量 |

| 工作电压/最大电流 |

| 核心板尺寸、工艺 |

| 与底板扣接高度 |

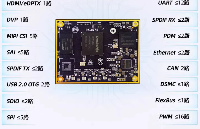

[]()1.3********产品外观

如下图标注出了 KU 系列核心板的正反面器件所在位置,方便用户 查看。

编辑

[]()1.4********产品尺寸

核心板长宽尺寸为83.8x64.8mm,对于高度我们做详细说明,方 便用户在定制外壳时候有所参考。核心板和底板的连接器合高为 4mm, 核心板 PCB 的厚度是 1.75mm,核心板正面器件最大高度为 3.5mm。对 于使用我们定制散热片的用户,还要考虑散热片的高度,散热片厚度 7mm、散热片与核心板之间的支撑柱高 5mm。

如下图为核心板的尺寸标注。

编辑

[]()[]()第二章********核心板使用说明

[]()2.1********核心板供电

核心板供电电压是 5V,在核心板的对角留有电源输入管脚,电源 管脚在模块内部已做了连通,此设计是为了方便底板的电源接入,设 计底板时只需要连接一个角上的电源,核心板即可工作。电源连接需 用铜皮连接且打足够的过孔保证电源通流能力。核心板上的所有 GND 信号都需要连接到底板上,每个 GND 通过两个过孔与底板连接以确保 通流能力。核心板的极限电流在 5V/6A,所以外部供电需要考虑极限 电流情况以保证核心板工作稳定。

给模组供电的电源输出电压需稳定,在模组电源输入加一级DCDC 电源转换,从高电压转到 5V,DCDC 电流输出能力可以选 6A 左右,如 电源芯片 TPS56628DDAR 可以参考。在模组电源输入处需放置 2 颗 220uF/10V 电容保证电源质量。

编辑

[]()2.2********核心板时钟

核心板上放置了两颗有源差分晶振,200M 时钟为逻辑侧提供差 分时钟,125M 为 GTX 接口提供差分时钟。如下图,200M 差分时钟接 入 KU40/60 的 BANK67 或者 KU95 的 BANK68 的 12P/12N 管脚,对应的 管脚位置为 D24/C24,125M 时钟做了 BUF 转换成三路分别给到 BANK225/226/227 的 Y6/Y5、T6/T5、M6/M5 位置。

[]()2.3********核心板复位

核心板预留了一个复位按键,用于调试使用,此复位按键采用 RC 电路,复位并不充分,只作为调试使用,按键与 FPGA 的 BANK65连接, 对应管脚为 IO_13P_65(K26)。实际产品需要加复位电路,可以在底板 上采用专用复位芯片,如 MAX811,或者其他复位时间更长的芯片。

编辑

[]()2.4********核心板启动方式

核心板支持两种启动模式,分别是 JTAG、QSPI Flash。默认为 QSPI Flash 启动。

[]()2.5********网口连接

核心板上放置了一颗千兆以太网芯片RTL8211FI-CG,以太网芯片 与 FPGA 芯片之间通过 RGMII 接口互联,接口电平 3.3V,连接对应管 脚见下表,以太网对外连接只需要一个带变压器的 RJ45 即可使用,

芯片地址 PHY_AD[2:0]=001,复位管脚为低有效。设计原理图可参考

开发板图纸(产品电路需加 ESD 保护电路)。

| RMGII 信号 | 管脚名称 | 管脚位置 |

|---|---|---|

| TX_CLK | IO_14P_MRCC_65 | P24 |

| TXD0 | IO_15P_65 | T27 |

| TXD1 | IO_15N_65 | R27 |

| TXD2 | IO_16P_65 | T24 |

| TXD3 | IO_16N_65 | T25 |

| TX_EN | IO_17P_65 | R25 |

| RX_CLK | IO_13P_MRCC_65 | P26 |

| RXD0 | IO_17N_65 | R26 |

| RXD1 | IO_18P_65 | R23 |

| RXD2 | IO_18N_65 | P23 |

| RXD3 | IO_19P_65 | N22 |

| RX_CTL | IO_19N_65 | M22 |

| PHY_nRST | IO_13N_SRCC_65 | N26 |

| MDC | IO_20P_65 | P20 |

| MDIO | IO_20N_65 | P21 |

[]()2.6QSPIFLASH

单板上设计了两路 QSPI FLASH,默认贴片 QSPI0,QSPI1 不贴, X4 工作模式,容量为 32MB,型号为[MX25L25645GM2I-08G],用于存储 启动文件或者用户文件。如下表为两路 QSPI 的管脚位置。

| QSPI0FLASH引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DATA0 | D00_MOSI | AC7 |

| DATA1 | D01_DIN | AB7 |

| DATA2 | D02 | AA7 |

| DATA3 | D03 | Y7 |

| QSPI_CS | RDWR_FCS_B | U7 |

| QSPI_CLK | CCLK | AA9 |

| QSPI1FLASH引脚 | 管脚名称 | 管脚位置 |

| DATA0 | IO_L22P_65 | M20 |

| DATA1 | IO_L22N_65 | L20 |

| DATA2 | IO_L21P_65 | R21 |

| DATA3 | IO_L21N_65 | R22 |

| QSPI_CS | IO_L2N_65 | G26 |

| QSPI_CLK | CCLK | AA9 |

编辑

8 / 14

璞写当下 致远未来 [www.puzhitech.com]

[]()2.7板载LED

为方便调试,核心板上放置了五颗 LED,LED 的管脚位置如下表, 当管脚输出高电平时 LED 点亮,低电平 LED 灭。

| 序号 | 管脚名称 | 管脚位置 |

|---|---|---|

| LED1 | IO_T0U_65 | H23 |

| LED2 | IO_T2U_65 | N27 |

| LED3 | IO_L23P_65 | N21 |

| LED4 | IO_L23N_65 | M21 |

| LED5 | IO_L2P_65 | G25 |

[]()2.8BANK接口电平选择

核心板上对外的BANK 分别为BANK44/45/46/47/48/64,这些BANK 的 IO 均可独立调节电压。其中 BANK44/45/46/47/48 支持 1.2V/1.8V 两种电平调节,默认电平为 1.8V。BANK64 支持 1.8V/2.5V/3.3V 三种 电平调节,默认电平为 3.3V,如果需要更改电平,只需要更换对应位 置电阻即可实现调整,如 3.3V 电平的改成 1.8V 的,只需要把 3.3V 位 置的电阻改到 1.8V 位置即可。核心板上都有标注 BANK 电平调节电阻 位置,如下图。

编辑

[]()2.9DDR4********管脚连接

核心板配置了四颗工业级DDR4 芯片,单颗容量 1GB,四颗共计容 量为 4GB,型号为 MT40A512M16LY-062E IT:E,DDR4 管脚分配参见下 表。

| DDR4********引脚 | 管脚名称 | 管脚位置 |

|---|---|---|

| DDR4_D0 | IO-L6N-66 | D10 |

| DDR4_D1 | IO-L3N-66 | C8 |

| DDR4_D2 | IO-L5P-66 | D9 |

| DDR4_D3 | IO-L5N-66 | C9 |

| DDR4_D4 | IO-L6P-66 | E10 |

| DDR4_D5 | IO-L3P-66 | D8 |

| DDR4_D6 | IO-L2N-66 | A9 |

| DDR4_D7 | IO-L2P-66 | B9 |

| DDR4_DM0 | IO-L1P-66 | F8 |

| DDR4_DQS_P0 | IO-L4P-66 | B10 |

|---|---|---|

| DDR4_DQS_N0 | IO-L4N-66 | A10 |

| DDR4_D8 | IO-L12P-66 | G10 |

| DDR4_D9 | IO-L9P-66 | J8 |

| DDR4_D10 | IO-L11N-66 | F9 |

| DDR4_D11 | IO-L9N-66 | H8 |

| DDR4_D12 | IO-L12N-66 | F10 |

| DDR4_D13 | IO-L8P-66 | J9 |

| DDR4_D14 | IO-L11P-66 | G9 |

| DDR4_D15 | IO-L8N-66 | H9 |

| DDR4_DM1 | IO-L7P-66 | L8 |

| DDR4_DQS_P1 | IO-L10P-66 | K10 |

| DDR4_DQS_N1 | IO-L10N-66 | J10 |

| DDR4_D16 | IO-L14P-66 | H12 |

| DDR4_D17 | IO-L17N-66 | K12 |

| DDR4_D18 | IO-L14N-66 | G12 |

| DDR4_D19 | IO-L15P-66 | K11 |

| DDR4_D20 | IO-L18N-66 | H13 |

| DDR4_D21 | IO-L17P-66 | L12 |

| DDR4_D22 | IO-L18P-66 | J13 |

| DDR4_D23 | IO-L15N-66 | J11 |

| DDR4_DM2 | IO-L13P-66 | H11 |

| DDR4_DQS_P2 | IO-L16P-66 | L13 |

| DDR4_DQS_N2 | IO-L16N-66 | K13 |

| DDR4_D24 | IO-L23P-66 | A13 |

| DDR4_D25 | IO-L21P-66 | C11 |

| DDR4_D26 | IO-L24N-66 | C13 |

| DDR4_D27 | IO-L21N-66 | B11 |

| DDR4_D28 | IO-L24P-66 | D13 |

| DDR4_D29 | IO-L20P-66 | C12 |

| DDR4_D30 | IO-L20N-66 | B12 |

| DDR4_D31 | IO-L23N-66 | A12 |

| DDR4_DM3 | IO-L19P-66 | E11 |

| DDR4_DQS_P3 | IO-L22P-66 | F13 |

| DDR4_DQS_N3 | IO-L22N-66 | E13 |

| DDR4_D32 | IO-L2P-68 | A19 |

| DDR4_D33 | IO-L5N-68 | B16 |

| DDR4_D34 | IO-L6P-68 | C18 |

| DDR4_D35 | IO-L5P-68 | B17 |

| DDR4_D36 | IO-L2N-68 | A18 |

| DDR4_D37 | IO-L3P-68 | B15 |

| DDR4_D38 | IO-L6N-68 | C17 |

| DDR4_D39 | IO-L3N-68 | A15 |

|---|---|---|

| DDR4_DM4 | IO-L1P-68 | B14 |

| DDR4_DQS_P4 | IO-L4P-68 | C19 |

| DDR4_DQS_N4 | IO-L4N-68 | B19 |

| DDR4_D40 | IO-L12P-68 | E18 |

| DDR4_D41 | IO-L8P-68 | E15 |

| DDR4_D42 | IO-L11P-68 | E16 |

| DDR4_D43 | IO-L9P-68 | F15 |

| DDR4_D44 | IO-L12N-68 | E17 |

| DDR4_D45 | IO-L8N-68 | D15 |

| DDR4_D46 | IO-L11N-68 | D16 |

| DDR4_D47 | IO-L9N-68 | F14 |

| DDR4_DM5 | IO-L7P-68 | D14 |

| DDR4_DQS_P5 | IO-L10P-68 | D19 |

| DDR4_DQS_N5 | IO-L10N-68 | D18 |

| DDR4_D48 | IO-L18N-68 | H18 |

| DDR4_D49 | IO-L17N-68 | H16 |

| DDR4_D50 | IO-L17P-68 | H17 |

| DDR4_D51 | IO-L15P-68 | G15 |

| DDR4_D52 | IO-L18P-68 | H19 |

| DDR4_D53 | IO-L14N-68 | F17 |

| DDR4_D54 | IO-L14P-68 | F18 |

| DDR4_D55 | IO-L15N-68 | G14 |

| DDR4_DM6 | IO-L13P-68 | G17 |

| DDR4_DQS_P6 | IO-L16P-68 | G19 |

| DDR4_DQS_N6 | IO-L16N-68 | F19 |

| DDR4_D56 | IO-L24P-68 | L19 |

| DDR4_D57 | IO-L21N-68 | K15 |

| DDR4_D58 | IO-L24N-68 | L18 |

| DDR4_D59 | IO-L20N-68 | K17 |

| DDR4_D60 | IO-L20P-68 | K18 |

| DDR4_D61 | IO-L23N-68 | J16 |

| DDR4_D62 | IO-L23P-68 | K16 |

| DDR4_D63 | IO-L21P-68 | L15 |

| DDR4_DM7 | IO-L19P-68 | J15 |

| DDR4_DQS_P7 | IO-L22P-68 | J19 |

| DDR4_DQS_N7 | IO-L22N-68 | J18 |

| DDR4_A0 | IO-L16N-67 | C22 |

| DDR4_A1 | IO-L19P-67 | G24 |

| DDR4_A2 | IO-L3N-67 | D29 |

| DDR4_A3 | IO-L6N-67 | A28 |

| DDR4_A4 | IO-L14P-67 | E22 |

| DDR4_A5 | IO-L4N-67 | A29 |

|---|---|---|

| DDR4_A6 | IO-L17N-67 | A20 |

| DDR4_A7 | IO-L6P-67 | A27 |

| DDR4_A8 | IO-L21P-67 | F23 |

| DDR4_A9 | IO-L5P-67 | D28 |

| DDR4_A10 | IO-L17P-67 | B20 |

| DDR4_A11 | IO-L18N-67 | D21 |

| DDR4_A12 | IO-L7P-67 | E26 |

| DDR4_A13 | IO-L3P-67 | E28 |

| DDR4_A14 | IO-L20N-67 | E21 |

| DDR4_A15 | IO-L21N-67 | F24 |

| DDR4_A16 | IO-L22P-67 | G20 |

| DDR4_BA0 | IO-L20P-67 | E20 |

| DDR4_BA1 | IO-L19N-67 | F25 |

| DDR4_BG0 | IO-L15P-67 | B21 |

| DDR4_nCS | IO-L14N-67 | E23 |

| DDR4_ODT | IO-L18P-67 | D20 |

| DDR4_RESET | IO-L4P-67 | B29 |

| DDR4_CLK_P | IO-L13P-67 | D23 |

| DDR4_CLK_N | IO-L13N-67 | C23 |

| DDR4_CKE | IO-L16P-67 | C21 |

| DDR4_TEN | IO-L9N-67 | B26 |

| DDR4_nACT | IO-L8N-67 | A25 |

| DDR4_nALERT | IO-L9P-67 | C26 |

| DDR4_PARITY | IO-L8P-67 | B25 |

[]()[]()第三章********底板设计注意事项

[]()3.1电源部分PCB********设计

电源输入需要铺铜皮连接,打足够的过孔保证通电流能力,但电 源电压较高,干扰较大,在保证通流的条件下不要让这个铜皮更大, 以免干扰其他信号。地管脚需要连接到地平面上,且一个地管脚需要 打两个过孔,保证通流和充分连接。

编辑

[]()3.2********高速接口布局走线

1)千兆以太网:

与 RJ45 端连接的信号需要保持等长,RGMII 接口的 TX 部分与 RX 部分需要单独保持等长。

2)HDMI 接口

HDMI 接口信号需要走差分,且差分之间需保持等长控制。

- 其他高速接口

依据接口规范控制。

[]()3.3LVDS信号

HR BANK 电平可以在 1.8V/2.5V/3.3V 三种电平之间选择,默认 为 3.3V 电平,如果需要工作在 LVDS 模式下,需要把接口电平调整为 1.8V 或者 2.5V。HP BANK 电平可以在 1.2V/1.8V 两种电平之间选择, 默认为 1.8V 电平。核心板上 P/N 对已按差分走线处理,底板如果使 用 P/N 对,信号走线需做差分/阻抗控制处理,并且差分之间保持等 长。

[]()3.4GTX信号走线

GTX 走线需要考虑的问题比较多,对于有疑问的用户可以联系客 服接入技术支持。

[]()3.5********产品防护

对于产品设计,需要在各类接口加上防护电路。需按防护等级需 求进行设计。

[]()[]()第四章********核心板管脚与信号等长

[]()4.1********核心板管脚定义

KU 系列核心板管脚定义我们单独提供了说明文档。详细的管脚 定义参见文件夹《璞致 KintexUltraScale 系列核心板之 KU040- KU060-KU095 管脚与等长》。

[]()4.2********信号等长

为方便用户设计底板以及信号走高速,我们提供了 J1-J3 连接 器上的走线长度数据,方便用户协同底板设计。详细数据表格参见文 件夹《璞致 KintexUltraScale 系列核心板之 KU040-KU060-KU095 管 脚与等长》

审核编辑 黄宇

-

FPGA

+关注

关注

1655文章

22287浏览量

630326 -

开发板

+关注

关注

25文章

6125浏览量

113384 -

核心板

+关注

关注

6文章

1344浏览量

31760

发布评论请先 登录

高效项目的“核心”秘诀:怎么选对核心板?

fpga开发板 璞致 Kintex UltraScale Plus PZ-KU3P 与 PZ-KU5P核心板与开发板用户手册

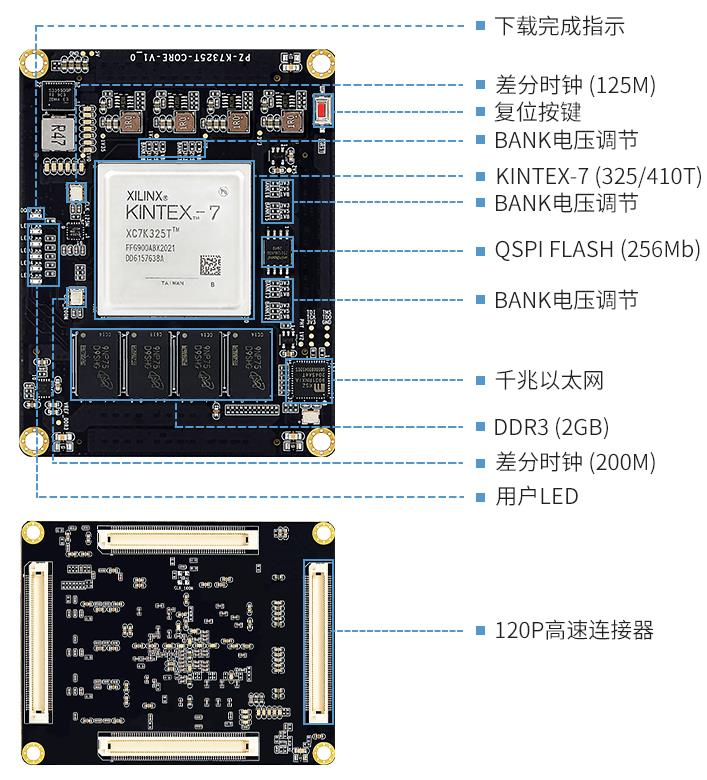

FPGA开发板—璞致 Kintex-7 系列核心板PZ-K7325T/PZ-K7410T 使用说明 XILINX核心板简介

fpga开发板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板与开发板用户手册

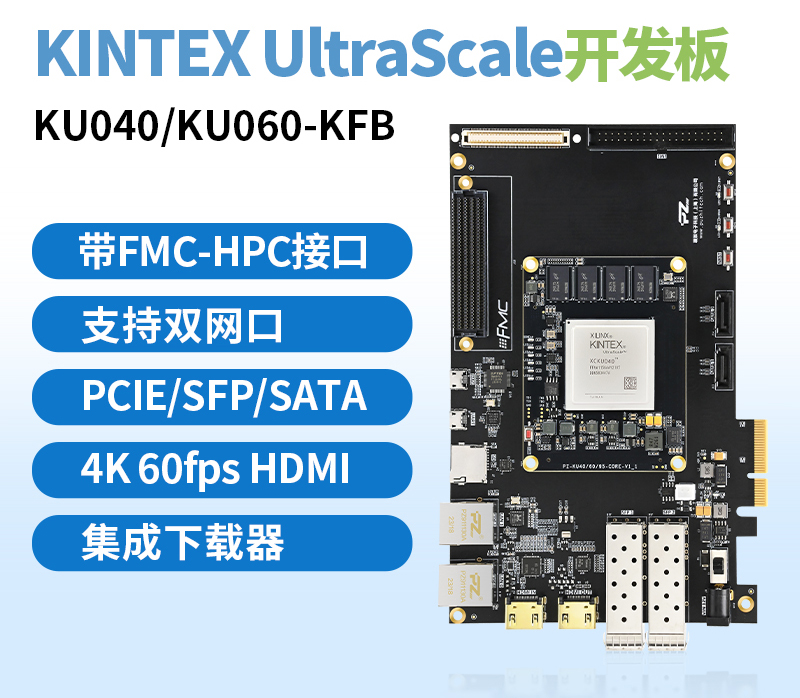

Kintex UltraScale 纯 FPGA 开发平台,释放高速并行计算潜能,高性价比的 FPGA 解决方案

核心板的多领域应用与前景分析

从入门级到旗舰款,全志T系列核心板怎么选?

正点原子AU15开发板资料发布!板载40G QSFP、PCIe3.0x8和FMC LPC等接口,性能强悍!

PET_RK3588_CORE核心板

为什么要选择BGA核心板?

FPGA开发板—璞致 Kintex UltraScale+ 系列核心板 KU040/KU060/KU095 使用说明 XILINX核心板简介

FPGA开发板—璞致 Kintex UltraScale+ 系列核心板 KU040/KU060/KU095 使用说明 XILINX核心板简介

评论