这款 28 位 1:2 可配置寄存器缓冲器设计用于 1.7V 至 1.9V VCC操作。每个 DIMM 需要一个设备来驱动多达 18 个堆叠的 SDRAM 负载,或者每个 DIMM 需要两个设备来驱动多达 36 个堆叠的 SDRAM 负载。

除芯片选择栅极使能 (CSGEN)、控制 (C) 和复位 (RESET) 输入外,所有输入均SSTL_18。 它们是 LVCMOS。所有输出都是边沿控制电路,针对未端接的DIMM负载进行了优化,符合SSTL_18规格,但漏极开路误差(QERR)输出除外。

*附件:74sstub32868a.pdf

74SSTUB32868A 采用差分时钟(CLK 和 CLK)工作。数据在 CLK 走高和 CLK 走低的交叉点上记录。

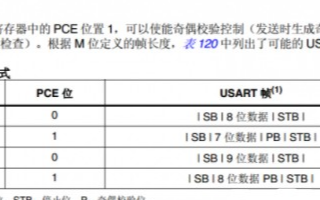

74SSTUB32868A 在奇偶校验位 (PAR_IN) 输入端接受来自存储器控制器的奇偶校验位,将其与独立于 DIMM 的 D 输入(C = 0 时为 D1-D5、D7、D9-D12、D17-D28;C = 1 时为 D1-D12、D17-D20、D22、D24-D28)上接收到的数据进行比较,并指示在 漏极开路 QERR 引脚(低电平有效)。公约是平等的;也就是说,有效奇偶校验定义为 与 DIMM 无关的数据输入与奇偶校验输入位相结合的 1 个数。要计算奇偶校验,所有与 DIMM 无关的 D 输入都必须连接到已知的逻辑状态。

74SSTUB32868A 包括奇偶校验功能。奇偶校验在应用到的数据输入后一个周期到达,在设备的PAR_IN输入上进行检查。数据注册后两个时钟周期,生成相应的 QERR 信号。

如果发生错误并且 QERR 输出被驱动为低电平,则它将保持低电平锁存至少两个时钟周期或 直到RESET被驱动为低电平。如果发生两个或多个连续奇偶校验错误,则QERR输出被驱动为低电平并锁存为低电平,时钟持续时间等于奇偶校验错误持续时间,或者直到RESET被驱动为低电平。如果在器件进入低功耗模式(LPM)之前,时钟周期上发生奇偶校验错误,并且QERR输出被驱动为低电平,则在LPM持续时间加上两个时钟周期内或直到RESET被驱动为低电平。与 DIMM 相关的信号(DCKE0、DCKE1、DODT0、DODT1、DCS0 和 DCS1)不包括在奇偶校验计算中。

C输入控制从寄存器A配置(低电平时)到寄存器B配置(高电平时)的引脚配置。正常工作期间不应切换 C 输入。它应该硬连线到有效的低电平或高电平,以将寄存器配置为所需模式。

在DDR2 RDIMM应用中,RESET被指定为相对于CLK和CLK完全异步的 时钟。因此,无法保证两者之间的时间关系。进入复位时,寄存器被清除,数据输出相对于禁用差分输入接收器的时间快速驱动为低电平。然而,当复位出来时,寄存器相对于时间迅速激活 启用差分输入接收器。只要数据输入为低电平,并且时钟在从RESET从低到高转换到输入接收器完全使能期间保持稳定,74SSTUB32868A的设计就必须确保输出保持低电平,从而确保输出上没有毛刺。

为确保在提供稳定时钟之前从寄存器获得定义的输出,在上电期间必须将RESET保持在低电平状态。

该器件支持低功耗待机作。当RESET为低电平时,差分输入接收器为: 禁用和未驱动(浮动)数据、时钟和基准电压 (V 裁判 ) 输入。此外,当RESET为低电平时,所有寄存器都被复位,除QERR外,所有输出都强制为低电平。LVCMOS RESET和C输入必须始终保持在有效的逻辑高电平或低电平。

该器件还通过监控系统芯片选择(DCS0和DCS1)和CSGEN输入来支持低功耗有源作,并在CSGEN、DCS0和DCS1输入为高电平时将门控Qn输出的状态变化。如果 CSGEN、DCS0 或 DCS1 输入为低电平,则 Qn 输出工作正常。此外,如果 DCS0 和 DCS1 输入均为高电平,则器件将阻止 QERR 输出发生状态变化。如果 DCS0 或 DCS1 为低电平,则 QERR 输出正常工作。RESET输入优先于DCS0和DCS1控制,当驱动低电平时,Qn输出为低电平,QERR输出为高电平。如果芯片选择控制 不需要功能,则CSGEN输入可以硬接线到地,在这种情况下,DCS0和DCS1的建立时间要求将与其他D数据输入相同。控制低功耗 模式,则 CSGEN 输入应上拉至 VCC通过上拉电阻器。

两个V裁判引脚(A5 和 AB5)在内部连接在一起大约 150 个。但是,只需连接两个 V 中的一个裁判引脚连接到外部V裁判电源。未使用的 V裁判引脚应以 V 结尾裁判耦合电容器。

特性

- 德州仪器 (TI) Widebus+ ™ 系列成员

- 引脚排列优化了 DDR2 DIMM PCB 布局

- 1 对 2 输出支持堆叠式 DDR2 DIMM

- 每个 DIMM 需要一个设备

- 芯片选择输入可控制数据输出的状态变化,并最大限度地降低系统功耗

- 输出边沿控制电路可最大限度地降低未端接线路中的开关噪声

- 支持SSTL_18数据输入

- 差分时钟(CLK和CLK)输入

- 支持芯片选择栅极使能、控制和RESET输入上的LVCMOS开关电平

- 检查与 DIMM 无关的数据输入上的奇偶校验

- 支持工业温度范围(-40°C 至 85°C)

- 重置输入禁用差分输入接收器,复位所有寄存器,并强制所有输出为低电平,QERR除外

- 应用

- 重载 DDR2 寄存器 DIMM

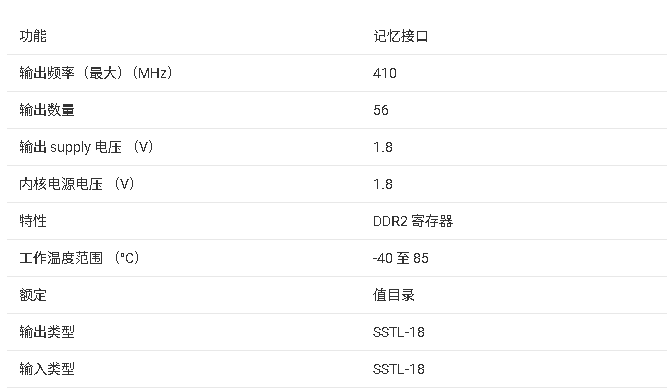

参数

1. 核心功能特性

- Widebus+™家族成员:属于TI高速总线产品线,支持DDR2 DIMM PCB布局优化

- 配置灵活性:提供1:2输出配置,可驱动18个堆叠SDRAM负载(单DIMM)或36个负载(双DIMM)

- 低功耗设计:通过芯片选择输入门控数据输出状态,降低系统功耗

- 噪声控制:输出边缘控制电路减少未端接线路的开关噪声

- 工业级温度支持:工作温度范围-40°C至85°C

2. 关键应用场景

- 高负载DDR2寄存型DIMM

- 需要地址奇偶校验的服务器内存模块

3. 技术细节

- 电压支持:1.7V至1.9V VCC操作电压

- 输入/输出标准:

- 数据输入:SSTL_18电平

- 控制输入(RESET/CSGEN/C):LVCMOS电平

- 奇偶校验机制:

- 支持DIMM独立数据输入的奇偶校验(偶校验规则)

- 错误信号(QERR)在数据注册后2个时钟周期生成

- 可检测连续错误并保持锁定状态直至复位

4. 封装与订购信息

5. 时序特性

- 最大时钟频率:410MHz

- 建立/保持时间:数据输入相对CLK需满足500ps时序要求

- 传播延迟:CLK到Q输出典型值1.1ns(最大1.6ns)

6. 特殊功能模式

- 低功耗模式:通过RESET控制可禁用差分接收器

- 配置选择:C引脚硬连线选择Register-A/B配置模式

- 芯片选择门控:CSGEN信号动态控制数据锁存时机

7. 安全注意事项

该文档完整描述了器件功能、电气特性、时序参数及应用设计要点,适用于高性能内存系统的硬件开发。

-

寄存器

+关注

关注

31文章

5588浏览量

129033 -

缓冲器

+关注

关注

6文章

2215浏览量

48651 -

控制电路

+关注

关注

83文章

1749浏览量

138201 -

DIMM

+关注

关注

0文章

41浏览量

9976 -

LVCMOS

+关注

关注

1文章

142浏览量

11939

发布评论请先 登录

UART中有奇偶校验位和无奇偶校验位的数据传输是怎样的?

DES使用一个56位的密钥以及附加的8位奇偶校验位详细资料说明

单片机串口分析起始位停止位奇偶校验位

什么是奇偶校验 奇偶校验的基本原理 奇偶校验电路什么意思

什么是奇偶校验电路?奇偶校验器是时序逻辑电路吗?

8位到9位奇偶校验总线收发器SN74BCT29854数据表

带奇偶校验器和双3态输出的3.3-V 12位通用总线驱动器SN74ALVCH16903数据表

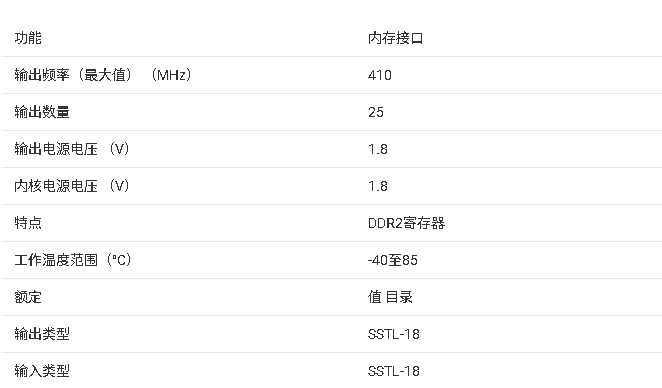

SN74SSTUB32866 25位可配置寄存缓冲器(带地址奇偶校验)技术文档摘要

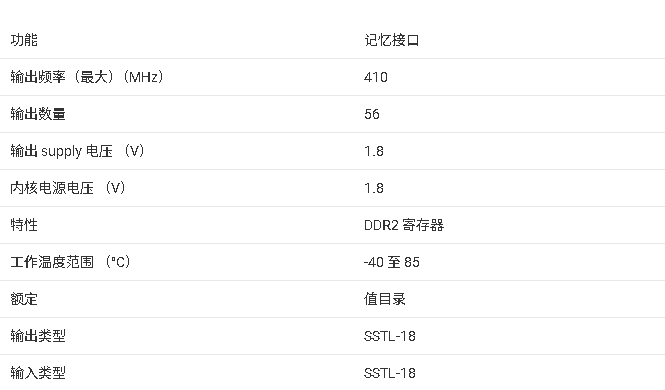

74SSTUB32868 28位至56位带地址奇偶校验的注册缓冲器技术文档总结

74SSTUB32868A 28位至56位带地址奇偶校验的注册缓冲器技术文档总结

74SSTUB32868A 28位至56位带地址奇偶校验的注册缓冲器技术文档总结

评论