CDCLVD1216时钟缓冲器将两个可选时钟输入(IN0、IN1)中的一个分配给16对差分LVDS时钟输出(OUT0、OUT15),时钟分配的偏斜最小。该CDCLVD1216可以接受两个时钟源进入输入多路复用器。输入可以是LVDS、LVPECL或LVCMOS。

*附件:cdclvd1216.pdf

该CDCLVD1216专为驱动 50 Ω输电线路而设计。如果以单端模式驱动输入,则适当的偏置电压 (V AC_REF )应用于未使用的负输入引脚。

IN_SEL引脚选择路由到输出的输入。如果此引脚保持打开状态,则会禁用输出(静态)。该部件支持故障安全功能。它包含输入迟滞,可防止在没有输入信号的情况下输出随机振荡。

该器件在 2.5 V 电源环境中工作,特性为 –40°C 至 85°C(环境温度)。该CDCLVD1216采用小型48引脚、7mm×7mm QFN封装。

特性

- 2:16 差分缓冲器

- 低附加抖动:10 kHz 至 20 MHz 时为

<300 fs RMS - 55 ps(最大值)的低输出偏斜

- 通用输入接受 LVDS、LVPECL、LVCMOS

- 通过控制引脚选择时钟输入

- 16 个 LVDS 输出,兼容 ANSI EIA/TIA-644A 标准

- 时钟频率高达 800 MHz

- 2.375–2.625V 器件电源

- LVDS基准电压,V

AC_REF,可用于电容耦合输入 - 工业温度范围 –40°C 至 85°C

- 封装采用 7mm × 7mm 48 引脚 QFN (RGZ) 封装

- ESD 保护超过 3 kV HBM、1 kV CDM

- 应用

- 电信/网络

- 医学影像

- 测试和测量设备

- 无线通信

- 通用时钟

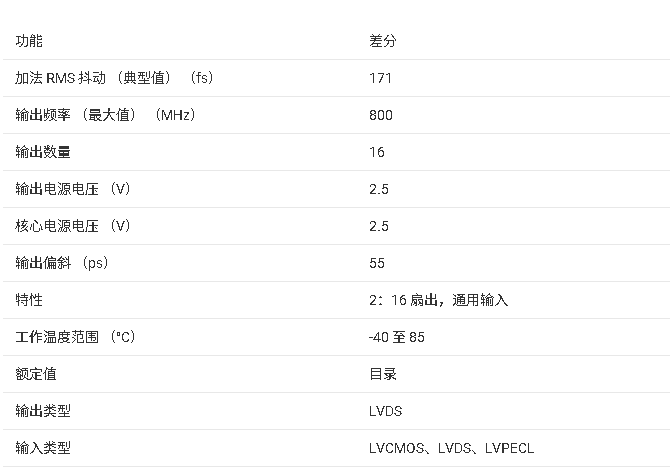

参数

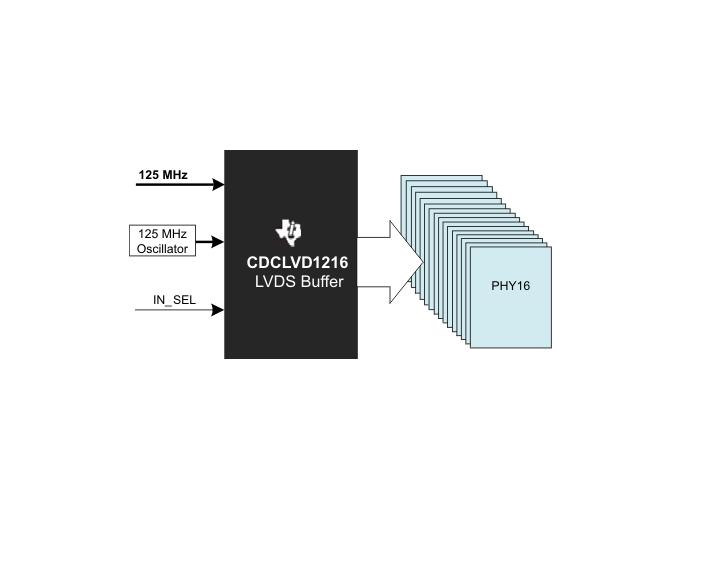

方框图

1. 产品概述

CDCLVD1216是德州仪器(TI)推出的2:16差分时钟缓冲器,专为高性能时钟分配设计。核心特性包括:

- 16路LVDS输出:符合ANSI EIA/TIA-644A标准,支持最高800MHz时钟频率

- 低抖动性能:附加抖动<300 fs RMS(10kHz-20MHz频段)

- 多协议输入:兼容LVDS、LVPECL和LVCMOS信号

- 工业级工作温度:-40°C至85°C

2. 关键参数

- 电源电压:2.375V-2.625V(典型2.5V)

- 输出特性:

- 差分输出电压250-450mV

- 输出偏斜≤55ps(最大值)

- 传播延迟2.5ns(典型值)

- 热特性:48引脚QFN封装(7mm×7mm),结至环境热阻30.6°C/W

3. 功能框图

- 输入选择通过IN_SEL引脚控制(0=IN0,1=IN1,悬空=关闭输出)

- 集成参考电压生成器(VAC_REF)用于容性耦合输入

- 内置200kΩ输入上拉/下拉电阻

4. 典型应用

- 电信/网络设备时钟树

- 医疗成像系统

- 测试测量仪器

- 无线通信基站

- 通用时钟分配场景

5. 设计注意事项

- 热管理:必须将底部散热焊盘接地以优化散热

- 电源滤波:建议每个电源引脚配置0.1μF去耦电容

- 输入配置:

- LVDS输入推荐100Ω端接

- 3.3V LVCMOS需限制摆幅(VIH≤VCC)

- 未用输入建议通过1kΩ电阻接地

- 输出配置:

- LVDS输出需100Ω差分端接

- 交流耦合时建议使用0.1μF电容

6. 可靠性特性

- ESD保护:3kV HBM,1kV CDM

- 绝对最大额定值:电源电压-0.3V至2.8V

文档还包含详细的电气特性表、时序图、封装尺寸及典型应用电路图,适用于高速时钟分配系统的硬件设计参考。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

输电线路

+关注

关注

1文章

814浏览量

24555 -

时钟缓冲器

+关注

关注

2文章

273浏览量

51954 -

lvds

+关注

关注

2文章

1241浏览量

70208 -

多路复用器

+关注

关注

9文章

1065浏览量

66831 -

时钟源

+关注

关注

0文章

112浏览量

16813

发布评论请先 登录

相关推荐

热点推荐

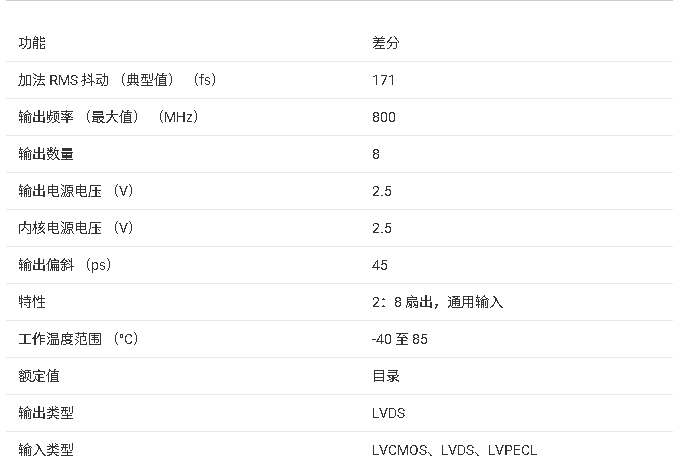

CDCLVD1208 2:8低加性抖动LVDS缓冲器数据表

电子发烧友网站提供《CDCLVD1208 2:8低加性抖动LVDS缓冲器数据表.pdf》资料免费

发表于 08-21 11:15

•0次下载

CDCLVD1212 2:12低加性抖动LVDS缓冲器数据表

电子发烧友网站提供《CDCLVD1212 2:12低加性抖动LVDS缓冲器数据表.pdf》资料免

发表于 08-21 11:16

•0次下载

CDCLVD2108双通道1:8低附加抖动LVDS缓冲器数据表

电子发烧友网站提供《CDCLVD2108双通道1:8低附加抖动LVDS缓冲器数据表.pdf》资料

发表于 08-21 10:50

•0次下载

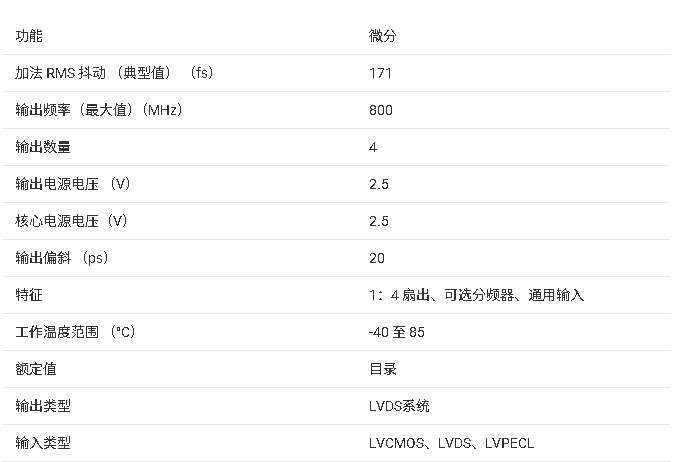

CDCLVD1204 2:4低加性抖动LVDS缓冲器数据表

电子发烧友网站提供《CDCLVD1204 2:4低加性抖动LVDS缓冲器数据表.pdf》资料免费

发表于 08-21 11:10

•0次下载

CDCLVD1208 2:8低附加抖动LVDS缓冲器技术文档总结

CDCLVD1208时钟缓冲器分配两个可选时钟输入(IN0和IN1)之一 8对差分LVDS时钟输出(OUT0至OUT7),时钟偏移最小 分配。该CDCLVD1208可以接受两个时钟源进

探索 CDCLVD1212:低抖动 LVDS 缓冲器的卓越性能与应用指南

——CDCLVD1212,它在众多领域都展现出了非凡的实力。 文件下载: cdclvd1212.pdf 产品概述 CDCLVD1212 是一款 2:12 的

探索CDCLVD1208:低抖动LVDS缓冲器的卓越性能与应用

探索CDCLVD1208:低抖动LVDS缓冲器的卓越性能与应用 在电子设计领域,时钟缓冲器是确保

CDCLVD1216:低抖动LVDS时钟缓冲器的设计与应用

CDCLVD1216:低抖动LVDS时钟缓冲器的设计与应用 在电子设计领域,时钟信号的精准分配至关重要。德州仪器(TI)的

CDCLVD2104:高性能双路1:4低附加抖动LVDS缓冲器解析

CDCLVD2104:高性能双路1:4低附加抖动LVDS缓冲器解析 在电子设计领域,时钟

CDCLVD2106:高性能双路 1:6 低附加抖动 LVDS 时钟缓冲器的深度解析

CDCLVD2106:高性能双路 1:6 低附加抖动 LVDS 时钟缓冲器的深度解析 在电子设计

CDCLVD1213:高性能低抖动LVDS缓冲器的设计与应用

抖动时钟分配方面表现出色,能满足多种应用场景的需求。 文件下载: cdclvd1213.pdf 一、产品概述 CDCLVD1213是一款1:4低附加

CDCLVD1216 2:16低附加抖动LVDS缓冲器技术文档总结

CDCLVD1216 2:16低附加抖动LVDS缓冲器技术文档总结

评论